1 I2C总线的基本概念

I2C总线协议是Philips公司推出的总线协议。它是多主机总线,通过2根线(SDA-aserial data line,SCL-a serial clock line)与连接到总线上的器件之间传送信息,根据地址识别每个器件。例如,微控制器、LCD驱动器、存储器、键盘,连接的器件可以工作在发送和(或)接收状态。很显然,LCD驱动器等一些器件只能是接收器,而存储器可以发送和接收数据。对于AT24系列存储器来说,器件的地址是通过把地址输入端A0,A1,A2进行硬件连接来确定的。

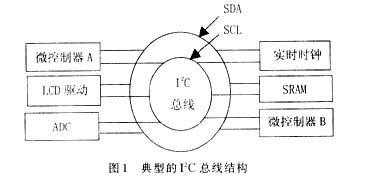

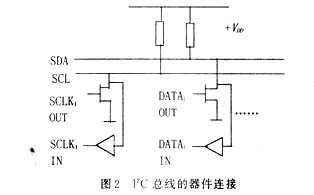

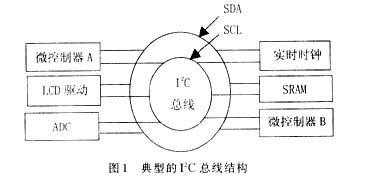

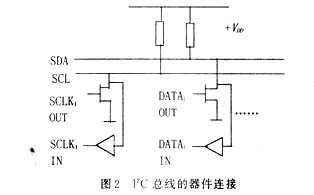

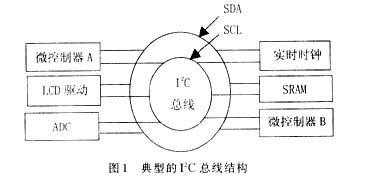

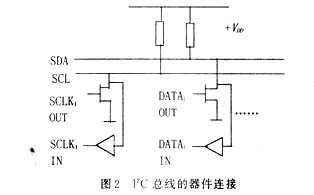

图1是典型的I2C总线结构。SDA和SCL都是双向线,通过上拉电阻接正电源。当总线空闲时,这两根线处于高电平状态,连到总线的器件的输出级必须是开漏极或集电极开路,以具有线“与”的功能。设备与总线的接口电路如图2所示。

2 I2C总线的数据传输

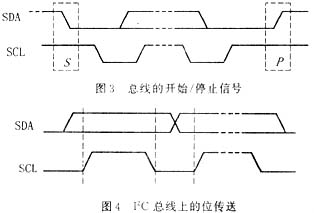

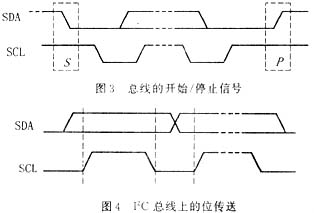

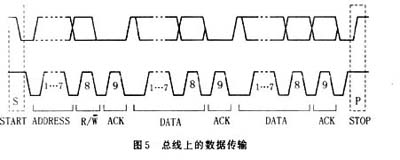

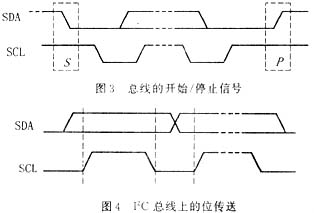

在I2C总线的数据传输过程中,定义了开始和停止信号。如图3所示,SCL保持“高”,SDA由“高”变为“低”为开始信号;SCL保持“高”,SDA由“低”变为“高”为停止信号。开始(S)和停止(P)信号由主器件产生。在时钟高电平期间上的数据必须保持稳定,如图4所示,只有在时钟线SCL的时钟低电平期间,SDA线上高电平或低电平才能变化。

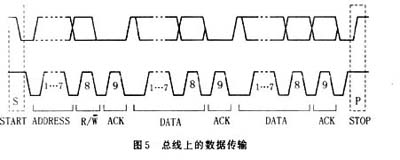

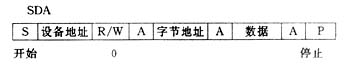

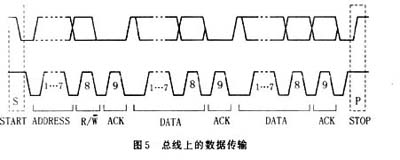

到SDA线上的每个字节必须是8位长度,每次传输的字节数是不受限制的,每个字节后面必须跟一个响应位。如果一个接收器件在完成其他功能前(如一个内部中断)不能接收另一个数据的完整字节时,可以使时钟保持低电平,以促使发送器进入等待状态。当接收器准备好接收下一个数据字节并释放SCL线,数据传输继续进行。图5表示出了I2C总线上的数据传送时序。

数据传送具有应答是必须的。与应答对应的时钟脉冲由主控器件产生。发送器在应答期间必须下拉SDA线。当寻址的被控器件不能应答时,数据保持为高,于是主器件产生停止信号终止传输。

3 IP核的设计

3.1 该IP核设计与软件实现的比较

在I2C总线的应用中,实现微机与AT24系列存储器之间的通信,可以把微机的通用I/O口作为I2C总线的接口,通过汇编由软件控制实现数据的传输。由于软件在操作上时间的原因,速度总要受到限制。并且汇编控制也很难作为一个统一的标准在应用中推广。通过IP核设计,我们可以在硬件上实现数据串并转换的目的。工作的速度只与存储器本身的特性有关,克服了软件在此方面的不足。

3.2 系统设计方案

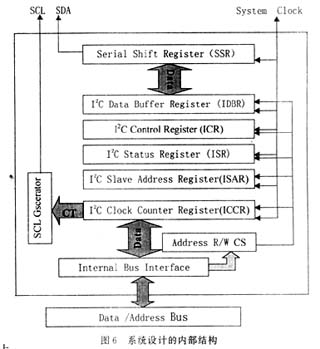

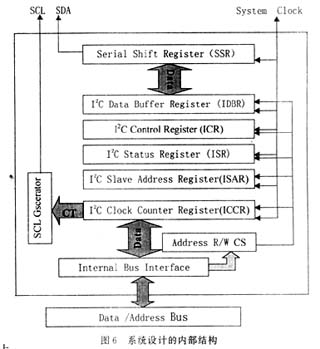

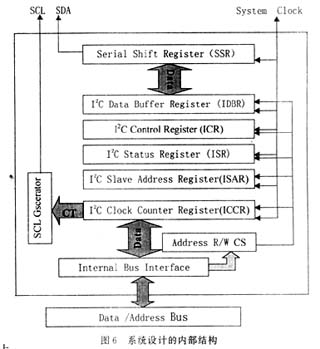

该系统主要由I2C串行移位寄存器(SSR)、数据缓冲寄存器(IDBR)、控制寄存器(ICR)、状态寄存器(ISR)、从地址寄存器(ICCR)、SCL产生器(SCL Generator)及其他总线组成。图6为其基本内部结构。

在该系统中,SSR把并行数据变为串行数据,传输给存储器,或者把存储器的串行数据变为并行数据,传输为处理器;IDBR把并口来的数据或把被转换成并行的数据暂且装载起来;ICR控制着整个系统的读/写、数据的转换等操作;ISR则监视着系统的状态。

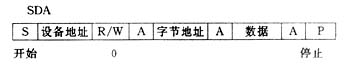

3.3 数据的通信格式

主控制器(CPU)如果要从存储器读数据或者写(0表示写)数据到存储器,则需经过接口转换。SDA上的信号传输要遵循一定的格式。在主控制器(CPU)给存储器写数据时,把设备地址、字节地址和数据送给接口,接口完成与存储器之间的数据交换。如下:

其中确认(A)是存储器传送给接口的信号,其余的如开始(S)、设备地址等信号是接口产生的信号。

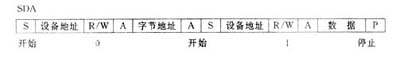

主控制器从接口读数据时,会把设备地址、字节地址和读信号告诉接口,接口通过与存储器进行数据交换,把数据读出来,送给主控制器。数据格式如下:

其中确认(A)和数据是存储器产生的,其余的如开始(S)、设备地址、停止(P)等信号是接口产生的。

3.4 IP核的VHDL设计

该IP核的VHDL设计从低到高共5个模块。这几个模块分别为头地址移位寄存器模块、数据移位寄存器模块、计数器模块、控制模块和外围综合模块。

头地址移位寄存器是用来装载写入(读出)设备地址,在控制模块的控制下,把设备地址移位到串行数据线SDA上。数据移位寄存器是用来装载写入/读出的数据、字节地址,并在控制模块的控制下,把写入的数据、字节地址移位到SDA上,或者把从SDA读出的串行数据变为并行数据,以传送给主控制器。在该IP核设计中,需要对移位的数据字节进行记数,计数器模块实现该功能。控制模块主要通过以刚提到的三个模块为基础,实现了数据的单向传输,也就是把双向的数据线分成2根单向的数据线来传输数据。而外围综合模块则把2根单向的的数据线综合成一根双向的数据线SDA,实现了接口的串并转换功能。

3.5 VHDL的实现与仿真

硬件描述语言VHDL(Very-high Speed IC Hard-ware Description Language)是一种用于电路设计的高层次描述语言,具有行为级、寄存器传输级和门级等多层次描述,并具有简单、易读、易修改和与工艺无关等优点。本设计采用MAX+plus Ⅱ 9.5 作为综合工具,对设计的VHDL程序进行调试和波形仿真。

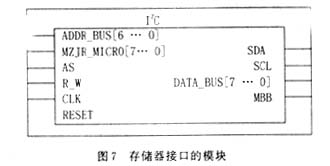

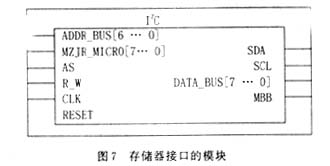

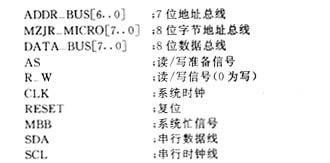

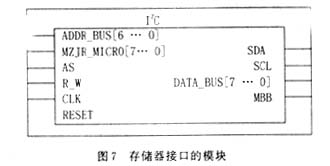

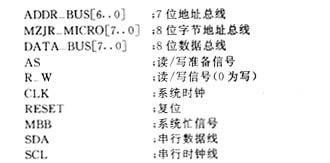

在调试中,MAX+plus Ⅱ生成所需要的I2C接口模块,如图7所示,表示了整个接口的外部结构。

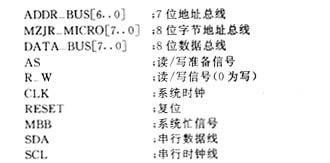

其中各个管脚的意义如下:

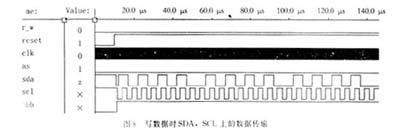

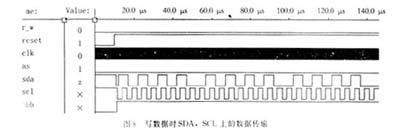

在仿真中,选择EPF10K10LC84-3 作为下载芯片来实现模拟仿真。当向存储器写数据时,串行时钟线和数据线得到图8所示的仿真波形。

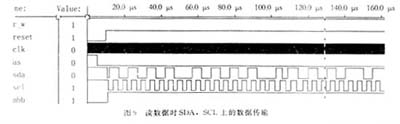

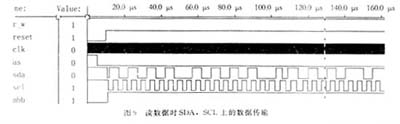

当从芯片中读数据时,串行数据线和时钟线上得到的仿真波形如图9。

4 结论

以上介绍了基于I2C总线协议的AT24系列存储器数据串并转换接口的VHDL设计,该接口是针对8位微处理器而设计的。基于FPGA技术的基础上,把软件仿真、编译成功的程序,经JTAG电缆下载到以上指定的芯片上,用89C51与设计的接口进行数据通信,通过硬件验证,能实现它应具备的功能,可在通信系统中得到运用。

1 I2C总线的基本概念

I2C总线协议是Philips公司推出的总线协议。它是多主机总线,通过2根线(SDA-aserial data line,SCL-a serial clock line)与连接到总线上的器件之间传送信息,根据地址识别每个器件。例如,微控制器、LCD驱动器、存储器、键盘,连接的器件可以工作在发送和(或)接收状态。很显然,LCD驱动器等一些器件只能是接收器,而存储器可以发送和接收数据。对于AT24系列存储器来说,器件的地址是通过把地址输入端A0,A1,A2进行硬件连接来确定的。

图1是典型的I2C总线结构。SDA和SCL都是双向线,通过上拉电阻接正电源。当总线空闲时,这两根线处于高电平状态,连到总线的器件的输出级必须是开漏极或集电极开路,以具有线“与”的功能。设备与总线的接口电路如图2所示。

2 I2C总线的数据传输

在I2C总线的数据传输过程中,定义了开始和停止信号。如图3所示,SCL保持“高”,SDA由“高”变为“低”为开始信号;SCL保持“高”,SDA由“低”变为“高”为停止信号。开始(S)和停止(P)信号由主器件产生。在时钟高电平期间上的数据必须保持稳定,如图4所示,只有在时钟线SCL的时钟低电平期间,SDA线上高电平或低电平才能变化。

到SDA线上的每个字节必须是8位长度,每次传输的字节数是不受限制的,每个字节后面必须跟一个响应位。如果一个接收器件在完成其他功能前(如一个内部中断)不能接收另一个数据的完整字节时,可以使时钟保持低电平,以促使发送器进入等待状态。当接收器准备好接收下一个数据字节并释放SCL线,数据传输继续进行。图5表示出了I2C总线上的数据传送时序。

数据传送具有应答是必须的。与应答对应的时钟脉冲由主控器件产生。发送器在应答期间必须下拉SDA线。当寻址的被控器件不能应答时,数据保持为高,于是主器件产生停止信号终止传输。

3 IP核的设计

3.1 该IP核设计与软件实现的比较

在I2C总线的应用中,实现微机与AT24系列存储器之间的通信,可以把微机的通用I/O口作为I2C总线的接口,通过汇编由软件控制实现数据的传输。由于软件在操作上时间的原因,速度总要受到限制。并且汇编控制也很难作为一个统一的标准在应用中推广。通过IP核设计,我们可以在硬件上实现数据串并转换的目的。工作的速度只与存储器本身的特性有关,克服了软件在此方面的不足。

3.2 系统设计方案

该系统主要由I2C串行移位寄存器(SSR)、数据缓冲寄存器(IDBR)、控制寄存器(ICR)、状态寄存器(ISR)、从地址寄存器(ICCR)、SCL产生器(SCL Generator)及其他总线组成。图6为其基本内部结构。

在该系统中,SSR把并行数据变为串行数据,传输给存储器,或者把存储器的串行数据变为并行数据,传输为处理器;IDBR把并口来的数据或把被转换成并行的数据暂且装载起来;ICR控制着整个系统的读/写、数据的转换等操作;ISR则监视着系统的状态。

3.3 数据的通信格式

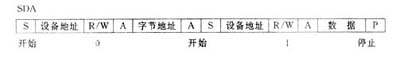

主控制器(CPU)如果要从存储器读数据或者写(0表示写)数据到存储器,则需经过接口转换。SDA上的信号传输要遵循一定的格式。在主控制器(CPU)给存储器写数据时,把设备地址、字节地址和数据送给接口,接口完成与存储器之间的数据交换。如下:

其中确认(A)是存储器传送给接口的信号,其余的如开始(S)、设备地址等信号是接口产生的信号。

主控制器从接口读数据时,会把设备地址、字节地址和读信号告诉接口,接口通过与存储器进行数据交换,把数据读出来,送给主控制器。数据格式如下:

其中确认(A)和数据是存储器产生的,其余的如开始(S)、设备地址、停止(P)等信号是接口产生的。

3.4 IP核的VHDL设计

该IP核的VHDL设计从低到高共5个模块。这几个模块分别为头地址移位寄存器模块、数据移位寄存器模块、计数器模块、控制模块和外围综合模块。

头地址移位寄存器是用来装载写入(读出)设备地址,在控制模块的控制下,把设备地址移位到串行数据线SDA上。数据移位寄存器是用来装载写入/读出的数据、字节地址,并在控制模块的控制下,把写入的数据、字节地址移位到SDA上,或者把从SDA读出的串行数据变为并行数据,以传送给主控制器。在该IP核设计中,需要对移位的数据字节进行记数,计数器模块实现该功能。控制模块主要通过以刚提到的三个模块为基础,实现了数据的单向传输,也就是把双向的数据线分成2根单向的数据线来传输数据。而外围综合模块则把2根单向的的数据线综合成一根双向的数据线SDA,实现了接口的串并转换功能。

3.5 VHDL的实现与仿真

硬件描述语言VHDL(Very-high Speed IC Hard-ware Description Language)是一种用于电路设计的高层次描述语言,具有行为级、寄存器传输级和门级等多层次描述,并具有简单、易读、易修改和与工艺无关等优点。本设计采用MAX+plus Ⅱ 9.5 作为综合工具,对设计的VHDL程序进行调试和波形仿真。

在调试中,MAX+plus Ⅱ生成所需要的I2C接口模块,如图7所示,表示了整个接口的外部结构。

其中各个管脚的意义如下:

在仿真中,选择EPF10K10LC84-3 作为下载芯片来实现模拟仿真。当向存储器写数据时,串行时钟线和数据线得到图8所示的仿真波形。

当从芯片中读数据时,串行数据线和时钟线上得到的仿真波形如图9。

4 结论

以上介绍了基于I2C总线协议的AT24系列存储器数据串并转换接口的VHDL设计,该接口是针对8位微处理器而设计的。基于FPGA技术的基础上,把软件仿真、编译成功的程序,经JTAG电缆下载到以上指定的芯片上,用89C51与设计的接口进行数据通信,通过硬件验证,能实现它应具备的功能,可在通信系统中得到运用。

举报

举报

举报

举报