基带光纤拉远是将数字微波接力系统的中频部分从室内单元移至室外单元。由于信号拉远的物理介质采用的是光纤,而且传输的是基带数字信号,因此传输距离一般可达几km以上。基带光纤拉远避免了系统的室内单元和室外单元之间馈线连接的不便,同时减少了馈线损耗,降低了功率放大器的功率要求,最重要的是天线的位置调整不再受室内单元的制约,可以依据周边环境特点,选择合适的地点架设,降低了设备开通的难度。本文介绍了88E1111的功能和特点,并给出了采用88E1111完成数字微波接力系统基带光纤拉远的接13设计方案,解决了基带光纤拉远接口设计复杂、难以实现的问题。

1 88E1111简介

1.1 88E1111的功能特点

88E1111是Marvell公司推出的单片集成高性能千兆以太网物理层芯片,具有如下功能:完整支持IEEE802.3协议簇;内置1.25 G串行解串行器,满足千兆光传输应用;支持GMII、TBI、RGMII、RTBI等多种MAC层接口;支持10/100/1000BaseT自适应检测;采用0.13 μm CMOS工艺,支持2.5 V、1.2 V低电压供电,最大功耗O.75W,且支持自动降功耗功能。

1.2 88E1111的接口

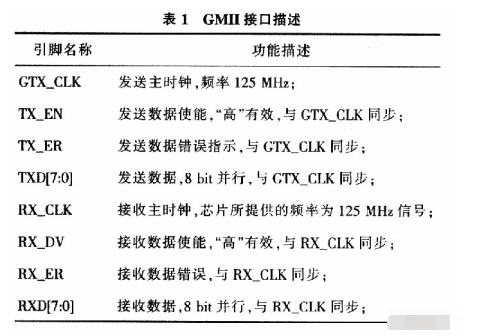

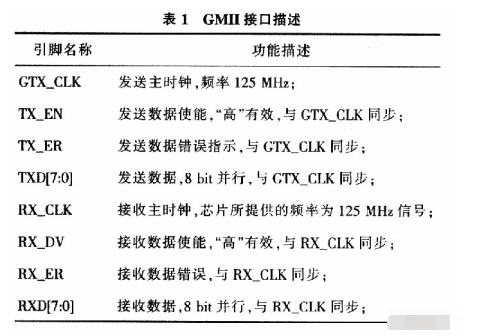

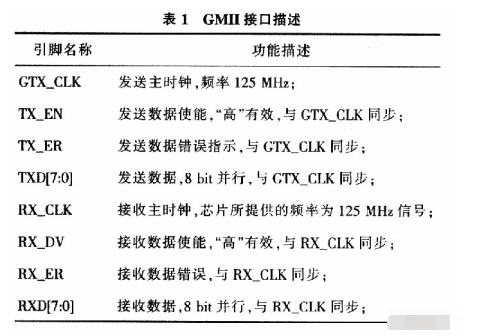

1)GMII接口 88E1111与MAC层之间的数据接口见表1。

2)Management接口 由MDC、MDIO 2个信号组成,MDC为时钟信号,最大速率8.3 MHz;MDIO为数据信号,同步于MDC。数据流中出现“0 1”表示操作的开始;紧随其后是操作码,“10”表示读操作,“01”表示写操作;然后是物理地址、寄存器地址、寄存器数据。CPU通过访问相应的物理地址、寄存器地址,对芯片进行控制和监测。

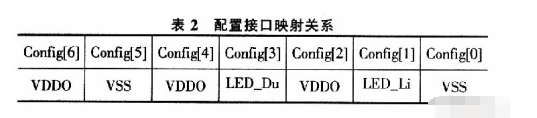

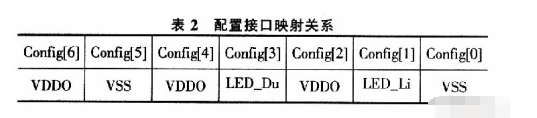

3)LED/Configuration接口 LED接口由LED_Link10、LED_Link100、LED_Link1000、LED_TX、LED_RX、LED-Duplex、VDDO、VSS组成。Co-nfiguration接口由Config[6:0]组成。通过将Config[6:0]连接到LED接口的不同信号,可以将芯片配置到相应的工作模式。典型的1000Ba-seX、全双工工作模式配置映射关系如表2所示。

4)高速串行信号接口 由3对差分信号组成,接口电平为CML,其中S_IN±为串行数据输入、S_OUT±为串行数据输出、SD±为光功率有效输入。

1.3 88E1111的寄存器

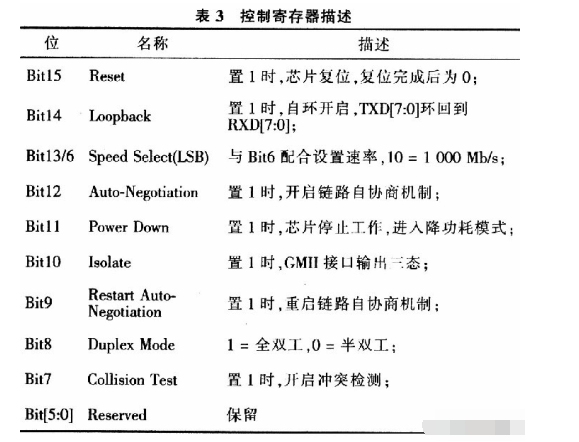

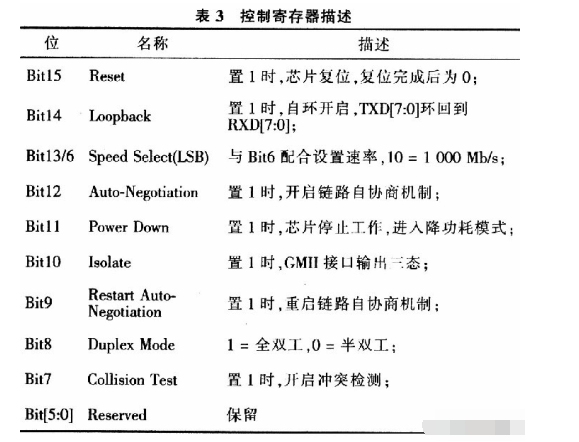

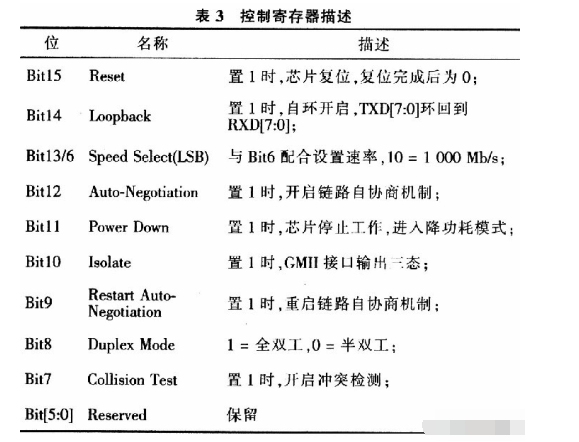

88E1111共有32个控制寄存器,每个寄存器16 bit,地址偏移量为OOH~1FH。功能为复位芯片、设置速率、双工模式等,其描述如表3所示。

2 方案设计

根据88E1111的功能特点和基带光纤拉远的设计要求,本文提出了用88E1111完成数字微波接力系统基带光纤拉远的接口设计方案。接口设计方案框图如图1所示,主要由室内单元、室外单元2部分组成。发方向,室内单元业务码流输入FPGA复分解器,完成业务数据打包,封装成符合IEEE802.3标准的数据帧结构,通过GMII接口发送到88E1111,由88E1111完成数据并串转换,通过高速串行信号接口将信号发送到1.25 G光收发器,完成电光转换后向室外单元发送1.25 G光信号。室外单元1.25 G光收发器接收光信号,完成光电转换,通过高速串行信号接口将高速电信号输入88E1111,由88Ellll完成数据串并转换,通过GMII接口将并行数据发送到FPGA调制解调器,完成数据解帧、调制后,通过中频射频单元向空中发送无线射频信号。收方向为发方向的逆向流程。

3 硬件设计

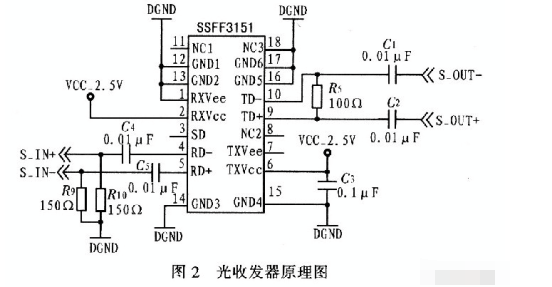

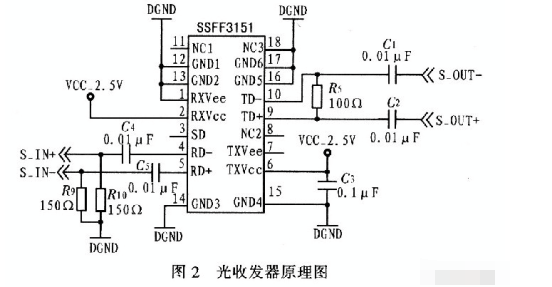

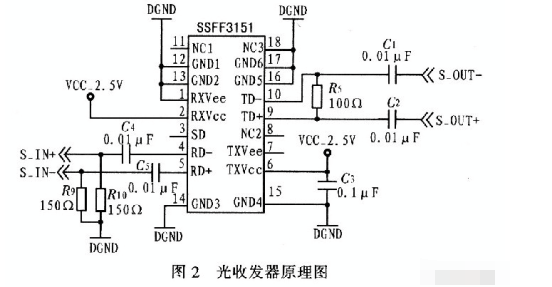

图2所示是1.25 G光收发器SSFF315l的电路原理图,其收发引脚RD±、TD±分别连接到88E1111的高速串行信号接口S_IN±、S_0UT±信号。图3所示是88E1111的电路原理图,其主要引脚连接关系如下:GMII接口信号(详见表1连接到FPGA;Management接口信号MDl0、MDC连接到微处理器;Config接口信号按表2映射关系连接到LED接口;XTALl引脚输入125 MHz时钟信号,频率稳定度±50 ppm;RSET为芯片参考电压输入引脚,通过5 kΩ精密电阻连接到地;SEL_FREQ为时钟输入选择引脚,接低电平时,选择125 MHz时钟输入。

88E1111完全按照IEEE802.3协议工作。TX_CLX为发送时钟,TX_EN为发送使能信号,TX_EN有效时,在发送时钟TX_CLK的上升沿传送数据,TXD[7:0]至88E1111,完成发送操作。RX_CLK为接收时钟,RX_DV是接收数据使能信号。RX_DV有效时,在接收时钟RX_CLK的上升沿从88E1111接收数据RXD[7:0],完成接收操作。

4 设计中应注意的问题

4.1 电气接口匹配

88E111l的高速串行信号接口为CML接口,光收发器的信号接口为LVPECL接口。因此接口之间要增加CML转LVPECL电气接口匹配电路。采用交流耦合接口匹配电路时,发送端在IVPECL的2个输出信号上各加一个到地的偏置电阻,即图2中R9、R10,电阻值选取范围142~200Ω。输入端在LVPECL的2个输入信号之间跨接一个电阻,即R5,阻值取100 Ω。

4.2 GMII接口设计

GMII接口数据速率达到125 Mb/s,速率较高,为了避免各个信号在PCB板上由于传播时延不同而造成相位误差,布线时,TXD[7:0]、CTX_CLK、TX_EN为一组信号,RXD[7:0]、RX_CLK、RX_DV为一组信号,两组信号必须严格等长。

4.3 PCB布线设计

基带光纤拉远接口板上有LVTTL、LVPECL、CML等多种信号。为避免相互干扰,PCB布线时应注意,在差分线对内,2条线之间的距离应尽可能短,以保持接收器的共模抑制能力,在PCB板上,2条差分线之间的距离应尽可能保持一致,以避免差分阻抗的不连续性。

5 结束语

基于88E1111的基带光纤拉远接口设计方案,在千兆、全双工运行模式下,接口数据传输速率可达800 Mb/s;在单模光纤传输时,传输距离可达20 km,完全达到数字微波接力系统的设计要求。本方案已在多个数字微波接力产品中得到应用,具有设计简单、性能稳定的优点。相比传统的方案有以下2个创新点:1)传输数据采用符合IEEE802.3协议的数据帧结构,接口标准、可靠;2)采用光纤作为传输介质,避免了系统的室内外单元之间馈线连接的不便,大大降低了系统成本和设备开通的难度。

基带光纤拉远是将数字微波接力系统的中频部分从室内单元移至室外单元。由于信号拉远的物理介质采用的是光纤,而且传输的是基带数字信号,因此传输距离一般可达几km以上。基带光纤拉远避免了系统的室内单元和室外单元之间馈线连接的不便,同时减少了馈线损耗,降低了功率放大器的功率要求,最重要的是天线的位置调整不再受室内单元的制约,可以依据周边环境特点,选择合适的地点架设,降低了设备开通的难度。本文介绍了88E1111的功能和特点,并给出了采用88E1111完成数字微波接力系统基带光纤拉远的接13设计方案,解决了基带光纤拉远接口设计复杂、难以实现的问题。

1 88E1111简介

1.1 88E1111的功能特点

88E1111是Marvell公司推出的单片集成高性能千兆以太网物理层芯片,具有如下功能:完整支持IEEE802.3协议簇;内置1.25 G串行解串行器,满足千兆光传输应用;支持GMII、TBI、RGMII、RTBI等多种MAC层接口;支持10/100/1000BaseT自适应检测;采用0.13 μm CMOS工艺,支持2.5 V、1.2 V低电压供电,最大功耗O.75W,且支持自动降功耗功能。

1.2 88E1111的接口

1)GMII接口 88E1111与MAC层之间的数据接口见表1。

2)Management接口 由MDC、MDIO 2个信号组成,MDC为时钟信号,最大速率8.3 MHz;MDIO为数据信号,同步于MDC。数据流中出现“0 1”表示操作的开始;紧随其后是操作码,“10”表示读操作,“01”表示写操作;然后是物理地址、寄存器地址、寄存器数据。CPU通过访问相应的物理地址、寄存器地址,对芯片进行控制和监测。

3)LED/Configuration接口 LED接口由LED_Link10、LED_Link100、LED_Link1000、LED_TX、LED_RX、LED-Duplex、VDDO、VSS组成。Co-nfiguration接口由Config[6:0]组成。通过将Config[6:0]连接到LED接口的不同信号,可以将芯片配置到相应的工作模式。典型的1000Ba-seX、全双工工作模式配置映射关系如表2所示。

4)高速串行信号接口 由3对差分信号组成,接口电平为CML,其中S_IN±为串行数据输入、S_OUT±为串行数据输出、SD±为光功率有效输入。

1.3 88E1111的寄存器

88E1111共有32个控制寄存器,每个寄存器16 bit,地址偏移量为OOH~1FH。功能为复位芯片、设置速率、双工模式等,其描述如表3所示。

2 方案设计

根据88E1111的功能特点和基带光纤拉远的设计要求,本文提出了用88E1111完成数字微波接力系统基带光纤拉远的接口设计方案。接口设计方案框图如图1所示,主要由室内单元、室外单元2部分组成。发方向,室内单元业务码流输入FPGA复分解器,完成业务数据打包,封装成符合IEEE802.3标准的数据帧结构,通过GMII接口发送到88E1111,由88E1111完成数据并串转换,通过高速串行信号接口将信号发送到1.25 G光收发器,完成电光转换后向室外单元发送1.25 G光信号。室外单元1.25 G光收发器接收光信号,完成光电转换,通过高速串行信号接口将高速电信号输入88E1111,由88Ellll完成数据串并转换,通过GMII接口将并行数据发送到FPGA调制解调器,完成数据解帧、调制后,通过中频射频单元向空中发送无线射频信号。收方向为发方向的逆向流程。

3 硬件设计

图2所示是1.25 G光收发器SSFF315l的电路原理图,其收发引脚RD±、TD±分别连接到88E1111的高速串行信号接口S_IN±、S_0UT±信号。图3所示是88E1111的电路原理图,其主要引脚连接关系如下:GMII接口信号(详见表1连接到FPGA;Management接口信号MDl0、MDC连接到微处理器;Config接口信号按表2映射关系连接到LED接口;XTALl引脚输入125 MHz时钟信号,频率稳定度±50 ppm;RSET为芯片参考电压输入引脚,通过5 kΩ精密电阻连接到地;SEL_FREQ为时钟输入选择引脚,接低电平时,选择125 MHz时钟输入。

88E1111完全按照IEEE802.3协议工作。TX_CLX为发送时钟,TX_EN为发送使能信号,TX_EN有效时,在发送时钟TX_CLK的上升沿传送数据,TXD[7:0]至88E1111,完成发送操作。RX_CLK为接收时钟,RX_DV是接收数据使能信号。RX_DV有效时,在接收时钟RX_CLK的上升沿从88E1111接收数据RXD[7:0],完成接收操作。

4 设计中应注意的问题

4.1 电气接口匹配

88E111l的高速串行信号接口为CML接口,光收发器的信号接口为LVPECL接口。因此接口之间要增加CML转LVPECL电气接口匹配电路。采用交流耦合接口匹配电路时,发送端在IVPECL的2个输出信号上各加一个到地的偏置电阻,即图2中R9、R10,电阻值选取范围142~200Ω。输入端在LVPECL的2个输入信号之间跨接一个电阻,即R5,阻值取100 Ω。

4.2 GMII接口设计

GMII接口数据速率达到125 Mb/s,速率较高,为了避免各个信号在PCB板上由于传播时延不同而造成相位误差,布线时,TXD[7:0]、CTX_CLK、TX_EN为一组信号,RXD[7:0]、RX_CLK、RX_DV为一组信号,两组信号必须严格等长。

4.3 PCB布线设计

基带光纤拉远接口板上有LVTTL、LVPECL、CML等多种信号。为避免相互干扰,PCB布线时应注意,在差分线对内,2条线之间的距离应尽可能短,以保持接收器的共模抑制能力,在PCB板上,2条差分线之间的距离应尽可能保持一致,以避免差分阻抗的不连续性。

5 结束语

基于88E1111的基带光纤拉远接口设计方案,在千兆、全双工运行模式下,接口数据传输速率可达800 Mb/s;在单模光纤传输时,传输距离可达20 km,完全达到数字微波接力系统的设计要求。本方案已在多个数字微波接力产品中得到应用,具有设计简单、性能稳定的优点。相比传统的方案有以下2个创新点:1)传输数据采用符合IEEE802.3协议的数据帧结构,接口标准、可靠;2)采用光纤作为传输介质,避免了系统的室内外单元之间馈线连接的不便,大大降低了系统成本和设备开通的难度。

举报

举报

举报

举报