1 引言

典型的GPS接收机主要由4部分组成:天线、射频前端、相关器和导航解算部分。其中,天线主要负责信号的接收;射频前端负责信号的下变频,在当前的数字化接收机中还包括A/D转换,它是所有后端处理的基础,其信号的品质直接影响接收机的性能,相关器主要负责信号跟踪与锁定的硬件部分,包括各种原始数据和测量数据的输出,并传输给微处理器;导航解算部分主要负责信号的跟踪和锁定的软件部分、数据的解调、伪距的提取以及导航数据的解算,它的处理基础是相关器,所有的原始数据来自相关器。

2 GP2015及其外围电路

GP2015是Zarlink半导体公司的超小型射频前端器件,它包含除中频滤波器外的所有从天线接收的L1频段信号到两位数字信号的模块。其中,中频滤波在片外,分别由一个157.42MHz滤波器和一个35.42MHz声表面滤波器组成,包含在VCO(压控振荡器)中的片上PLL用于产生一个本地的振荡频率来提供给混频器,它的参考信号是来自温度补偿晶振(TCXO)的10.0 00MHz。

Dynex DW9255是声表面波带通滤波器,用它对GPS信号扩频信号的窄带宽进行滤波,在使用之前应该预先调到GPS二级中频的准确频段35.42MHz和1.9MHz的带宽。滤波器通带的弱衰减性和阻带的强衰减性有助于改进GP2015的抗干扰性。

GP4020是完整的基于GPS接收机的数字基带处理器,它由一个12通道的相关器和带ARM7TDMI核的微处理器组成。其中,相关器包含12个独立通道的跟踪模块,每个模块包含所有的跟踪和锁定GPS信号的模块,不是每个通道都必须在跟踪的时候激活,这样可以减少电源的消耗,微处理器部分包含萤火虫MF1微控制器。它采用了ARM7TDMI核,带有THUMB的指令集,还包含UART串行接口、通用I/O和看门狗的功能。

在整个设计过程中,射频部分的设计是基础,它的良好实现才能保证以后部分的正确定位信息的输出。文中主要针对GP2015的设计,讨论GPS接收机射频模块的实现过程。

3 GP2015射频模块的设计

本设计选用的GP2015有48个引脚,采用TQFP封装,工作电压是3V至5V,在3V的工作电压下,功耗只有200mW,带有片上锁相环。该电路完成下变频和A/D转换的功能。在该模块的设计中,除了电路本身完成的功能外,还需在中频变换中加入滤波器。

3.1 高频信号在电路板中的走线设计

高频信号在电路板上的布局一般采用微波传输带的方法,就是在一定宽度和厚度的绝缘基上的一条导体传输带,绝缘基将传输带与地分割开来,因为微波传输带周围的绝缘基都是一个不连续的空气和绝缘基的混合体,所以信号的传输都受边缘区域的影响,微波传输带特征阻抗的计算是很复杂的,但是能够通过一定的条件来简化。

在GPS接收机的设计中,电路板是4层,厚度为1.6mm,其中接地层在第2层。除每层35μm的铜线外,绝缘基大概有1.45mm厚,在4层信号连接层中,第2层和第3层都在内部实现,为了保持每层都占有相同的空间,将绝缘基设计为两块(0.5mm厚),一块对0.45mm厚(位于中间)。根据微波传输的计算公式,微波带大概应该有 0.8mm的宽度,50Ω的特征阻抗。

如果布局不一样或者电路板的层数不一样,则整个微波传输带的宽度可能需要重新计算和设计。

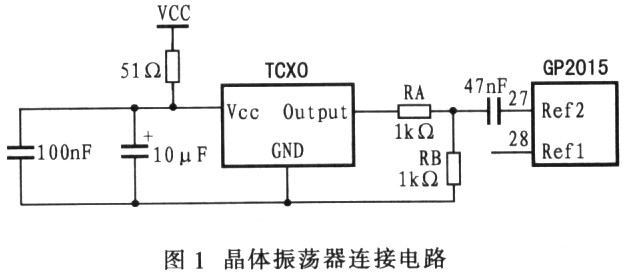

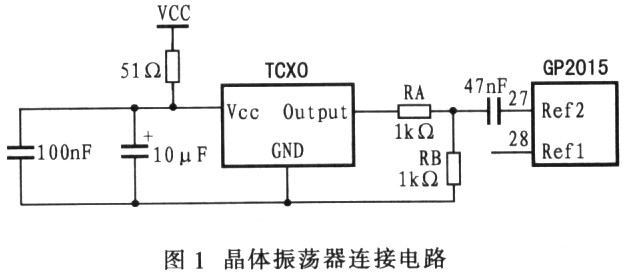

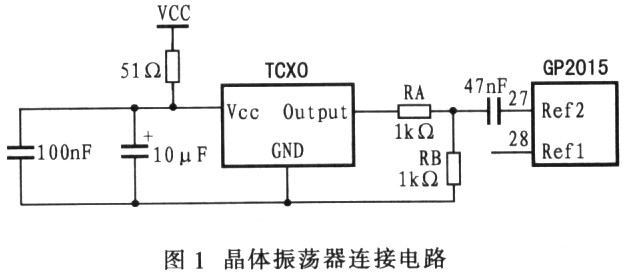

3.2 晶体振荡器匹配电路的设计

整个设计中的,所有的参考信号都由TCXO输入,GP2015中的振荡电路与外部晶体振荡器连接后产生10.000MHz的信号,在整个接收机中如果没有温度补偿晶振的稳定性就不足以保证信号的跟踪和锁定。基于这样的原因,接收机采用10.000MHz的TCXO。具体电路设计如图1所示。

如图1所示,在电源和VCC端串接了一只51Ω的电阻器,并在VCC和GND之间并接了1对电容,其TCXO的电流消耗不能超过5mA,否则51Ω电阻器上的压降就会很大。

3.3 第一级中频滤波器的设计

GP2105的第一次下变频至175.42MHz,在片外进行滤波,由于没有专用滤波器,所以第一级滤波器必须自行设计。滤波器放置在一级变频的输出端和二级变频的输入端。它要滤除二级中频的镜频干扰及有射频的镜频干扰,当然这些都能通过RF滤波器来进行消除。但是仍然推荐使用第一级的中频滤波器。

一级中频滤波器还用于滤除到达二级混频输入的干扰信号,GP2015的第一级混频输入需要DC偏移来实现最大的中频信号处理空间。通常第一级中频滤波应该包含一个DC连接,它通过1只上拉电感器来实现,同时从第一级到第二级的信号路径应该有交流去耦。在设计中采用了两个带有谐振器的耦合可调的IC滤波器,整个电路设计如图2所示。

3.4 第二级中频滤波器的设计

第二级中频滤波器的中心频率为35.42MHz,带宽约为+1.0MHz,插入损耗为14dB-18dB,衰减系数大于10dB。连接在二级混频的输出和三级混频的输入之间。该滤波器的带宽应该达到2MHz,同时对带外信号应该至少有20dB的衰减,所以它的响应曲线应该是一个brick-wall形状的曲线。在这一级的滤波器设计中,选用Dynex公司的DW9255来实现滤波。它可提供中心频率在35.42MHz的1.9MHz带宽,同时衰减只有1dB。带外信号的滤除在+2.0MHz达到21dB。

第三级混频后的滤波在片内完成,在此不作详细介绍。

1 引言

典型的GPS接收机主要由4部分组成:天线、射频前端、相关器和导航解算部分。其中,天线主要负责信号的接收;射频前端负责信号的下变频,在当前的数字化接收机中还包括A/D转换,它是所有后端处理的基础,其信号的品质直接影响接收机的性能,相关器主要负责信号跟踪与锁定的硬件部分,包括各种原始数据和测量数据的输出,并传输给微处理器;导航解算部分主要负责信号的跟踪和锁定的软件部分、数据的解调、伪距的提取以及导航数据的解算,它的处理基础是相关器,所有的原始数据来自相关器。

2 GP2015及其外围电路

GP2015是Zarlink半导体公司的超小型射频前端器件,它包含除中频滤波器外的所有从天线接收的L1频段信号到两位数字信号的模块。其中,中频滤波在片外,分别由一个157.42MHz滤波器和一个35.42MHz声表面滤波器组成,包含在VCO(压控振荡器)中的片上PLL用于产生一个本地的振荡频率来提供给混频器,它的参考信号是来自温度补偿晶振(TCXO)的10.0 00MHz。

Dynex DW9255是声表面波带通滤波器,用它对GPS信号扩频信号的窄带宽进行滤波,在使用之前应该预先调到GPS二级中频的准确频段35.42MHz和1.9MHz的带宽。滤波器通带的弱衰减性和阻带的强衰减性有助于改进GP2015的抗干扰性。

GP4020是完整的基于GPS接收机的数字基带处理器,它由一个12通道的相关器和带ARM7TDMI核的微处理器组成。其中,相关器包含12个独立通道的跟踪模块,每个模块包含所有的跟踪和锁定GPS信号的模块,不是每个通道都必须在跟踪的时候激活,这样可以减少电源的消耗,微处理器部分包含萤火虫MF1微控制器。它采用了ARM7TDMI核,带有THUMB的指令集,还包含UART串行接口、通用I/O和看门狗的功能。

在整个设计过程中,射频部分的设计是基础,它的良好实现才能保证以后部分的正确定位信息的输出。文中主要针对GP2015的设计,讨论GPS接收机射频模块的实现过程。

3 GP2015射频模块的设计

本设计选用的GP2015有48个引脚,采用TQFP封装,工作电压是3V至5V,在3V的工作电压下,功耗只有200mW,带有片上锁相环。该电路完成下变频和A/D转换的功能。在该模块的设计中,除了电路本身完成的功能外,还需在中频变换中加入滤波器。

3.1 高频信号在电路板中的走线设计

高频信号在电路板上的布局一般采用微波传输带的方法,就是在一定宽度和厚度的绝缘基上的一条导体传输带,绝缘基将传输带与地分割开来,因为微波传输带周围的绝缘基都是一个不连续的空气和绝缘基的混合体,所以信号的传输都受边缘区域的影响,微波传输带特征阻抗的计算是很复杂的,但是能够通过一定的条件来简化。

在GPS接收机的设计中,电路板是4层,厚度为1.6mm,其中接地层在第2层。除每层35μm的铜线外,绝缘基大概有1.45mm厚,在4层信号连接层中,第2层和第3层都在内部实现,为了保持每层都占有相同的空间,将绝缘基设计为两块(0.5mm厚),一块对0.45mm厚(位于中间)。根据微波传输的计算公式,微波带大概应该有 0.8mm的宽度,50Ω的特征阻抗。

如果布局不一样或者电路板的层数不一样,则整个微波传输带的宽度可能需要重新计算和设计。

3.2 晶体振荡器匹配电路的设计

整个设计中的,所有的参考信号都由TCXO输入,GP2015中的振荡电路与外部晶体振荡器连接后产生10.000MHz的信号,在整个接收机中如果没有温度补偿晶振的稳定性就不足以保证信号的跟踪和锁定。基于这样的原因,接收机采用10.000MHz的TCXO。具体电路设计如图1所示。

如图1所示,在电源和VCC端串接了一只51Ω的电阻器,并在VCC和GND之间并接了1对电容,其TCXO的电流消耗不能超过5mA,否则51Ω电阻器上的压降就会很大。

3.3 第一级中频滤波器的设计

GP2105的第一次下变频至175.42MHz,在片外进行滤波,由于没有专用滤波器,所以第一级滤波器必须自行设计。滤波器放置在一级变频的输出端和二级变频的输入端。它要滤除二级中频的镜频干扰及有射频的镜频干扰,当然这些都能通过RF滤波器来进行消除。但是仍然推荐使用第一级的中频滤波器。

一级中频滤波器还用于滤除到达二级混频输入的干扰信号,GP2015的第一级混频输入需要DC偏移来实现最大的中频信号处理空间。通常第一级中频滤波应该包含一个DC连接,它通过1只上拉电感器来实现,同时从第一级到第二级的信号路径应该有交流去耦。在设计中采用了两个带有谐振器的耦合可调的IC滤波器,整个电路设计如图2所示。

3.4 第二级中频滤波器的设计

第二级中频滤波器的中心频率为35.42MHz,带宽约为+1.0MHz,插入损耗为14dB-18dB,衰减系数大于10dB。连接在二级混频的输出和三级混频的输入之间。该滤波器的带宽应该达到2MHz,同时对带外信号应该至少有20dB的衰减,所以它的响应曲线应该是一个brick-wall形状的曲线。在这一级的滤波器设计中,选用Dynex公司的DW9255来实现滤波。它可提供中心频率在35.42MHz的1.9MHz带宽,同时衰减只有1dB。带外信号的滤除在+2.0MHz达到21dB。

第三级混频后的滤波在片内完成,在此不作详细介绍。

举报

举报

举报

举报