随着DSP处理器在现代工业的应用越来越广泛,DSP的功能不仅只有快速运算处理,还需要与其他处理器或者设备之间进行实时数据交换,以实现资源的共享。因此,针对不同设备的需求,选择稳定、快速和高效率的接口方式在当今数字信号处理系统设计中关键的组成部分。

TI公司的8核处理器TMS320C6678(以下简称C6678)提供丰富的片上接口资源用于处理器与外设之间的通信,这些接口都可以用于DSP与外设之间的通信,但是灵活性有差异,使用SGMII接口来实现千兆以太网通信,可使得通信接口一般化,能够适用于众多的设备连接。本文针对C6678的芯片特点以及含有的接口资源,设计实现了千兆以太网通信,主要设计了以太网接口电路、网络底层硬件驱动、TCP/IP协议的用户程序,并完成了与上位机以太网通信测试,实现了数字信号高速有效地网络传输。

1 C6678以太网交换子系统

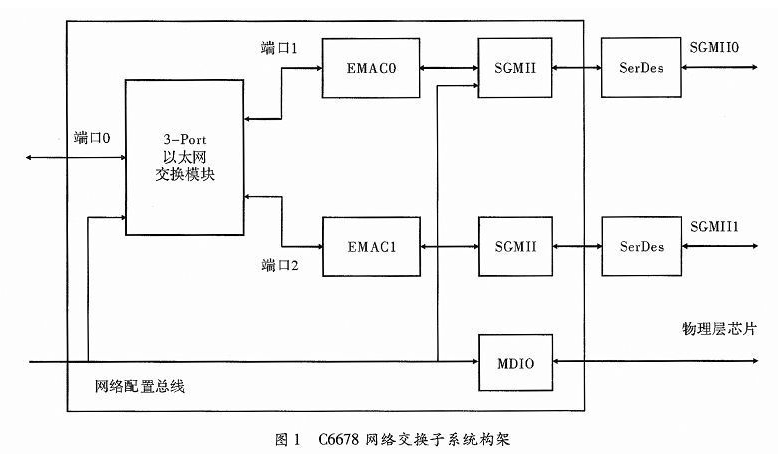

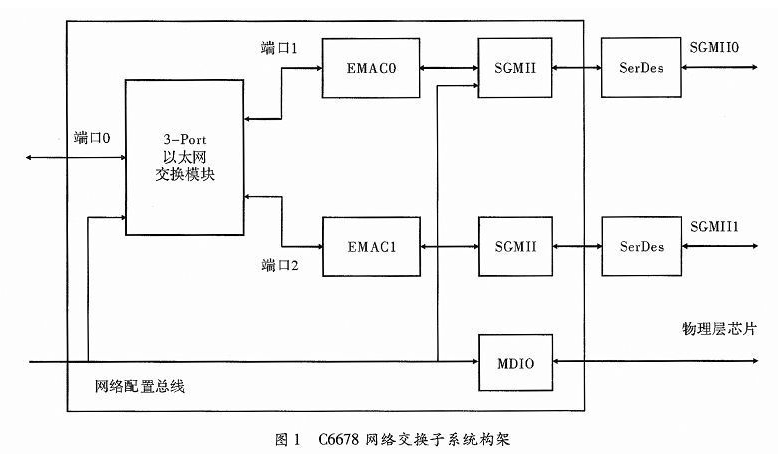

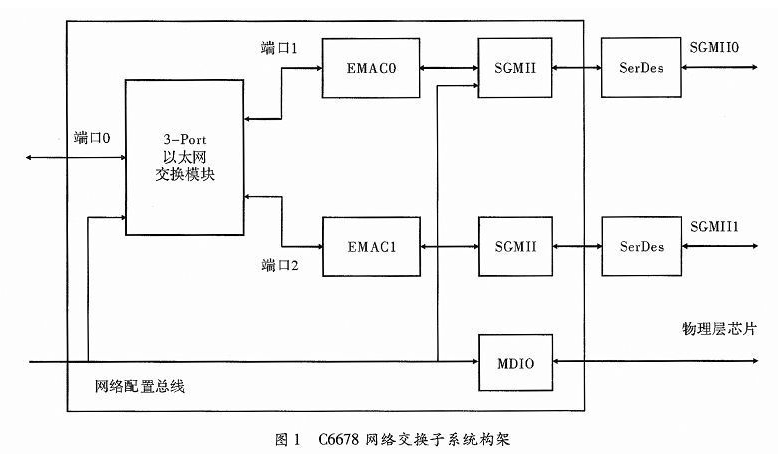

C6678是基于KeyStone I构架的8核高性能、定点/浮点处理器,单核最高工作频率可达1.25 GHz。C6678的以太网交换子系统包括2个以太网媒体访问控制(Ethernet Media Access Controller,EMAC)、2个SGMII、1个管理数据输入输出(Management Data Input Output,MDIO)、3-Port以太网交换模块以及网络配置总线,其网络交换子系统如图1所示。

EMAC的作用是将交换子系统的内部信号转换为GMII信号传递给SGMII模块;MDIO控制物理层芯片执行对多数据流的控制输入输出。

2 PHY芯片88E1111

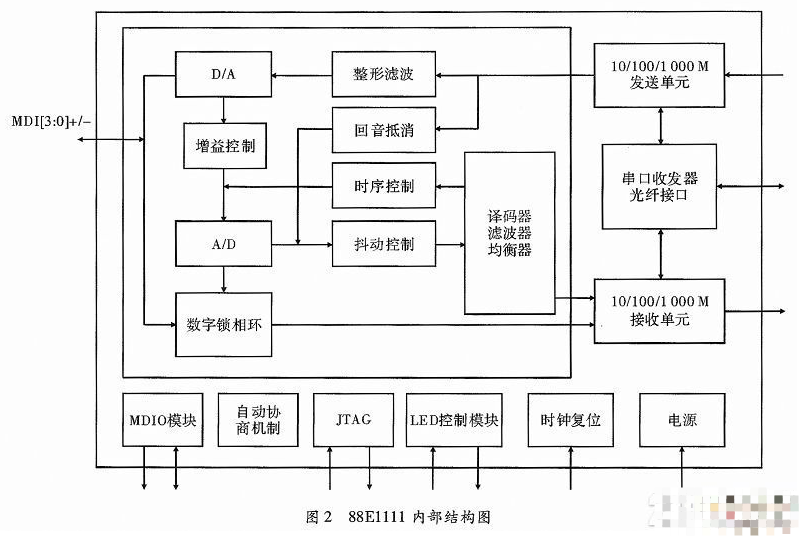

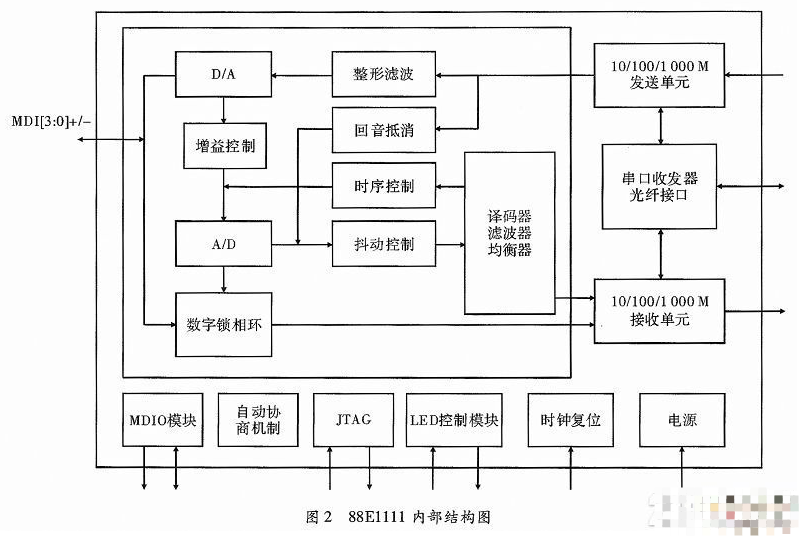

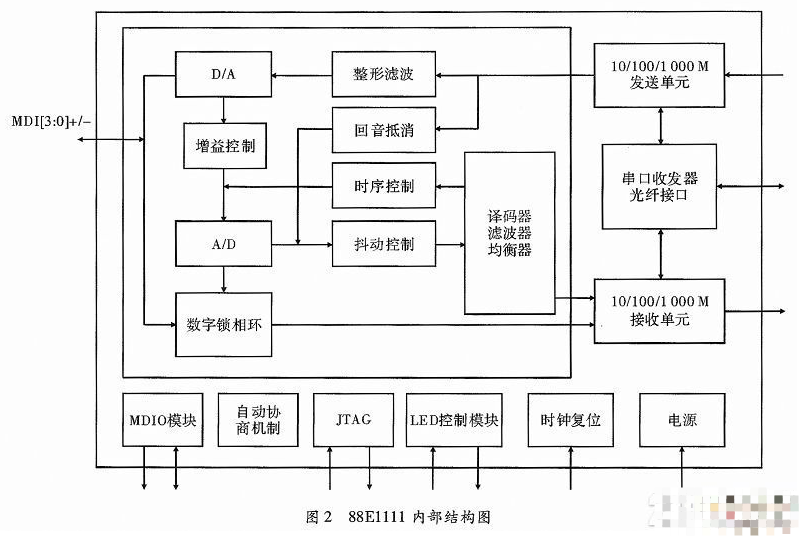

本文选择C6678作为主芯片,由于C6678的千兆网络交换子系统只支持SGMII接口,所以本文选择对SGMII接口的网络数据传输具有较好兼容性的物理芯片88E1111。88E1111芯片的内部结构如图2所示。

88E1111的介质接口有铜介质接口和光纤接口。铜介质接口为MDI[3:0],通过设置HWCFG_MODE[3:0]来选择运行模式。 88E1111集成的MDIO模块与EMAC的MDIO接口相连接,可将方便网络控制端读取物理芯片状态寄存器,达到实时监测的效果。

3 硬件接口设计

本文设计的任务是基于C6678片内以太网交换子系统和片外PHY芯片88E1111及其外围电路的接口设计。主要包括:C6678与88E1111芯片连接、88E1111芯片配置以及88E1111芯片与网络介质连接。

3.1 C6678与88E1111芯片连接

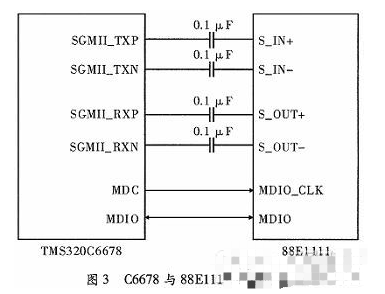

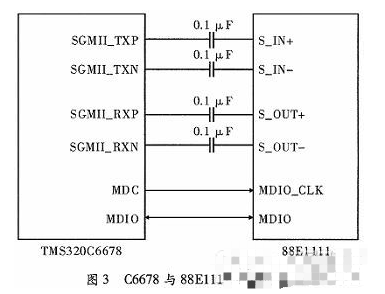

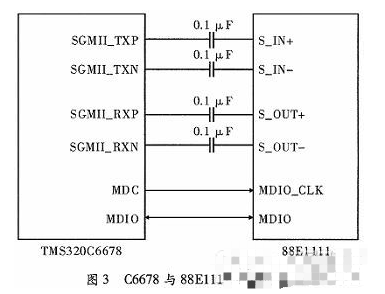

C6678和PHY芯片88E1111的接口电路如图3所示。88E1111工作在SGMII接口模式下,不需要TXCLK时钟输入,更有助于减少电路板上走线的数量,同时也可减少噪声的产生。

主要的接口信号包括时钟和数据信号如下:

MDIO_CLK:管理数据时钟。该时钟信号由C6678片上的MDIO模块提供,该时钟频率通过配置MDIO的控制寄存器CONTROL中的CLKDIV位来控制实现。

SGMII_TXP和SGMII_TXN:串行发送差分数据线。连接DSP内部SerDes和物理芯片的S_IN管脚,DSP的SerDes通过该管脚向物理层发送串行数据,数据中包含发送数据时钟信号。

SGMII_RXP和SGMII_RXN:串行接收差分数据线。连接DSP内部SerDes和物理芯片的S_OUT管脚,物理层芯片通过该接口将数据传送到DSP的SerDes,数据中包含数据接收时钟信号。

MDIO:管理数据I/O。可最多连接32个PHY设备到DSP的EMAC,并且可以枚举所有PHY设备,读取PHY设备状态寄存器来监测PHY的连接状态。数据帧结构符合802.3标准,包含读写指令、PHY地址、寄存器地址和数据等。

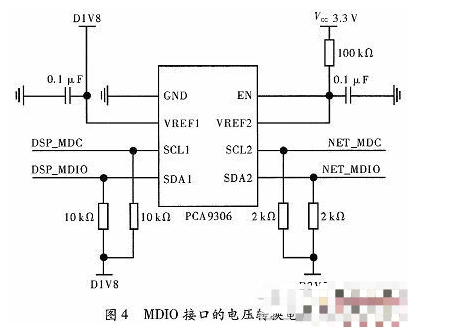

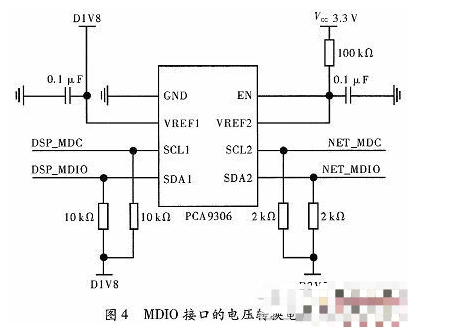

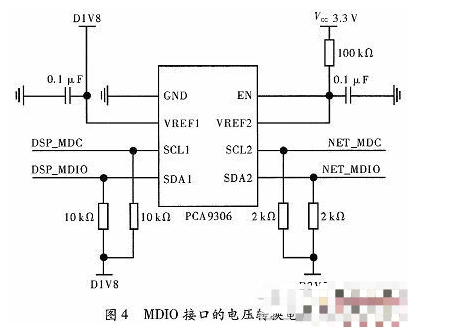

因为88E1111上集成的MDIO与C6678集成MDIO模块进行连接时,电压有所差别,前者电压为2.5 V,后者电压为1.8 V,所以在二者之间应该添加电压转换器。本文采用一片PCA9306,实现2.5 V和1.8 V之间的电平转换,其连接电路如图4所示。

3.2 88E1111芯片配置

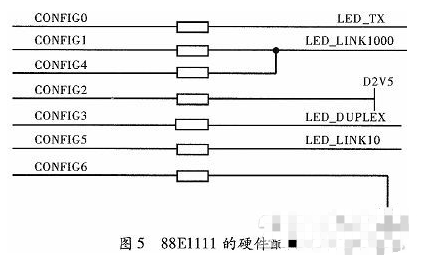

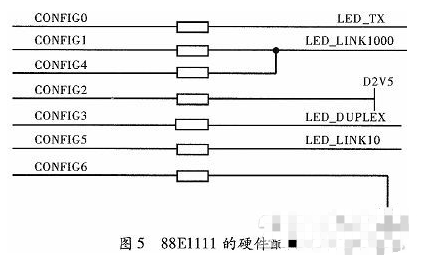

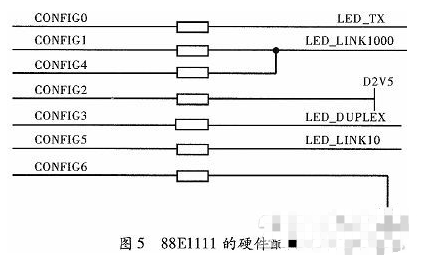

88E1111与C6678的MDIO模块相连接,MDIO最多可识别32个物理芯片,在使用物理芯片之前需要对其进行配置,配置内容主要包括芯片的地址、模式等。配置CONFTG[6:0]管脚定义可查询文献,本文配置的硬件电路如图5所示,图5中可以不使用电阻,本文为了测试方便,加一个0 Ω的电阻。

88E1111硬件配置完成后,系统将固定为一种接口方式,按照文献的定义,物理芯片的地址为:PHY_ADDRESS=0’b00001,芯片模式为:不带时钟,自动协商的SGMII模式。

3.3 88E1111芯片与RJ45连接

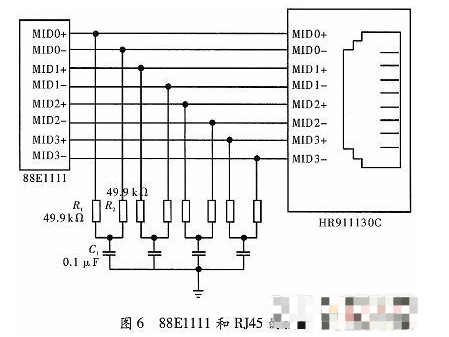

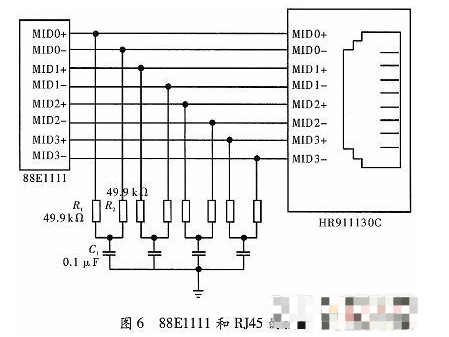

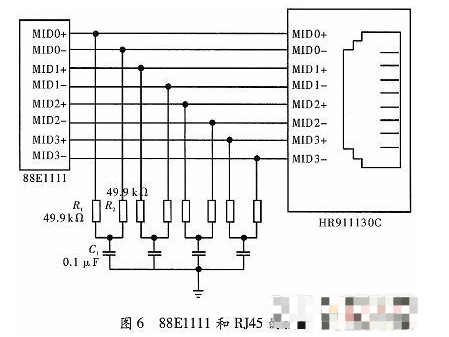

88E1111和网络介质之间无法直接连接,因传输速度在千兆级,所以更加需要设计合适的网络隔离变压器来降低传输损耗、回音和串扰。本文选择千兆网口插座HR911130C,该插座内部自带变压器电路,只需在外部连接滤波网络便可实现网络信号稳定地传输,如图6所示。88E1111和 HR9111130C采用差分连接,在PCB布线时需要严格等长,且一般还需使用阻抗匹配网络,如图6中的R1和C1。

4 软件程序设计

TI针对网络开发发布了网络开发套件(Network Development Kit,NDK),能将多个模块的配置操作交给NDK网络框架实现,同时数据分包和解析也无需程序员过多考虑,加速了网络开发进程。NDK构建在实时操作系统SYS/BIOS之上,NDK通过OS抽象层与BIOS进行交互,同时BIOS的cfg配置文件能对NDK各模块进行可视化查看。

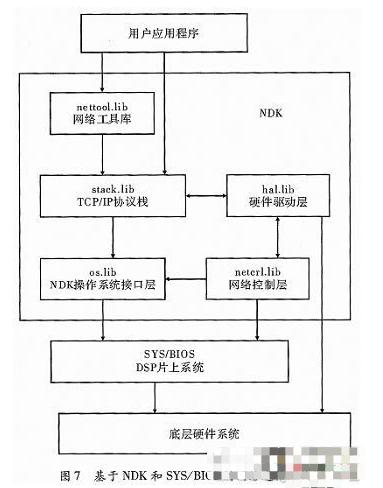

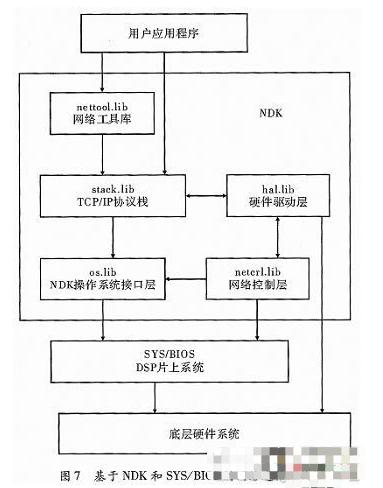

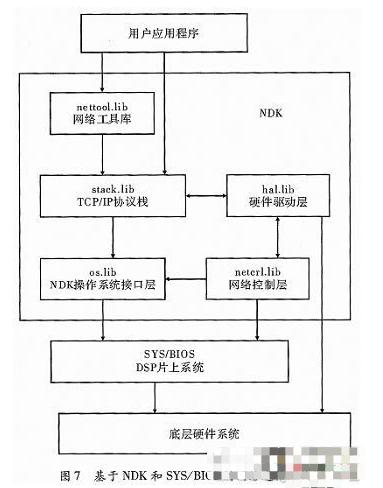

本文基于多核DSP实时操作系统SYS/BIOS上,设计了以太网通信程序。该操作系统能够提供较多的集成模块,方便用户编写程序,且还有软硬件中断管理、多任务同步机制、多核通信机制和存储器管理机制等,可为用户进行多线程多任务开发提供模块化的框架。以太网通信接口的软件总体结构如图7所示。

SYS/BIOS为整个软件提供集成开发环境,不仅拥有适合实时系统的多线程优先抢占机制,还可添加需要的封装库,使得编写程序时可以更加方便地调用库函数。NDK是DSP的网络程序开发集成工具,其中,stack.lib给出了从顶层socket到底层PPP关于TCP/IP协议栈的封装库;nettool.lib提供用于socket网络套接字和用于网络应用开发工具的封装库;os.lib提供应用于SYS/BIOS和网络编程套件之间的系统协调的封装库;hal.lib提供外围设备和网协议栈之间接口的封装库;netctrl.lib提供DSP网络编程的整体控制,可用来配置底层驱动和协议。

本文DSP片上系统软件分为3部分:SYS/BIOS平台和NDK的TCP/IP协议栈建立和配置;用户程序;编制底层驱动程序。

4.1 底层硬件驱动的实现

NDK的基本结构如图7所示,可看出NDK开发套件与用户程序、SYS/BIOS操作系统和底层硬件都有密切的联系。NDK中网络控制层和操作系统接口层与SYS/BIOS系统相连接,NDK的硬件驱动层用于控制底层硬件驱动的配置,这些操作和配置均可在网络工具库中找到相应的驱动函数,并可直接由用户应用程序来调用实现。

这些功能主要包括:

(1)底层硬件驱动包括:MDIO模块和EMAC模块的初始化HY芯片搜索配置和状态监测;EMAC/MDIO中断使能。(2)TCP/IP协议栈的建立,配置接收和发送缓存区的大小,完成以太网数据的收发任务。(3)利用MDIO模块,根据MDIO读取的PHY状态寄存器来监测其连接状态,识别可以是CPU产生中断的状态变化事件,并将信息反馈。(4)关闭驱动,复位前面对寄存器进行的操作,收回占用资源。

如图7所示,硬件驱动包含在硬件驱动层hal.lib中,用户需要对按照系统对驱动函数进行修改。C6000系列NDK的API封装了许多固定的驱动函数,具有特定的功能,比如_llPacketSerivceCheck()的作用是检测以太网数据包的结构,且将检测到的结构信息反馈给协议栈进行分析处理。具体的驱动程序需要按照硬件系统的配置来进行设计,在C6678中,可在集成度较高的片上系统直接对网络通信模块的寄存器进行配置查询,就可以完成硬件底层驱动,使得底层硬件能够有效地运行。

4.2 DSP端网络应用程序

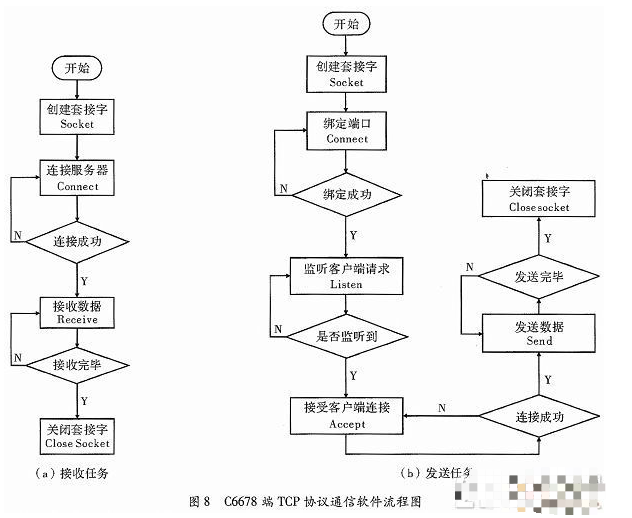

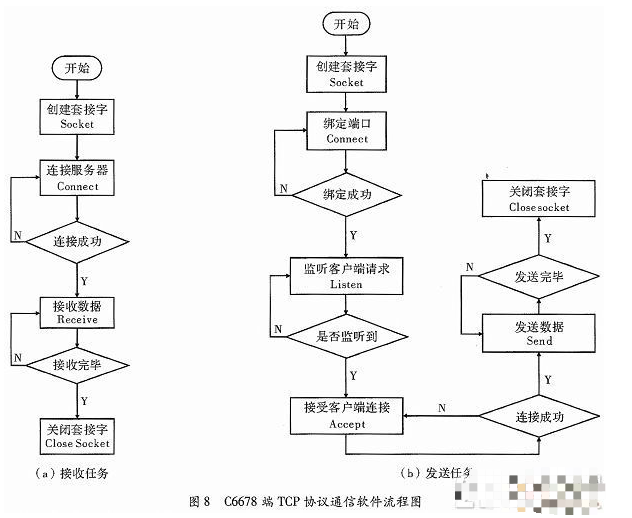

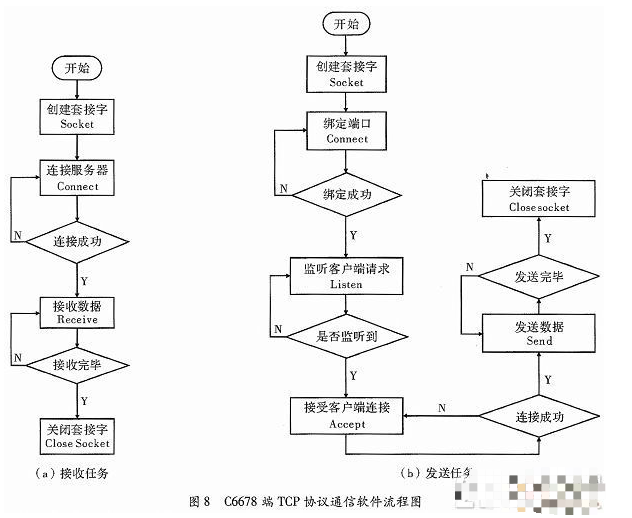

DSP软件设计是基于SYS/BIOS实时多任务操作系统和C语言,采用Socket套接字,创建TCP/IP客户端(Client)和服务器端 (Server),Client负责与外部设备服务器端建立连接并接收数据包,Server用来向PC机发送处理后的数据包。接收任务和发送任务流程如图 8所示。在C6678的内核Core0中建立两个同步线程任务,即数据接收和发送任务,分别用来接收TCP服务器发送过来的数据和发送处理后的数据到PC 上位机中进行处理、存储和显示。

4.3 上位机测试程序

上位机测试程基于VC++的MFC界面设计,使用套接字Socket进行网络编程。程序中需设计两个同步线程,用来实现数据的实时接收和动态显示功能。使用TCP服务器端发送船体结构应力数据,经过DSP的接接收、处理和发送过程,最后发送到PC上位机进行数据动态显示,结果如图9所示。

5 结束语

本文以8核处理器C6678为核心,对片上集成的以太网交换子系统接口硬件进行了研究,按照接口的特点设计了包括以太网交换子系统和物理芯片的接口连接、物理芯片与网络介质接口连接的硬件系统,并完成了千兆以太网驱动,最终实现多核DSP C6678与上位机进行千兆以太网通信。通过与上位机进行网络通信测试,结果显示以太网数据通信接口能实时高效地进行网络数据传输。

随着DSP处理器在现代工业的应用越来越广泛,DSP的功能不仅只有快速运算处理,还需要与其他处理器或者设备之间进行实时数据交换,以实现资源的共享。因此,针对不同设备的需求,选择稳定、快速和高效率的接口方式在当今数字信号处理系统设计中关键的组成部分。

TI公司的8核处理器TMS320C6678(以下简称C6678)提供丰富的片上接口资源用于处理器与外设之间的通信,这些接口都可以用于DSP与外设之间的通信,但是灵活性有差异,使用SGMII接口来实现千兆以太网通信,可使得通信接口一般化,能够适用于众多的设备连接。本文针对C6678的芯片特点以及含有的接口资源,设计实现了千兆以太网通信,主要设计了以太网接口电路、网络底层硬件驱动、TCP/IP协议的用户程序,并完成了与上位机以太网通信测试,实现了数字信号高速有效地网络传输。

1 C6678以太网交换子系统

C6678是基于KeyStone I构架的8核高性能、定点/浮点处理器,单核最高工作频率可达1.25 GHz。C6678的以太网交换子系统包括2个以太网媒体访问控制(Ethernet Media Access Controller,EMAC)、2个SGMII、1个管理数据输入输出(Management Data Input Output,MDIO)、3-Port以太网交换模块以及网络配置总线,其网络交换子系统如图1所示。

EMAC的作用是将交换子系统的内部信号转换为GMII信号传递给SGMII模块;MDIO控制物理层芯片执行对多数据流的控制输入输出。

2 PHY芯片88E1111

本文选择C6678作为主芯片,由于C6678的千兆网络交换子系统只支持SGMII接口,所以本文选择对SGMII接口的网络数据传输具有较好兼容性的物理芯片88E1111。88E1111芯片的内部结构如图2所示。

88E1111的介质接口有铜介质接口和光纤接口。铜介质接口为MDI[3:0],通过设置HWCFG_MODE[3:0]来选择运行模式。 88E1111集成的MDIO模块与EMAC的MDIO接口相连接,可将方便网络控制端读取物理芯片状态寄存器,达到实时监测的效果。

3 硬件接口设计

本文设计的任务是基于C6678片内以太网交换子系统和片外PHY芯片88E1111及其外围电路的接口设计。主要包括:C6678与88E1111芯片连接、88E1111芯片配置以及88E1111芯片与网络介质连接。

3.1 C6678与88E1111芯片连接

C6678和PHY芯片88E1111的接口电路如图3所示。88E1111工作在SGMII接口模式下,不需要TXCLK时钟输入,更有助于减少电路板上走线的数量,同时也可减少噪声的产生。

主要的接口信号包括时钟和数据信号如下:

MDIO_CLK:管理数据时钟。该时钟信号由C6678片上的MDIO模块提供,该时钟频率通过配置MDIO的控制寄存器CONTROL中的CLKDIV位来控制实现。

SGMII_TXP和SGMII_TXN:串行发送差分数据线。连接DSP内部SerDes和物理芯片的S_IN管脚,DSP的SerDes通过该管脚向物理层发送串行数据,数据中包含发送数据时钟信号。

SGMII_RXP和SGMII_RXN:串行接收差分数据线。连接DSP内部SerDes和物理芯片的S_OUT管脚,物理层芯片通过该接口将数据传送到DSP的SerDes,数据中包含数据接收时钟信号。

MDIO:管理数据I/O。可最多连接32个PHY设备到DSP的EMAC,并且可以枚举所有PHY设备,读取PHY设备状态寄存器来监测PHY的连接状态。数据帧结构符合802.3标准,包含读写指令、PHY地址、寄存器地址和数据等。

因为88E1111上集成的MDIO与C6678集成MDIO模块进行连接时,电压有所差别,前者电压为2.5 V,后者电压为1.8 V,所以在二者之间应该添加电压转换器。本文采用一片PCA9306,实现2.5 V和1.8 V之间的电平转换,其连接电路如图4所示。

3.2 88E1111芯片配置

88E1111与C6678的MDIO模块相连接,MDIO最多可识别32个物理芯片,在使用物理芯片之前需要对其进行配置,配置内容主要包括芯片的地址、模式等。配置CONFTG[6:0]管脚定义可查询文献,本文配置的硬件电路如图5所示,图5中可以不使用电阻,本文为了测试方便,加一个0 Ω的电阻。

88E1111硬件配置完成后,系统将固定为一种接口方式,按照文献的定义,物理芯片的地址为:PHY_ADDRESS=0’b00001,芯片模式为:不带时钟,自动协商的SGMII模式。

3.3 88E1111芯片与RJ45连接

88E1111和网络介质之间无法直接连接,因传输速度在千兆级,所以更加需要设计合适的网络隔离变压器来降低传输损耗、回音和串扰。本文选择千兆网口插座HR911130C,该插座内部自带变压器电路,只需在外部连接滤波网络便可实现网络信号稳定地传输,如图6所示。88E1111和 HR9111130C采用差分连接,在PCB布线时需要严格等长,且一般还需使用阻抗匹配网络,如图6中的R1和C1。

4 软件程序设计

TI针对网络开发发布了网络开发套件(Network Development Kit,NDK),能将多个模块的配置操作交给NDK网络框架实现,同时数据分包和解析也无需程序员过多考虑,加速了网络开发进程。NDK构建在实时操作系统SYS/BIOS之上,NDK通过OS抽象层与BIOS进行交互,同时BIOS的cfg配置文件能对NDK各模块进行可视化查看。

本文基于多核DSP实时操作系统SYS/BIOS上,设计了以太网通信程序。该操作系统能够提供较多的集成模块,方便用户编写程序,且还有软硬件中断管理、多任务同步机制、多核通信机制和存储器管理机制等,可为用户进行多线程多任务开发提供模块化的框架。以太网通信接口的软件总体结构如图7所示。

SYS/BIOS为整个软件提供集成开发环境,不仅拥有适合实时系统的多线程优先抢占机制,还可添加需要的封装库,使得编写程序时可以更加方便地调用库函数。NDK是DSP的网络程序开发集成工具,其中,stack.lib给出了从顶层socket到底层PPP关于TCP/IP协议栈的封装库;nettool.lib提供用于socket网络套接字和用于网络应用开发工具的封装库;os.lib提供应用于SYS/BIOS和网络编程套件之间的系统协调的封装库;hal.lib提供外围设备和网协议栈之间接口的封装库;netctrl.lib提供DSP网络编程的整体控制,可用来配置底层驱动和协议。

本文DSP片上系统软件分为3部分:SYS/BIOS平台和NDK的TCP/IP协议栈建立和配置;用户程序;编制底层驱动程序。

4.1 底层硬件驱动的实现

NDK的基本结构如图7所示,可看出NDK开发套件与用户程序、SYS/BIOS操作系统和底层硬件都有密切的联系。NDK中网络控制层和操作系统接口层与SYS/BIOS系统相连接,NDK的硬件驱动层用于控制底层硬件驱动的配置,这些操作和配置均可在网络工具库中找到相应的驱动函数,并可直接由用户应用程序来调用实现。

这些功能主要包括:

(1)底层硬件驱动包括:MDIO模块和EMAC模块的初始化HY芯片搜索配置和状态监测;EMAC/MDIO中断使能。(2)TCP/IP协议栈的建立,配置接收和发送缓存区的大小,完成以太网数据的收发任务。(3)利用MDIO模块,根据MDIO读取的PHY状态寄存器来监测其连接状态,识别可以是CPU产生中断的状态变化事件,并将信息反馈。(4)关闭驱动,复位前面对寄存器进行的操作,收回占用资源。

如图7所示,硬件驱动包含在硬件驱动层hal.lib中,用户需要对按照系统对驱动函数进行修改。C6000系列NDK的API封装了许多固定的驱动函数,具有特定的功能,比如_llPacketSerivceCheck()的作用是检测以太网数据包的结构,且将检测到的结构信息反馈给协议栈进行分析处理。具体的驱动程序需要按照硬件系统的配置来进行设计,在C6678中,可在集成度较高的片上系统直接对网络通信模块的寄存器进行配置查询,就可以完成硬件底层驱动,使得底层硬件能够有效地运行。

4.2 DSP端网络应用程序

DSP软件设计是基于SYS/BIOS实时多任务操作系统和C语言,采用Socket套接字,创建TCP/IP客户端(Client)和服务器端 (Server),Client负责与外部设备服务器端建立连接并接收数据包,Server用来向PC机发送处理后的数据包。接收任务和发送任务流程如图 8所示。在C6678的内核Core0中建立两个同步线程任务,即数据接收和发送任务,分别用来接收TCP服务器发送过来的数据和发送处理后的数据到PC 上位机中进行处理、存储和显示。

4.3 上位机测试程序

上位机测试程基于VC++的MFC界面设计,使用套接字Socket进行网络编程。程序中需设计两个同步线程,用来实现数据的实时接收和动态显示功能。使用TCP服务器端发送船体结构应力数据,经过DSP的接接收、处理和发送过程,最后发送到PC上位机进行数据动态显示,结果如图9所示。

5 结束语

本文以8核处理器C6678为核心,对片上集成的以太网交换子系统接口硬件进行了研究,按照接口的特点设计了包括以太网交换子系统和物理芯片的接口连接、物理芯片与网络介质接口连接的硬件系统,并完成了千兆以太网驱动,最终实现多核DSP C6678与上位机进行千兆以太网通信。通过与上位机进行网络通信测试,结果显示以太网数据通信接口能实时高效地进行网络数据传输。

举报

举报

举报

举报