时钟速度的提高和更严格的信号时序增加了对精准的高频模块的需求。PLL(锁相环)基于输入信号生成高频输出信号,是一种备受欢迎的用于产生高频信号的电路。当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。因此,需要非常精确地加以测量。

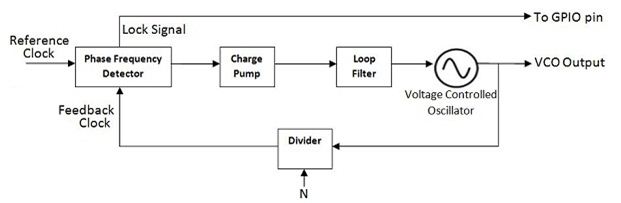

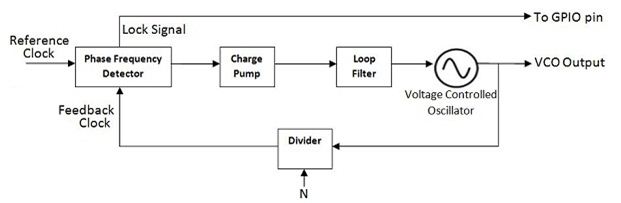

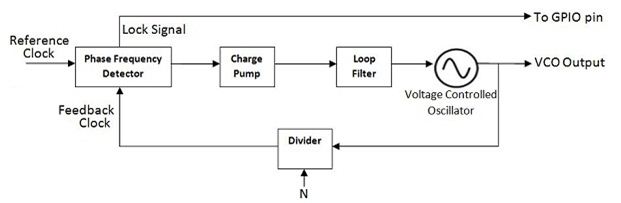

图1 显示了PLL及其组件的简化框图。

图1 在锁相环中,VCO信号被划分并发回与参考信号进行比较。

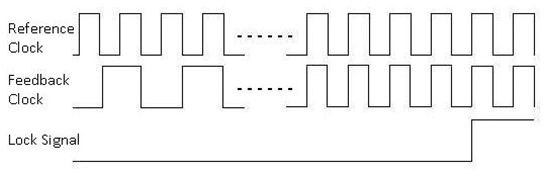

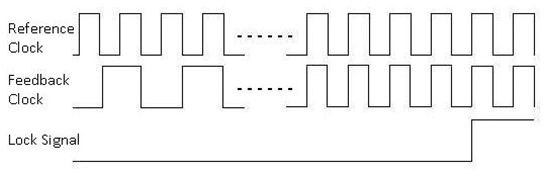

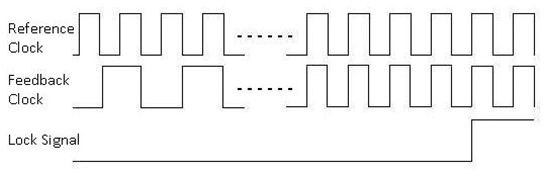

PLL锁定时间是通电后,PLL需要与相匹配(PLL参考时钟和PLL反馈时钟之间)产生目标频率的时间。图2 显示在反馈时钟和参考时钟的频率相同时,锁定信号为高。

图2 反馈时钟和参考时钟的频率相同时,PLL锁定信号为高

PLL的设计通常采用一种方式,让锁定时间尽可能短,同时仍然提供尽可能高的稳定性。取决于参考频率的范围,实现锁定状态所花费的时间有所不同,如图3。

图3 锁定时间行为与参考频率关系是线性正比的。

你可以根据可用资源使用以下任何方法。

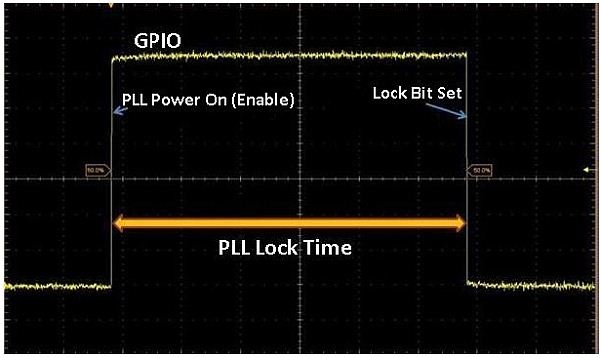

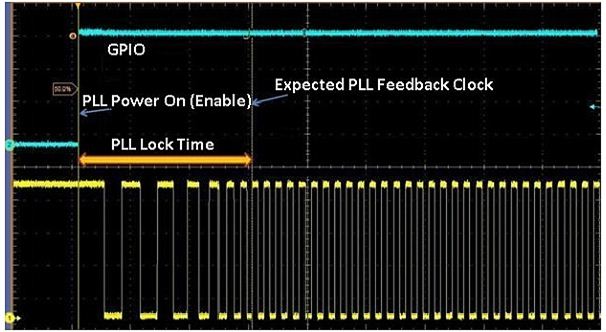

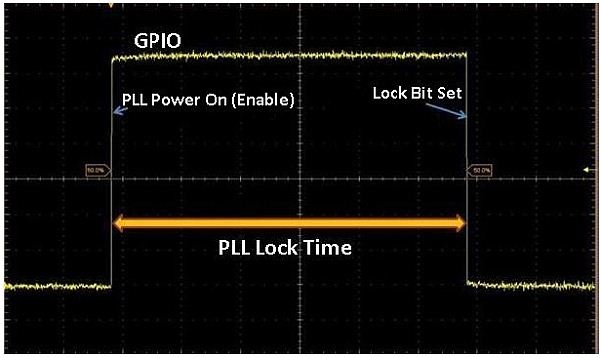

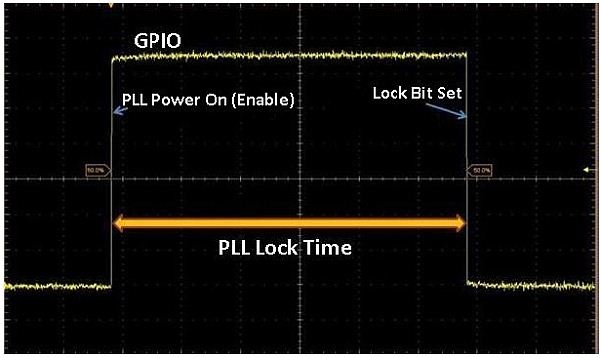

方法1:PLL电源开启,锁定位断言/去断言

PLL电源开启时,GPIO(通用输入输出)引脚翻转。然后,锁定位轮询检查锁定状态是否已经实现。当锁定位被断言/去断言时,相同的GPIO引脚再次触发,如图4。该GPIO的脉冲宽度就是PLL锁定时间。如果无法访问PLL时钟输出,可以使用这一方法。

图4 PLL电源开启到锁定位断言/去断言

不幸的是,这种方法不是很精确,因为在锁位设置后,有一定锁定时间的设计裕量。

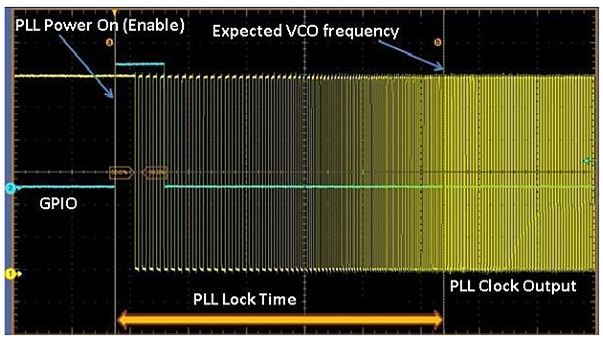

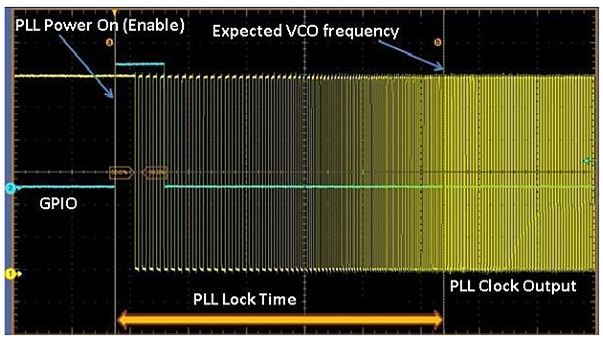

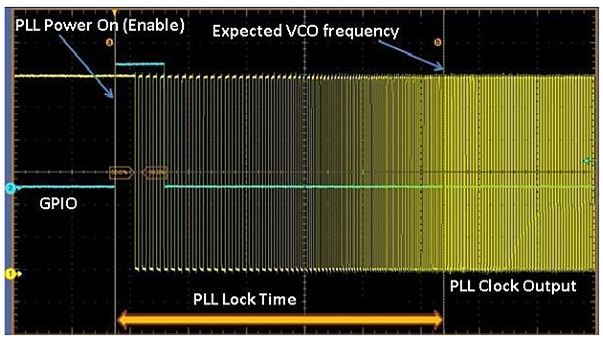

方法2:PLL电源开启到预期VCO时钟输出

如果PLL VCO(压控振荡器)的时钟输出垫没有锁位门控(不论PLL锁定位处于何种状态,时钟输出垫都驱动VCO时钟),则此方法会奏效。由于VCO时钟输出垫没有锁位门控,我们可以直接观察VCO输出。在此方法中,我们测量PLL电源开启时间到获得所需VCO输出频率的时间之间的时间间隔,如图5。这个时间就是锁定时间。

可以通过手动放置每个循环的光标,直到观察到恒定频率,从而测量示波器所需的PLL频率输出。

图5 在这个应用中,锁定时间是PLL电源开启到预期VCO时钟输出时间。

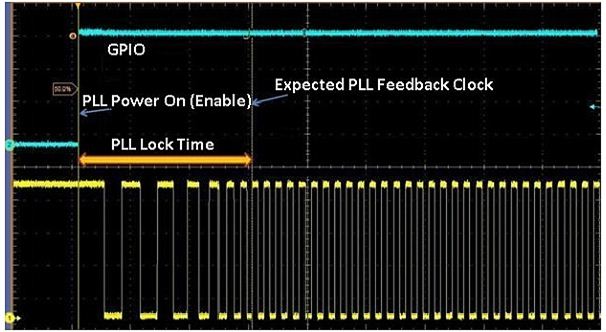

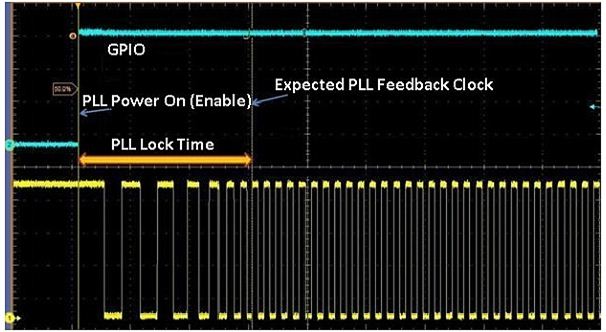

方法3:PLL电源开启到预期PLL反馈时钟输出

如果PLL VCO(压控振荡器)时钟输出垫有锁位门控(时钟输出垫只有在获得PLL锁定时方驱动VCO时钟),并且不论PLL锁定位状态如何,时钟输出垫都有反馈时钟信号,则可使用这一方法。在这个方法中,测量的是PLL电源开启到其所需的反馈频率(同基准频率)时间之间所花的时间,如图6。这个时间就是锁定时间。

图6 PLL锁定时间为PLL电源开启到预期PLL反馈时钟输出的时间。

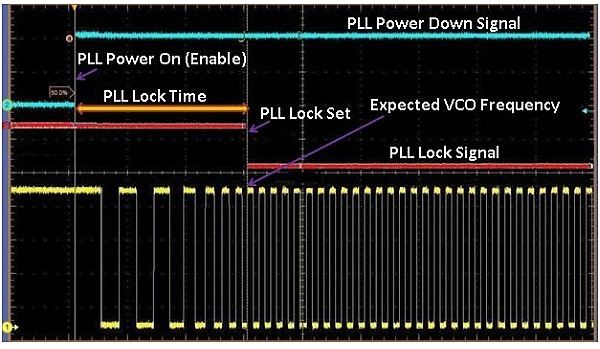

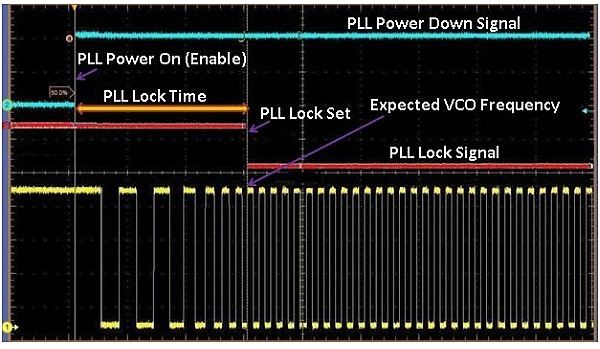

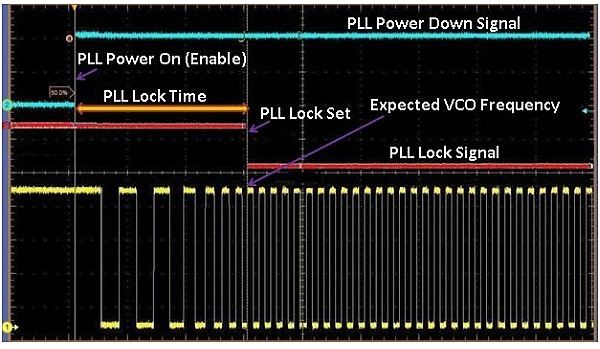

方法4:PLL电源开启到锁定垫断言/去断言

如果PLL VCO时钟输出垫有锁位门控,就无法选择让PLL反馈时钟信号到垫上,但锁定垫可以用硅,就可以使用这个方法。在这里,测量的是PLL电源开启的时间,和锁定垫被断言/解除断言的时间,如图 7(在此,板上的可用锁定垫受到监控,锁定位不用GPIO轮询)。这个时间是锁定时间。这种方法是精准的,因为锁定信号直接来自PFD,因此没有附加的延迟。

图7.PLL锁定时间是PLL上电锁定垫断言/去断言的函数。在这种情况下,你只需要在示波器上观察PLL断电信号和PLL锁定信号。这里显示的时钟仅供参考。)

我们已经讨论了取决于设计局限性的测量PLL锁定时间的不同方法。方法4到方法3到方法2到方法1对PLL锁定时间测量的精度是递降的。因此,如果所有的资源都可用,我们推荐采用方法4进行PLL锁定时间的测量。

时钟速度的提高和更严格的信号时序增加了对精准的高频模块的需求。PLL(锁相环)基于输入信号生成高频输出信号,是一种备受欢迎的用于产生高频信号的电路。当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。因此,需要非常精确地加以测量。

图1 显示了PLL及其组件的简化框图。

图1 在锁相环中,VCO信号被划分并发回与参考信号进行比较。

PLL锁定时间是通电后,PLL需要与相匹配(PLL参考时钟和PLL反馈时钟之间)产生目标频率的时间。图2 显示在反馈时钟和参考时钟的频率相同时,锁定信号为高。

图2 反馈时钟和参考时钟的频率相同时,PLL锁定信号为高

PLL的设计通常采用一种方式,让锁定时间尽可能短,同时仍然提供尽可能高的稳定性。取决于参考频率的范围,实现锁定状态所花费的时间有所不同,如图3。

图3 锁定时间行为与参考频率关系是线性正比的。

你可以根据可用资源使用以下任何方法。

方法1:PLL电源开启,锁定位断言/去断言

PLL电源开启时,GPIO(通用输入输出)引脚翻转。然后,锁定位轮询检查锁定状态是否已经实现。当锁定位被断言/去断言时,相同的GPIO引脚再次触发,如图4。该GPIO的脉冲宽度就是PLL锁定时间。如果无法访问PLL时钟输出,可以使用这一方法。

图4 PLL电源开启到锁定位断言/去断言

不幸的是,这种方法不是很精确,因为在锁位设置后,有一定锁定时间的设计裕量。

方法2:PLL电源开启到预期VCO时钟输出

如果PLL VCO(压控振荡器)的时钟输出垫没有锁位门控(不论PLL锁定位处于何种状态,时钟输出垫都驱动VCO时钟),则此方法会奏效。由于VCO时钟输出垫没有锁位门控,我们可以直接观察VCO输出。在此方法中,我们测量PLL电源开启时间到获得所需VCO输出频率的时间之间的时间间隔,如图5。这个时间就是锁定时间。

可以通过手动放置每个循环的光标,直到观察到恒定频率,从而测量示波器所需的PLL频率输出。

图5 在这个应用中,锁定时间是PLL电源开启到预期VCO时钟输出时间。

方法3:PLL电源开启到预期PLL反馈时钟输出

如果PLL VCO(压控振荡器)时钟输出垫有锁位门控(时钟输出垫只有在获得PLL锁定时方驱动VCO时钟),并且不论PLL锁定位状态如何,时钟输出垫都有反馈时钟信号,则可使用这一方法。在这个方法中,测量的是PLL电源开启到其所需的反馈频率(同基准频率)时间之间所花的时间,如图6。这个时间就是锁定时间。

图6 PLL锁定时间为PLL电源开启到预期PLL反馈时钟输出的时间。

方法4:PLL电源开启到锁定垫断言/去断言

如果PLL VCO时钟输出垫有锁位门控,就无法选择让PLL反馈时钟信号到垫上,但锁定垫可以用硅,就可以使用这个方法。在这里,测量的是PLL电源开启的时间,和锁定垫被断言/解除断言的时间,如图 7(在此,板上的可用锁定垫受到监控,锁定位不用GPIO轮询)。这个时间是锁定时间。这种方法是精准的,因为锁定信号直接来自PFD,因此没有附加的延迟。

图7.PLL锁定时间是PLL上电锁定垫断言/去断言的函数。在这种情况下,你只需要在示波器上观察PLL断电信号和PLL锁定信号。这里显示的时钟仅供参考。)

我们已经讨论了取决于设计局限性的测量PLL锁定时间的不同方法。方法4到方法3到方法2到方法1对PLL锁定时间测量的精度是递降的。因此,如果所有的资源都可用,我们推荐采用方法4进行PLL锁定时间的测量。

举报

举报

举报

举报