在众多的语音编译码调制中,连续可变斜率增量调制(CVSD)作为许多增量调制中的一种,只需编一位码,在发送端与接收端之间不需要码型同步,量阶△的大小能自动地跟踪信号变化,因而具有强抗误码能力,在10-3时仍可保持高质量的话音。目前市场上有CVSD的专用芯片,但专用芯片的通用性、灵活性和可扩展性受到了很大的限制,并且产品的开发周期长,开发成本也较高。专用CVSD芯片只能实现一路编译码,在需要多路CVSD编译码时则需要很多专用芯片,具有局限性;而单片FPGA容易实现多路CVSD编译码功能。此外如果专用芯片停产或者买不到,已有的通信设备维修将会因器件缺乏导致后续工作无法开展。为了弥补专用CVSD芯片的不足,同时也方便在现场可编程门阵列(FPGA)中增加一些其他相关的应用功能,因此在FPGA中实现CVSD语音编译码调制功能的前景将是非常广阔的。

这里将详细介绍基于FPGA的CVSD语音编译码的设计思路、具体实现以及和专用芯片CMX639之间的互相通信。

1 CVSD工作原埋

CVSD是一种量阶△随着输入语音信号平均斜率(斜率绝对值的平均值)大小而连续变化的增量调制方式。它的工作原理如下:用多个连续可变斜率的折线来逼近语音信号,当折线斜率为正时,对应的数字编码为“1”;当折线斜率为负时,对应的数字编码为“0”。

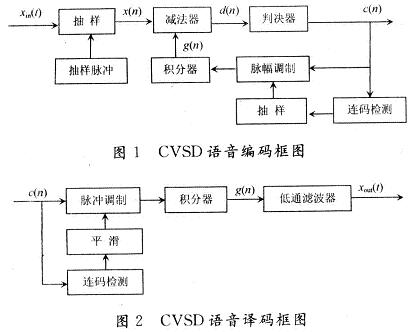

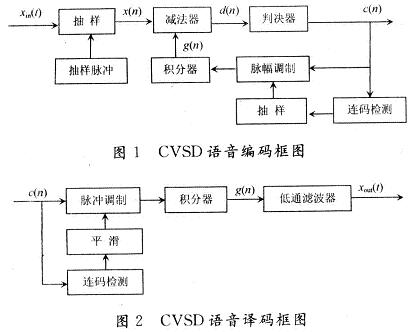

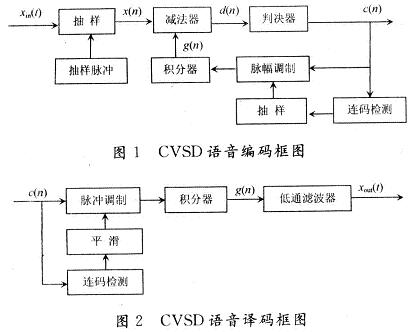

当CVSD工作于编码方式时,其系统框图如图1所示。语音信号xin(t)经采样得到数字信号x(n),数字信号x(n)与积分器输出信号g(n)比较后输出误差信号d(n),误差信号d(n)经判决后输出数字编码c(n),同时该信号作为积分器输出斜率的极性控制信号和积分器输出斜率大小逻辑的输入信号。在每个时钟周期内,若语音信号大于积分器输出信号,则判决输出为“1”,积分器输出上升一个量阶△;若语音信号小于积分器输出信号,则判决输出为“0”,积分器输出下降一个量阶△。当CVSD工作于译码方式时,其系统框图如图2所示。在每个时钟周期内,数字编码c(n)被送到连码检测器,然后送到平滑电路以控制积分器输出斜率的大小。若数字编码c(n)输入为“1”,则积分器的输出上升一个量阶△,若数字输入为“O”,则积分器的输出下降一个量阶△,这相当于编码过程的逆过程。积分器的输出g(n)通过低通滤波器平滑滤波后将重现输入语音信号xout(t)。可见输入信号的波形上升越快,输出的连“1”码就越多,同样下降越快,输出的连“O”码越多,CVSD编译码能够很好地反映输入信号的斜率大小,有效地避免了斜率过载失真和颗粒失真。为使积分器的输出能够更好地逼近输入语音信号,量阶△随着输入信号斜率大小而变化,当信号斜率绝对值很大,编码出现3个或4个连“l”或连“O”码时,则量阶△加一个增量△0;当不出现上述码型时,量阶△则相应地减少。

2 CVSD的软件算法

2.1 CVSD的编码算法

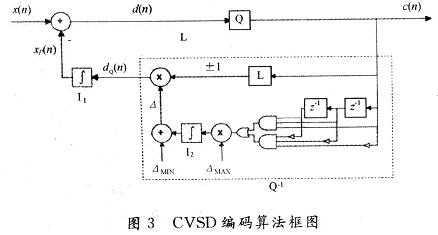

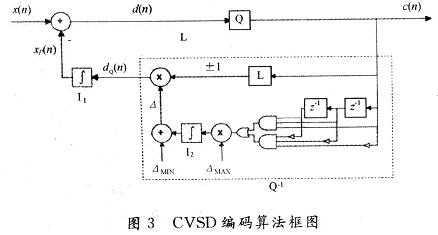

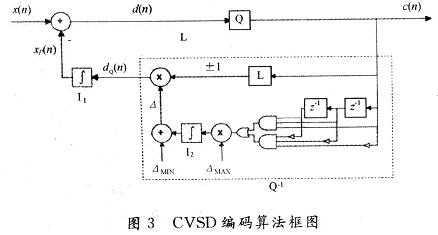

图3是CVSD编码算法框图,其量阶△调整是基于前3位的连码。x(n)是语音经过采样得到的数字信号,数字信号x(n)与积分器地I1输出的预测信号xp(n)经过比较后输出误差信号d(n),误差信号d(n)经一阶量化(d(n)≥0,c(n)=1;d(n)<0,c(n)=O)得到输出的数字编码c(n),该信号同时作为积分器I2的极性控制信号和控制积分器I2输出斜率大小逻辑的输入信号。当输出码出现连续的“1”码或者连续的“0”码,则说明信号波形的斜率较大,因此量阶△需要适当增加,当输出码c(n)长时间没有出现连码,则积分器I2向“O”值方向衰减,量阶△减小。最小和最大阶距是由△MIN和△MAX分别确定的。当长时间没有出现连码,CVSD编码器退化为一个线性增量调制(LDM)编码器。

2.2 CVSD的译码算法

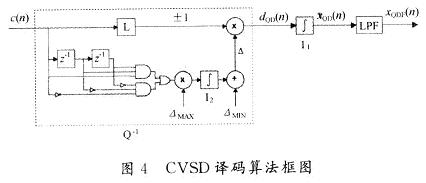

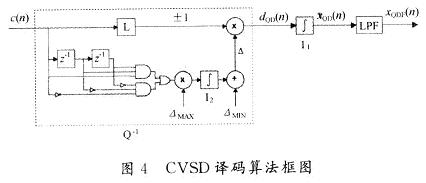

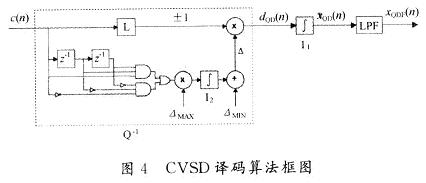

图4是CVSD译码算法框图,其量阶调整是基于前3位的连码。译码过程就是编码的逆过程,只是在积分器I1后面增加了一个低通滤波器,用于抑制带外干扰。

3 CVSD算法在FPGA中的实现

3.1 硬件实现框图

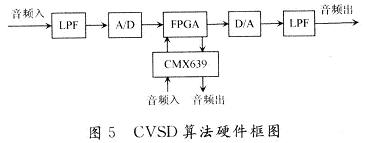

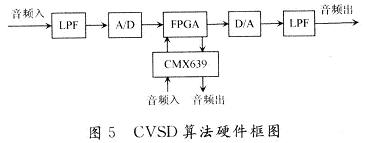

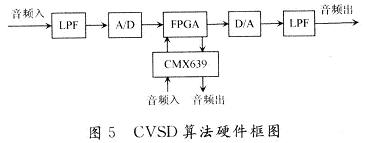

考虑到实际需求,采用了通用性较强的A/D,D/A元器件和FPGA器件。该硬件可以同时实现3路CVSD编译码算法,一路采用FPGA(XC3S1500)实现,两路采用专用芯片实现;同时编译码之间可以通过FPGA内部逻辑控制互相通信。在FPGA内设计实现了CVSD编译码算法,在该器件内融合多种控制功能,可以在线编程、方便调试。

音频信号在进行A/D采样之前,为了防止带外信号进入,首先进行低通滤波;再通过高倍时钟进行采样得到数字信号进入FPGA进行编译码处理。译码过后的信号通过D/A输出模拟信号,该信号再经过低通滤波器后输出,得到音频信号。

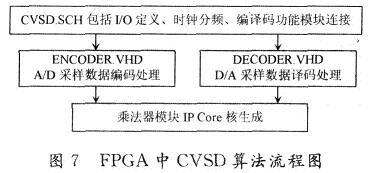

3.2 CVSD算法实现框图

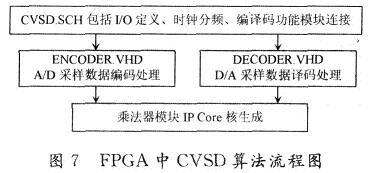

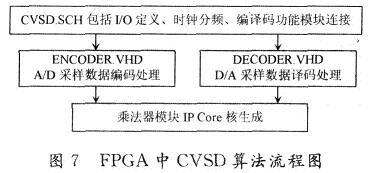

在FPGA内部算法实现上,采用了“自顶向下”的设计方法,即根据要求的功能先设计出顶层的原理图,该图由若干个功能模块组成。再把各个模块细化为子模块,各子模块的功能采用电路图实现,也可用硬件描述语言实现。设计中顶层采用原理图实现,子模块采用VHDL硬件描述语言实现,利用ISE自带的IP Core乘法器,经过综合和优化等过程,最终将程序下载到芯片中,使用在线逻辑分析仪ChipScope Pro进行逻辑和功能测试分析。

3.3 CVSD算法的仿真

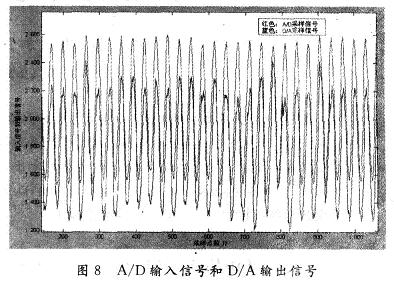

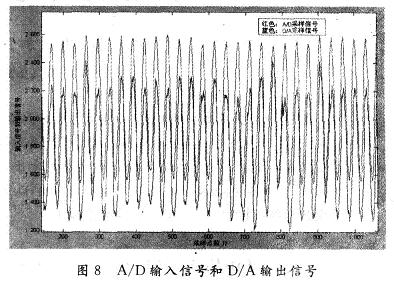

以正弦单音输入信号为例,利用信号源产生信号幅度O.5 Vpp,频率fin(t)=1 kHz的正弦信号作为测试信号,在FPGA中利用高倍时钟产生fs(t)=64 kHz的采样时钟。对输入A/D的音频信号采用专用低通滤波芯片进行了滤波。D/A输出的信号包含了许多不必要的高次谐波分量,因此也采用低通滤波器对其进行了平滑滤波。

在设计上,不仅仅是采用FPGA实现和验证自己的CVSD编译码算法,还和专用芯片CMX639进行互相通信进行验证。CMX639是一款CVSD全双工音频调制芯片,集成了编码和译码功能,实现了单芯片语音处理能力,外围设备简单,用户可以根据实际情况,自主选择采样速率。

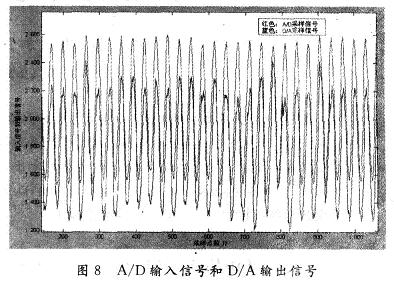

图8是通过ChipScope Pro采集的实时正弦信号。从图中可以看出量阶△的大小能够很好地反映输入信号斜率的大小,输出端输出信号能够很好地重现输入信号,说明CVSD编译码方式是有效的。

3.4 CVSD算法的实现

采用原理图和VHDL语言相结合的方式在FPGA中实现了CVSD电路。具体实现步骤如下:

(1)根据算法框图设计顶层原理图CVSD.SCH;

(2)利用IP Core产生底层所需要的乘法器;

(3)利用VHDL语言完成CVSD编译码模块;

(4)I/O管脚定义,约束条件编写;

(5)设计综合、编译;

(6)bit文件生成、下载,通过ChipScope Pro进行仿真测试;

(7)根据仿真测试结果返回修改设计,直到设计成功;

(8)mcs文件生成、加载,最终验证。

验证是FPGA设计中很重要的一环,只有通过验证才能说明设计的正确与否。采用XILINX公司的Spartan一3系列中的XC3S1500来具体实现CVSD的编译码功能。通过自己设计的编译码算法和CMX639专用芯片的编译码模块互相通信,输入实际语音信号测试,能够很好地从D/A输出语音信号,从CMX639译码输出也能听到语音信号,达到了满意的效果。

4 结 语

本文提出的FPGA设计方法很好地实现了CVSD编译码功能,充分利用了FPGA的优势,可以同时实现多路CVSD编译码功能,弥补了采用专用芯片实现CVSD编译码的不足,设计灵活、简单,成本低,具有很好的应用前景。

在众多的语音编译码调制中,连续可变斜率增量调制(CVSD)作为许多增量调制中的一种,只需编一位码,在发送端与接收端之间不需要码型同步,量阶△的大小能自动地跟踪信号变化,因而具有强抗误码能力,在10-3时仍可保持高质量的话音。目前市场上有CVSD的专用芯片,但专用芯片的通用性、灵活性和可扩展性受到了很大的限制,并且产品的开发周期长,开发成本也较高。专用CVSD芯片只能实现一路编译码,在需要多路CVSD编译码时则需要很多专用芯片,具有局限性;而单片FPGA容易实现多路CVSD编译码功能。此外如果专用芯片停产或者买不到,已有的通信设备维修将会因器件缺乏导致后续工作无法开展。为了弥补专用CVSD芯片的不足,同时也方便在现场可编程门阵列(FPGA)中增加一些其他相关的应用功能,因此在FPGA中实现CVSD语音编译码调制功能的前景将是非常广阔的。

这里将详细介绍基于FPGA的CVSD语音编译码的设计思路、具体实现以及和专用芯片CMX639之间的互相通信。

1 CVSD工作原埋

CVSD是一种量阶△随着输入语音信号平均斜率(斜率绝对值的平均值)大小而连续变化的增量调制方式。它的工作原理如下:用多个连续可变斜率的折线来逼近语音信号,当折线斜率为正时,对应的数字编码为“1”;当折线斜率为负时,对应的数字编码为“0”。

当CVSD工作于编码方式时,其系统框图如图1所示。语音信号xin(t)经采样得到数字信号x(n),数字信号x(n)与积分器输出信号g(n)比较后输出误差信号d(n),误差信号d(n)经判决后输出数字编码c(n),同时该信号作为积分器输出斜率的极性控制信号和积分器输出斜率大小逻辑的输入信号。在每个时钟周期内,若语音信号大于积分器输出信号,则判决输出为“1”,积分器输出上升一个量阶△;若语音信号小于积分器输出信号,则判决输出为“0”,积分器输出下降一个量阶△。当CVSD工作于译码方式时,其系统框图如图2所示。在每个时钟周期内,数字编码c(n)被送到连码检测器,然后送到平滑电路以控制积分器输出斜率的大小。若数字编码c(n)输入为“1”,则积分器的输出上升一个量阶△,若数字输入为“O”,则积分器的输出下降一个量阶△,这相当于编码过程的逆过程。积分器的输出g(n)通过低通滤波器平滑滤波后将重现输入语音信号xout(t)。可见输入信号的波形上升越快,输出的连“1”码就越多,同样下降越快,输出的连“O”码越多,CVSD编译码能够很好地反映输入信号的斜率大小,有效地避免了斜率过载失真和颗粒失真。为使积分器的输出能够更好地逼近输入语音信号,量阶△随着输入信号斜率大小而变化,当信号斜率绝对值很大,编码出现3个或4个连“l”或连“O”码时,则量阶△加一个增量△0;当不出现上述码型时,量阶△则相应地减少。

2 CVSD的软件算法

2.1 CVSD的编码算法

图3是CVSD编码算法框图,其量阶△调整是基于前3位的连码。x(n)是语音经过采样得到的数字信号,数字信号x(n)与积分器地I1输出的预测信号xp(n)经过比较后输出误差信号d(n),误差信号d(n)经一阶量化(d(n)≥0,c(n)=1;d(n)<0,c(n)=O)得到输出的数字编码c(n),该信号同时作为积分器I2的极性控制信号和控制积分器I2输出斜率大小逻辑的输入信号。当输出码出现连续的“1”码或者连续的“0”码,则说明信号波形的斜率较大,因此量阶△需要适当增加,当输出码c(n)长时间没有出现连码,则积分器I2向“O”值方向衰减,量阶△减小。最小和最大阶距是由△MIN和△MAX分别确定的。当长时间没有出现连码,CVSD编码器退化为一个线性增量调制(LDM)编码器。

2.2 CVSD的译码算法

图4是CVSD译码算法框图,其量阶调整是基于前3位的连码。译码过程就是编码的逆过程,只是在积分器I1后面增加了一个低通滤波器,用于抑制带外干扰。

3 CVSD算法在FPGA中的实现

3.1 硬件实现框图

考虑到实际需求,采用了通用性较强的A/D,D/A元器件和FPGA器件。该硬件可以同时实现3路CVSD编译码算法,一路采用FPGA(XC3S1500)实现,两路采用专用芯片实现;同时编译码之间可以通过FPGA内部逻辑控制互相通信。在FPGA内设计实现了CVSD编译码算法,在该器件内融合多种控制功能,可以在线编程、方便调试。

音频信号在进行A/D采样之前,为了防止带外信号进入,首先进行低通滤波;再通过高倍时钟进行采样得到数字信号进入FPGA进行编译码处理。译码过后的信号通过D/A输出模拟信号,该信号再经过低通滤波器后输出,得到音频信号。

3.2 CVSD算法实现框图

在FPGA内部算法实现上,采用了“自顶向下”的设计方法,即根据要求的功能先设计出顶层的原理图,该图由若干个功能模块组成。再把各个模块细化为子模块,各子模块的功能采用电路图实现,也可用硬件描述语言实现。设计中顶层采用原理图实现,子模块采用VHDL硬件描述语言实现,利用ISE自带的IP Core乘法器,经过综合和优化等过程,最终将程序下载到芯片中,使用在线逻辑分析仪ChipScope Pro进行逻辑和功能测试分析。

3.3 CVSD算法的仿真

以正弦单音输入信号为例,利用信号源产生信号幅度O.5 Vpp,频率fin(t)=1 kHz的正弦信号作为测试信号,在FPGA中利用高倍时钟产生fs(t)=64 kHz的采样时钟。对输入A/D的音频信号采用专用低通滤波芯片进行了滤波。D/A输出的信号包含了许多不必要的高次谐波分量,因此也采用低通滤波器对其进行了平滑滤波。

在设计上,不仅仅是采用FPGA实现和验证自己的CVSD编译码算法,还和专用芯片CMX639进行互相通信进行验证。CMX639是一款CVSD全双工音频调制芯片,集成了编码和译码功能,实现了单芯片语音处理能力,外围设备简单,用户可以根据实际情况,自主选择采样速率。

图8是通过ChipScope Pro采集的实时正弦信号。从图中可以看出量阶△的大小能够很好地反映输入信号斜率的大小,输出端输出信号能够很好地重现输入信号,说明CVSD编译码方式是有效的。

3.4 CVSD算法的实现

采用原理图和VHDL语言相结合的方式在FPGA中实现了CVSD电路。具体实现步骤如下:

(1)根据算法框图设计顶层原理图CVSD.SCH;

(2)利用IP Core产生底层所需要的乘法器;

(3)利用VHDL语言完成CVSD编译码模块;

(4)I/O管脚定义,约束条件编写;

(5)设计综合、编译;

(6)bit文件生成、下载,通过ChipScope Pro进行仿真测试;

(7)根据仿真测试结果返回修改设计,直到设计成功;

(8)mcs文件生成、加载,最终验证。

验证是FPGA设计中很重要的一环,只有通过验证才能说明设计的正确与否。采用XILINX公司的Spartan一3系列中的XC3S1500来具体实现CVSD的编译码功能。通过自己设计的编译码算法和CMX639专用芯片的编译码模块互相通信,输入实际语音信号测试,能够很好地从D/A输出语音信号,从CMX639译码输出也能听到语音信号,达到了满意的效果。

4 结 语

本文提出的FPGA设计方法很好地实现了CVSD编译码功能,充分利用了FPGA的优势,可以同时实现多路CVSD编译码功能,弥补了采用专用芯片实现CVSD编译码的不足,设计灵活、简单,成本低,具有很好的应用前景。

举报

举报

举报

举报