引言

Intel公司推出的XScale采用ARM V5TE结构,是Strong ARM的升级换代产品。XScale PXA270处理器最高主频可达到624M赫兹,加入了Wireless MMX、Intel SpeedStep等新技术,以其高性能、低功耗、多功能等特点在信息家电、工业控制等领域得到了广泛的应用。在嵌入式控制中,“微处理器+FPGA”是一种常用的解决方案,FPGA(现场可编程门阵列)有编程方便、集成度高、速度快等特点,电子设计人员可以通过硬件编程的方法来实现FPGA芯片各种功能的开发,在我们的一个数控平台的研究项目中,采用XScale PXA270作为主CPU,并对其进行FPGA扩展,使其具有插补、电机驱动、信号处理、I/O口扩展的功能。Linux以其内核精炼、高效、源代码开放且免费等优势,嵌入式领域得到了广泛的应用。下面以Intel XScale PXA270上的Altera FLEX/ACEX的应用为例,详细介绍Linux下的FPGA设备驱动的实现。

1 Altera FLEX/ACEX芯片结构

Altera FLEX/ACEX芯片是基于查找表LUT(Look-Up-Table)原理而实现的,LUT本质上就是一个RAM。目前FPGA中多使用4输入的LUT,所以每个LUT可以看成一个有4位地址线的16×1的RAM。当用户通过原理图或HDL语言描述一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM,这样,每输入一个信号进行逻辑运算都等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

由于LUT主要适合SRAM工艺生产,所以目前大部分FPGA都是基于SRAM工艺的,而SRAM工艺的芯片在掉电后信息就会丢失,一定要外加1片专用配置芯片(本实验电路使用Altera EPC2LC20),在上电时,由这个专用配置芯片把数据加载到FPGA中然后FPGA即可正常工作。由于配置时间很短,因此不会影响系统正常工作,在使用ACEX1K50之前,应对其进行设计编程,实现相应寄存器及I/O口的功能。有关FPGA的详细内容请参阅相关资料。

2 Intel XScale PXA270处理器的系统存储器接口

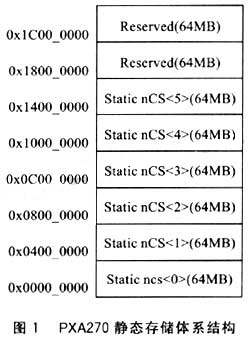

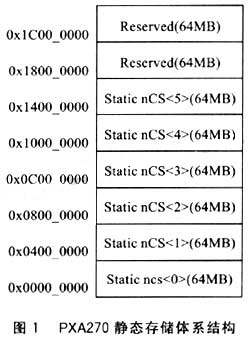

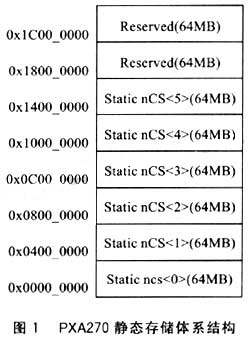

PXA270处理器的可编程静态存储体系结构如图1所示。

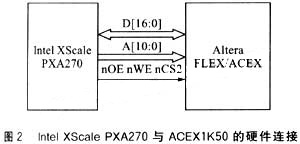

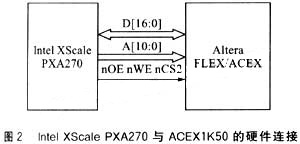

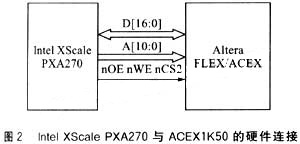

在系统上,ACEX1K50位于nCS<2>上,物理地址0x8000000-0x8001000共4K的静态地址空间,图2表示了Intel XScale PXA270与ACEX1K50的硬件连接关系。

3 Linux下ACEX1K50设备驱动的实现

3.1 Linux下设备驱动基本原理

设备驱动程序是应用程序与硬件之间的一个中间软件层,设备驱动程序为应用程序屏蔽了硬件的细节。这样在应用程序看来,硬件设备只是一个设备文件,应用程序可以像操作普通文件一样对应用设备进行操作,设备驱动程序是内核的一部分,它主要实现的功能有:对设备进行初始化和释放;把数据从内核传送到硬件和从硬件读取数据;读取应用程序传送给设备文件的数据,回送应用程序请求的数据以及检测和处理设备出现的错误。

Linux将设备分为最基本的两大类:一类是字符设备;另一类是块设备,字符设备和块设备的主要区别在于是否使用了缓冲技术,字符设备以单个字节为单位进行顺序读/写操作,通常不使用缓冲技术,块设备为了提高效率,利用一块系统内存作为读/写操作的缓冲区,由于涉及缓冲区管理、调度和同步等问题,实现起来比字符设备复杂得多。

Linux通过设备文件系统对设备进行管理,各种设备都以文件的形式存放在/dev目录下,称为“设备文件”。应用程序可以像普通文件一样打开、关闭和读/写这些设备文件,为了管理这些设备,系统为设备编了号,每个设备号又分为主设备号和次设备号,主设备号用来区分不同种类的设备,而次设备号用来区分同一类型的多个设备,Linux为所有的设备文件都提供了统一的操作函数接口,方法是使用数据结构struct FILE_operations,这个数据结构中包括许多操作函数的指针,如open()、close()、read()和write()等,但由于外设的种类较多,操作方式各不相同,struct file_operations结构体中的成员为一系列的接口函数,如用于读/写的read/write函数和用于控制的ioct1等。打开一个文件就是调用这个文件file_operations中的open操作,不同类型的文件(如普通的磁盘数据文件)有不同的file_operations成员函数,接口函数完成磁盘数据块读/写操作,而对于各种设备文件,则最终调用各自驱动程序中的I/O函数进行具体设备的操作,这样,应用程序根本不必考虑操作的是设备还是普通文件,可一律当做文件处理,具有非常清晰 、统一的I/O接口,所以file_operations是文件层次的I/O接口。

3.2 ACEX1K50在Linux下设备驱动的实现

驱动程序中使用内存映射可以提供给用户程序直接访问设备内存的能力。使用内存映射得好处是处理大文件时速度明显快于标准文件I/O,无论读/写,都少了一次用户空间与内核空间之间的复制,在用户空间对ACEX1K50 FPGA设备的访问是通过内存映射来实现的。

ACEX1K50可以看作是硬件连接在PXA270微处理器的nCS<2>上的一段物理地址来寻址。因为有虚拟内存管理单元,所以如果Linux下,必须先把物理地址映射到虚拟地址空间,然后才能对该段地址进行读/写。

在内核驱动程序的初始化阶段,通过ioremap()将ACEX1K50的这段物理地址映射到内核虚拟空间;在驱动程序的mmap系统调用中,使用remap_page_range()将该块COM映射到用户虚拟空间,这样内核空间和用户空间都能访问ACEX1K50的这段被映射后的虚拟地址。

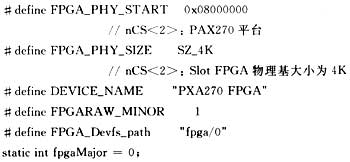

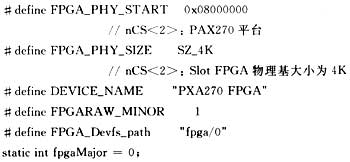

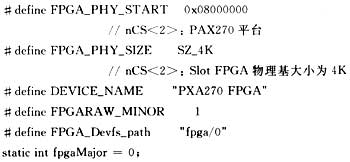

由于ACEX1K50位于nCS<2>上,参照PXA270静态存储体系结构映射表,其物理起始地址为0x08000000。另外,其设备名称及主次设备号定义如下:

其中FPGA主设备号定义为零,使得操作系统可以随机为该设备分配主设备号。

ioremap()的作为是把一个物理内存地址点映射为一个内核指针,被映射数据的长度由size参数设定,该函数的实质上把一块物理区域二次映射到一个可以从驱动程序里访问的虚拟地址上去,以下是该函数的定义:

void*ioremap(unsigned long phys_addr,unsigned long size);

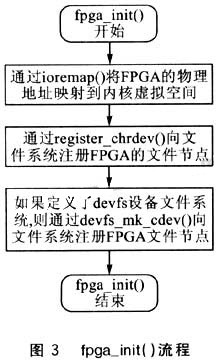

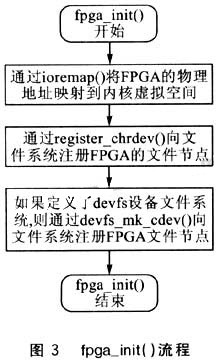

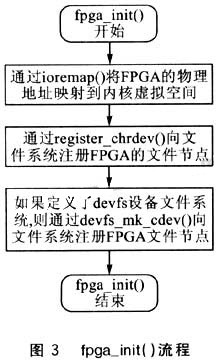

设备驱动通过fpga_init()函数初始化FPGA设备,最终通过init_module(fpga_init)在内核启动时初始化FPGA设备。

fpga_init()函数的流程如图3所示。

ioremap()调用的语句如下:

pxa270_fpga_base=(unsigned long)ioremap(FPGA_PHY_START,SZ_4K);

可以通过ioremap()调用的返回值pxa270_fpga_base来判断FPGA物理地址到内核虚拟空间是否映射成功。

if(!pxa270_FPGA_base){

printk(“ioremap pxa270 fpga failed/n”);

return-EINVAL;

}

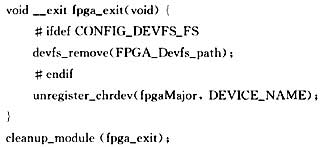

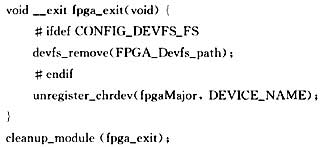

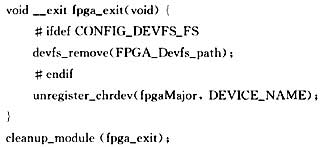

向设备文件系统注销FPGA设备通过调用cheanup_module()函数来实现。其代码如下:

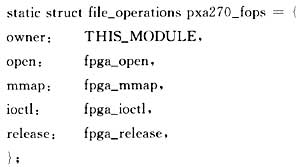

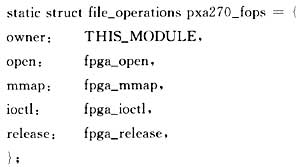

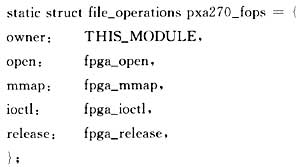

在向内核设备文件系统注册该FPGA驱动后,还须实现设备驱动的file_operations结构,ACEX1K50的设备驱动定义了如下file_operations成员函数:

其中fpga_open和fpga_release系统调用的功能只简单地实现了FPGA设备使用计数器的递增与递减,fpga_ioctl系统调用也只是简单的打印一条没有ioctl控制的信息提示。这里不再分析实现的具体代码。下面具体分析fpga_mmap的实现过程:

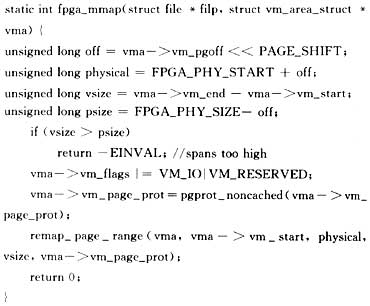

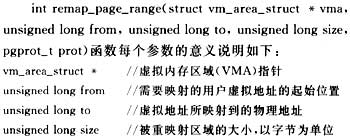

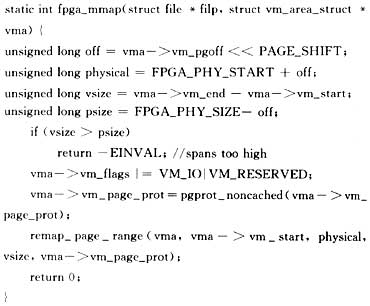

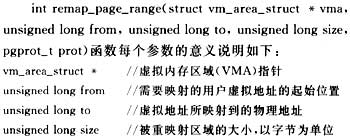

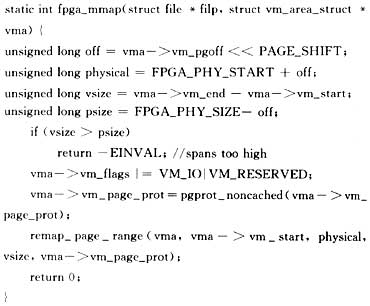

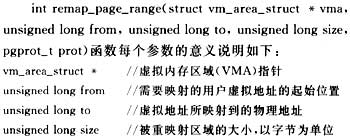

fpga_mmap(struct file*filp,struct vm_area_struct*vma)系统调用允许直接将FPGA设备内存线性地映射到用户进程的地址空间中,fpga_mmap系统调用是通过调用remap_page_range()函数来实现一段线性物理地址的映射,调用remap_page_range()函数需要填写vm_area_struct结构的几个关键字段。

4 ACEX1K50设备驱动在用户程序中的使用

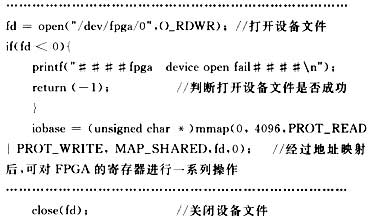

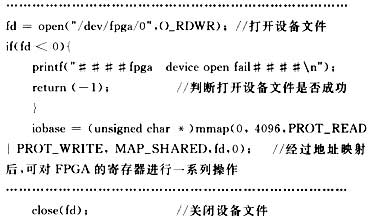

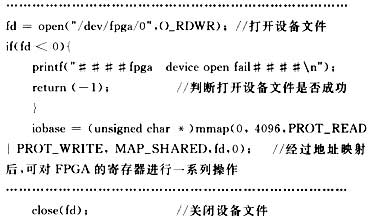

当设备驱动实现后就可以在用户空间使用该设备了。在用户空间主要是通过调用mmap()函数来实现对FPGA设备的访问。以下是用户空间应用程序的一个示例:

结语

本文通过介绍ACEX1K50在Linux操作系统下设备驱动的实现过程,为FPGA在嵌入式领域的应用提供了一种方法。在实际应用中,通过用户程序能够很好地实现对FPGA硬件编程后的各种功能的控制。

引言

Intel公司推出的XScale采用ARM V5TE结构,是Strong ARM的升级换代产品。XScale PXA270处理器最高主频可达到624M赫兹,加入了Wireless MMX、Intel SpeedStep等新技术,以其高性能、低功耗、多功能等特点在信息家电、工业控制等领域得到了广泛的应用。在嵌入式控制中,“微处理器+FPGA”是一种常用的解决方案,FPGA(现场可编程门阵列)有编程方便、集成度高、速度快等特点,电子设计人员可以通过硬件编程的方法来实现FPGA芯片各种功能的开发,在我们的一个数控平台的研究项目中,采用XScale PXA270作为主CPU,并对其进行FPGA扩展,使其具有插补、电机驱动、信号处理、I/O口扩展的功能。Linux以其内核精炼、高效、源代码开放且免费等优势,嵌入式领域得到了广泛的应用。下面以Intel XScale PXA270上的Altera FLEX/ACEX的应用为例,详细介绍Linux下的FPGA设备驱动的实现。

1 Altera FLEX/ACEX芯片结构

Altera FLEX/ACEX芯片是基于查找表LUT(Look-Up-Table)原理而实现的,LUT本质上就是一个RAM。目前FPGA中多使用4输入的LUT,所以每个LUT可以看成一个有4位地址线的16×1的RAM。当用户通过原理图或HDL语言描述一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM,这样,每输入一个信号进行逻辑运算都等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

由于LUT主要适合SRAM工艺生产,所以目前大部分FPGA都是基于SRAM工艺的,而SRAM工艺的芯片在掉电后信息就会丢失,一定要外加1片专用配置芯片(本实验电路使用Altera EPC2LC20),在上电时,由这个专用配置芯片把数据加载到FPGA中然后FPGA即可正常工作。由于配置时间很短,因此不会影响系统正常工作,在使用ACEX1K50之前,应对其进行设计编程,实现相应寄存器及I/O口的功能。有关FPGA的详细内容请参阅相关资料。

2 Intel XScale PXA270处理器的系统存储器接口

PXA270处理器的可编程静态存储体系结构如图1所示。

在系统上,ACEX1K50位于nCS<2>上,物理地址0x8000000-0x8001000共4K的静态地址空间,图2表示了Intel XScale PXA270与ACEX1K50的硬件连接关系。

3 Linux下ACEX1K50设备驱动的实现

3.1 Linux下设备驱动基本原理

设备驱动程序是应用程序与硬件之间的一个中间软件层,设备驱动程序为应用程序屏蔽了硬件的细节。这样在应用程序看来,硬件设备只是一个设备文件,应用程序可以像操作普通文件一样对应用设备进行操作,设备驱动程序是内核的一部分,它主要实现的功能有:对设备进行初始化和释放;把数据从内核传送到硬件和从硬件读取数据;读取应用程序传送给设备文件的数据,回送应用程序请求的数据以及检测和处理设备出现的错误。

Linux将设备分为最基本的两大类:一类是字符设备;另一类是块设备,字符设备和块设备的主要区别在于是否使用了缓冲技术,字符设备以单个字节为单位进行顺序读/写操作,通常不使用缓冲技术,块设备为了提高效率,利用一块系统内存作为读/写操作的缓冲区,由于涉及缓冲区管理、调度和同步等问题,实现起来比字符设备复杂得多。

Linux通过设备文件系统对设备进行管理,各种设备都以文件的形式存放在/dev目录下,称为“设备文件”。应用程序可以像普通文件一样打开、关闭和读/写这些设备文件,为了管理这些设备,系统为设备编了号,每个设备号又分为主设备号和次设备号,主设备号用来区分不同种类的设备,而次设备号用来区分同一类型的多个设备,Linux为所有的设备文件都提供了统一的操作函数接口,方法是使用数据结构struct FILE_operations,这个数据结构中包括许多操作函数的指针,如open()、close()、read()和write()等,但由于外设的种类较多,操作方式各不相同,struct file_operations结构体中的成员为一系列的接口函数,如用于读/写的read/write函数和用于控制的ioct1等。打开一个文件就是调用这个文件file_operations中的open操作,不同类型的文件(如普通的磁盘数据文件)有不同的file_operations成员函数,接口函数完成磁盘数据块读/写操作,而对于各种设备文件,则最终调用各自驱动程序中的I/O函数进行具体设备的操作,这样,应用程序根本不必考虑操作的是设备还是普通文件,可一律当做文件处理,具有非常清晰 、统一的I/O接口,所以file_operations是文件层次的I/O接口。

3.2 ACEX1K50在Linux下设备驱动的实现

驱动程序中使用内存映射可以提供给用户程序直接访问设备内存的能力。使用内存映射得好处是处理大文件时速度明显快于标准文件I/O,无论读/写,都少了一次用户空间与内核空间之间的复制,在用户空间对ACEX1K50 FPGA设备的访问是通过内存映射来实现的。

ACEX1K50可以看作是硬件连接在PXA270微处理器的nCS<2>上的一段物理地址来寻址。因为有虚拟内存管理单元,所以如果Linux下,必须先把物理地址映射到虚拟地址空间,然后才能对该段地址进行读/写。

在内核驱动程序的初始化阶段,通过ioremap()将ACEX1K50的这段物理地址映射到内核虚拟空间;在驱动程序的mmap系统调用中,使用remap_page_range()将该块COM映射到用户虚拟空间,这样内核空间和用户空间都能访问ACEX1K50的这段被映射后的虚拟地址。

由于ACEX1K50位于nCS<2>上,参照PXA270静态存储体系结构映射表,其物理起始地址为0x08000000。另外,其设备名称及主次设备号定义如下:

其中FPGA主设备号定义为零,使得操作系统可以随机为该设备分配主设备号。

ioremap()的作为是把一个物理内存地址点映射为一个内核指针,被映射数据的长度由size参数设定,该函数的实质上把一块物理区域二次映射到一个可以从驱动程序里访问的虚拟地址上去,以下是该函数的定义:

void*ioremap(unsigned long phys_addr,unsigned long size);

设备驱动通过fpga_init()函数初始化FPGA设备,最终通过init_module(fpga_init)在内核启动时初始化FPGA设备。

fpga_init()函数的流程如图3所示。

ioremap()调用的语句如下:

pxa270_fpga_base=(unsigned long)ioremap(FPGA_PHY_START,SZ_4K);

可以通过ioremap()调用的返回值pxa270_fpga_base来判断FPGA物理地址到内核虚拟空间是否映射成功。

if(!pxa270_FPGA_base){

printk(“ioremap pxa270 fpga failed/n”);

return-EINVAL;

}

向设备文件系统注销FPGA设备通过调用cheanup_module()函数来实现。其代码如下:

在向内核设备文件系统注册该FPGA驱动后,还须实现设备驱动的file_operations结构,ACEX1K50的设备驱动定义了如下file_operations成员函数:

其中fpga_open和fpga_release系统调用的功能只简单地实现了FPGA设备使用计数器的递增与递减,fpga_ioctl系统调用也只是简单的打印一条没有ioctl控制的信息提示。这里不再分析实现的具体代码。下面具体分析fpga_mmap的实现过程:

fpga_mmap(struct file*filp,struct vm_area_struct*vma)系统调用允许直接将FPGA设备内存线性地映射到用户进程的地址空间中,fpga_mmap系统调用是通过调用remap_page_range()函数来实现一段线性物理地址的映射,调用remap_page_range()函数需要填写vm_area_struct结构的几个关键字段。

4 ACEX1K50设备驱动在用户程序中的使用

当设备驱动实现后就可以在用户空间使用该设备了。在用户空间主要是通过调用mmap()函数来实现对FPGA设备的访问。以下是用户空间应用程序的一个示例:

结语

本文通过介绍ACEX1K50在Linux操作系统下设备驱动的实现过程,为FPGA在嵌入式领域的应用提供了一种方法。在实际应用中,通过用户程序能够很好地实现对FPGA硬件编程后的各种功能的控制。

举报

举报

举报

举报