近年来,随着经济的高速增长,无线通信得到了飞速地发展。由于扩展频谱信号具有抗干扰、保密、抗侦破和抗衰落等特点,扩频通信在军事无线通信领域(如测控通信)中被广泛应用;随着技术的成熟及成本的降低,其在民用通信市场上具有更广大的发展前景。

本文首先介绍了FPGA的设计思想及流程,然后以一种扩频通信调制器为例,描述了如何实现自顶向下的设计:包括调制器的顶层设计、划分的下一层基本单元的设计等,并重点分析了基本单元之一的PN码产生器的设计实现及仿真验证过程。

FPGA设计方法简介

FPGA技术的飞速发展,对国内的电子设计工程师提出了严峻的挑战,以往传统的设计方法,如单纯的原理图输入方法,已很难满足目前的要求。设计人员必须采用高水准的设计工具,如硬件描述语言(Verilog HDL)或语言与原理图结合来进行设计。

1 FPGA的设计思想

FPGA的设计思想一般采用自顶向下(Top-down)的设计,自顶向下的设计是从系统级开始的,把系统化分为基本单元,然后再把每个单元划分为下一层次的基本单元,一直这样做下去,直到可以直接用EDA元件库里的元件来实现为止。

2 FPGA的设计流程

FPGA器件的设计一般可分为设计输入、设计实现和编程三个设计步骤及相应的功能仿真、时序仿真和器件测试三个设计验证过程。

设计输入:设计输入有多种方式,目前最常用的有电路图和硬件描述语言两种。对于简单的设计,可采用原理图或ABEL语言设计。对于复杂的设计,可采用原理图或行为描述语言(如VHDL语言),或者两者混用,采用层次化设计方法,分模块、分层次的进行描述。软件在设计输入时,会检查语法错误,生成网表文件,供设计实现和设计校验用。

设计实现:设计实现是指从设计输入文件到位流文件的编译过程。在该过程中,编译软件自动地对设计文件进行综合、优化,并针对所选中的器件进行映射、布局、布线,产生相应的位流数据文件。

器件编程:器件编程就是将位流数据文件配置到相应的FPGA器件中。

设计校验:对应于设计输入、设计实现和器件编程的功能仿真、时序仿真、器件测试组成设计验证的三个部分。功能仿真验证设计的功能逻辑,在设计输入过程中,对部分功能或整个设计均可进行仿真。完成设计实现后进行时序仿真,针对器件的布局、布线方案进行时延仿真,分析定时关系。器件测试是在器件编程完成后进行,通过实验或借助于测试工具,测试器件最终功能和性能指标。

扩频调制器的FPGA设计

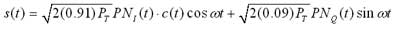

本文介绍的一种扩频调制器,常应用于测控通信领域。其信号形式是I、Q两路正交信道上分别传送扩频指令和测距码,采用UQPSK调制,I、Q两路的功率比为10:1,其信号的数学表达式如下:

(1)

式中:ω为载波频率; PT为信号总功率;c(t)为指令码;PNI为指令信道PN码;PNQ为测距信道PN码。PNI是码长为210-1=1023的Gold码,短码;PNQ是码长为218-28=261 888的18级截短码,长码;长短码长之比为256。要求两种码起始同步,即当长码发生器经过全“1”状态时,短码发生器也经过它的全“1”状态。

1 扩频调制器的顶层设计

扩频调制器的实现如图1所示。FPGA的顶层设计见图1的虚框部分,包括信息码产生器及寄存器、码钟及PN码产生器、载波产生器、0/π调制模块等基本单元。下面以PN码产生器为例介绍基本单元的设计。

图1 扩频调制器实现框图

2 基本单元的设计

PN码产生器包括两种:码长分别为1023位的码产生器及261 888位的截短码产生器,初步的设计如图2所示,PNMZ为码钟,产生RESET信号同时复位长、短码产生器。

图2 两路PN码的初步设计图

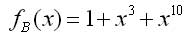

Gold码由两路小M序列异或组成,下面介绍210-1位码产生器的设计:

PN码的本原多项式为:

(2)

(3)

初相 A:0010011100 B:1001001000

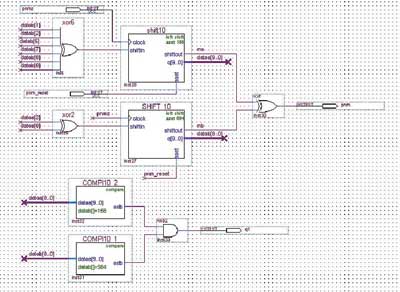

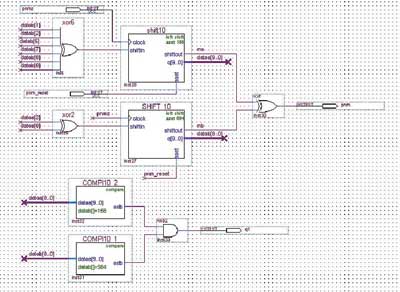

210-1位PN码产生器的FPGA设计如图3所示。pnmz为码钟输入端;pnm_reset为PN码的复位端;pnm为码输出端;q1为码全“1”信号输出端。当复位脉冲信号来到后,移位寄存器在码钟推动下从设定的初值开始左移,左移移位寄存器的高位先出,产生小M序列。两路小M序列异或产生PN码。两路比较器产生的信号相与后输出全“1”信号。PN码产生器划分成的下一级基本单元,包括移位寄存器、比较器、与门、异或门,都可以直接用EDA元件库里的元件。

图3 210-1位PN码发生器的FPGA设计图

扩频调制器的FPGA仿真

工程上,FPGA的仿真类型可分为功能仿真和时序仿真(或称前仿真和后仿真)。功能仿真是未经布线和适配之前,使用原始设计综合之后的文件进行仿真。时序仿真,即将FPGA设计综合之后,再由FPGA适配器(完成芯片内自动布线等功能)映射于具体芯片后得到的文件进行仿真。

本文选用QuartusII3.0集成的仿真工具进行波形仿真。对设计的主要模块在通过综合之后,首先进行功能仿真,验证原始设计的正确性,验证设计结果的逻辑功能是否符合原始规定的逻辑功能。通过功能仿真之后,在设计中考虑器件延时后,再进行布局布线后的仿真,通过观察波形和数据,可验证是否能满足时序要求,是否能得到预期的值。

在设计过程中,作者针对主要的电路模块进行了仿真,包括:PN码产生器、信息注入电路、并/串转换电路等。下面介绍扩频调制器两路PN码产生器的仿真及设计改进过程。

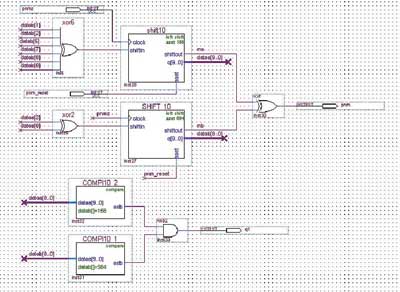

1 PN码产生器的功能仿真

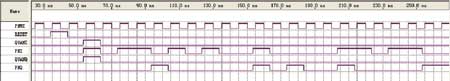

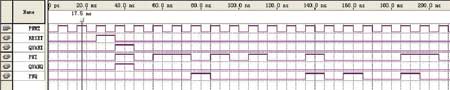

扩频调制器的两路PN码产生器,I路短码的初相是“10,1101,0100”,Q路长码的初相“00,0010,0000,1010,0100”(码初相指两路小M序列初相异或后的初值)。初始的设计见图3。对设计综合过后,进行功能仿真。仿真结果说明:两路PN码起始同步,PNI起始相位:10,1101,0100;PNQ起始相位:00,0010,0000,1010,0100。原始设计符合要求。仿真结果如图4所示。(PNMZ为码钟;RESET为复位信号;PNI、PNQ为I、Q两路PN码;QUANI、QIANQ为I、Q两路PN码全“1”信号。)

图4 两路PN码的功能仿真图

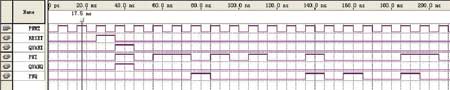

2 PN码产生器的时序仿真

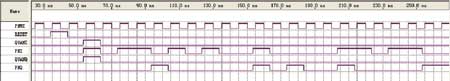

通过功能仿真之后,对设计进行布局布线编译,然后进行时序仿真。发现可能会在PN码序列中产生毛刺信号,并通过多次仿真发现复位信号也可能产生毛刺信号,导致I、Q两路信号起始不同步,如图5所示。

图5 两路PN码的时序仿真图

作者对电路进行改进,将复位信号、PN码信号、全“1”信号上加上D触发器,用码钟打一次,消除电路毛刺。改进后的电路如图6所示。

图6 改进后的两路PN码设计图

再次进行时序仿真,发现毛刺消除,PN码产生正常,说明两路PN码电路设计正确,可以作为经验证的基本单元加入扩频调制器的FPGA设计。

图7 改进后的PN码时序仿真图

结束语

本文介绍了一种扩频通信调制器的FPGA设计实现方法,着重说明了PN码产生器的设计仿真过程,形象地阐述了FPGA自顶向下的设计思想及详尽的设计流程。FPGA在无线通信工程领域的应用已非常普遍,掌握一种好的设计方法对电子设计师们很重要,希望本文对读者有所帮助。

近年来,随着经济的高速增长,无线通信得到了飞速地发展。由于扩展频谱信号具有抗干扰、保密、抗侦破和抗衰落等特点,扩频通信在军事无线通信领域(如测控通信)中被广泛应用;随着技术的成熟及成本的降低,其在民用通信市场上具有更广大的发展前景。

本文首先介绍了FPGA的设计思想及流程,然后以一种扩频通信调制器为例,描述了如何实现自顶向下的设计:包括调制器的顶层设计、划分的下一层基本单元的设计等,并重点分析了基本单元之一的PN码产生器的设计实现及仿真验证过程。

FPGA设计方法简介

FPGA技术的飞速发展,对国内的电子设计工程师提出了严峻的挑战,以往传统的设计方法,如单纯的原理图输入方法,已很难满足目前的要求。设计人员必须采用高水准的设计工具,如硬件描述语言(Verilog HDL)或语言与原理图结合来进行设计。

1 FPGA的设计思想

FPGA的设计思想一般采用自顶向下(Top-down)的设计,自顶向下的设计是从系统级开始的,把系统化分为基本单元,然后再把每个单元划分为下一层次的基本单元,一直这样做下去,直到可以直接用EDA元件库里的元件来实现为止。

2 FPGA的设计流程

FPGA器件的设计一般可分为设计输入、设计实现和编程三个设计步骤及相应的功能仿真、时序仿真和器件测试三个设计验证过程。

设计输入:设计输入有多种方式,目前最常用的有电路图和硬件描述语言两种。对于简单的设计,可采用原理图或ABEL语言设计。对于复杂的设计,可采用原理图或行为描述语言(如VHDL语言),或者两者混用,采用层次化设计方法,分模块、分层次的进行描述。软件在设计输入时,会检查语法错误,生成网表文件,供设计实现和设计校验用。

设计实现:设计实现是指从设计输入文件到位流文件的编译过程。在该过程中,编译软件自动地对设计文件进行综合、优化,并针对所选中的器件进行映射、布局、布线,产生相应的位流数据文件。

器件编程:器件编程就是将位流数据文件配置到相应的FPGA器件中。

设计校验:对应于设计输入、设计实现和器件编程的功能仿真、时序仿真、器件测试组成设计验证的三个部分。功能仿真验证设计的功能逻辑,在设计输入过程中,对部分功能或整个设计均可进行仿真。完成设计实现后进行时序仿真,针对器件的布局、布线方案进行时延仿真,分析定时关系。器件测试是在器件编程完成后进行,通过实验或借助于测试工具,测试器件最终功能和性能指标。

扩频调制器的FPGA设计

本文介绍的一种扩频调制器,常应用于测控通信领域。其信号形式是I、Q两路正交信道上分别传送扩频指令和测距码,采用UQPSK调制,I、Q两路的功率比为10:1,其信号的数学表达式如下:

(1)

式中:ω为载波频率; PT为信号总功率;c(t)为指令码;PNI为指令信道PN码;PNQ为测距信道PN码。PNI是码长为210-1=1023的Gold码,短码;PNQ是码长为218-28=261 888的18级截短码,长码;长短码长之比为256。要求两种码起始同步,即当长码发生器经过全“1”状态时,短码发生器也经过它的全“1”状态。

1 扩频调制器的顶层设计

扩频调制器的实现如图1所示。FPGA的顶层设计见图1的虚框部分,包括信息码产生器及寄存器、码钟及PN码产生器、载波产生器、0/π调制模块等基本单元。下面以PN码产生器为例介绍基本单元的设计。

图1 扩频调制器实现框图

2 基本单元的设计

PN码产生器包括两种:码长分别为1023位的码产生器及261 888位的截短码产生器,初步的设计如图2所示,PNMZ为码钟,产生RESET信号同时复位长、短码产生器。

图2 两路PN码的初步设计图

Gold码由两路小M序列异或组成,下面介绍210-1位码产生器的设计:

PN码的本原多项式为:

(2)

(3)

初相 A:0010011100 B:1001001000

210-1位PN码产生器的FPGA设计如图3所示。pnmz为码钟输入端;pnm_reset为PN码的复位端;pnm为码输出端;q1为码全“1”信号输出端。当复位脉冲信号来到后,移位寄存器在码钟推动下从设定的初值开始左移,左移移位寄存器的高位先出,产生小M序列。两路小M序列异或产生PN码。两路比较器产生的信号相与后输出全“1”信号。PN码产生器划分成的下一级基本单元,包括移位寄存器、比较器、与门、异或门,都可以直接用EDA元件库里的元件。

图3 210-1位PN码发生器的FPGA设计图

扩频调制器的FPGA仿真

工程上,FPGA的仿真类型可分为功能仿真和时序仿真(或称前仿真和后仿真)。功能仿真是未经布线和适配之前,使用原始设计综合之后的文件进行仿真。时序仿真,即将FPGA设计综合之后,再由FPGA适配器(完成芯片内自动布线等功能)映射于具体芯片后得到的文件进行仿真。

本文选用QuartusII3.0集成的仿真工具进行波形仿真。对设计的主要模块在通过综合之后,首先进行功能仿真,验证原始设计的正确性,验证设计结果的逻辑功能是否符合原始规定的逻辑功能。通过功能仿真之后,在设计中考虑器件延时后,再进行布局布线后的仿真,通过观察波形和数据,可验证是否能满足时序要求,是否能得到预期的值。

在设计过程中,作者针对主要的电路模块进行了仿真,包括:PN码产生器、信息注入电路、并/串转换电路等。下面介绍扩频调制器两路PN码产生器的仿真及设计改进过程。

1 PN码产生器的功能仿真

扩频调制器的两路PN码产生器,I路短码的初相是“10,1101,0100”,Q路长码的初相“00,0010,0000,1010,0100”(码初相指两路小M序列初相异或后的初值)。初始的设计见图3。对设计综合过后,进行功能仿真。仿真结果说明:两路PN码起始同步,PNI起始相位:10,1101,0100;PNQ起始相位:00,0010,0000,1010,0100。原始设计符合要求。仿真结果如图4所示。(PNMZ为码钟;RESET为复位信号;PNI、PNQ为I、Q两路PN码;QUANI、QIANQ为I、Q两路PN码全“1”信号。)

图4 两路PN码的功能仿真图

2 PN码产生器的时序仿真

通过功能仿真之后,对设计进行布局布线编译,然后进行时序仿真。发现可能会在PN码序列中产生毛刺信号,并通过多次仿真发现复位信号也可能产生毛刺信号,导致I、Q两路信号起始不同步,如图5所示。

图5 两路PN码的时序仿真图

作者对电路进行改进,将复位信号、PN码信号、全“1”信号上加上D触发器,用码钟打一次,消除电路毛刺。改进后的电路如图6所示。

图6 改进后的两路PN码设计图

再次进行时序仿真,发现毛刺消除,PN码产生正常,说明两路PN码电路设计正确,可以作为经验证的基本单元加入扩频调制器的FPGA设计。

图7 改进后的PN码时序仿真图

结束语

本文介绍了一种扩频通信调制器的FPGA设计实现方法,着重说明了PN码产生器的设计仿真过程,形象地阐述了FPGA自顶向下的设计思想及详尽的设计流程。FPGA在无线通信工程领域的应用已非常普遍,掌握一种好的设计方法对电子设计师们很重要,希望本文对读者有所帮助。

举报

举报

举报

举报