交通灯是城市交通监管系统的重要组成部分,对于保证机动车辆的安全运行,维持城市道路的顺畅起到了重要作用。目前很多城市交叉路口的交通灯实行的是定时控制,灯亮的时间是预先设定好的,在时间和空间方面的应变性能较差,一定程度上造成了交通资源的浪费,加重了道路交通压力。本文在EDA技术的基础上,利用FPGA的相关知识设计了交通灯控制系统,可以根据实际情况对灯亮时间进行自由调整,整个设计系统通过Max+PlusⅡ软件进行了模拟仿真,并下载到FPGA器件中进行硬件的调试,验证了设计的交通信号灯控制电路完全可以实现预定的功能,具有一定的实用性。

1 系统设计要求

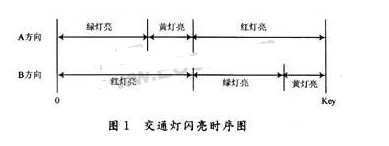

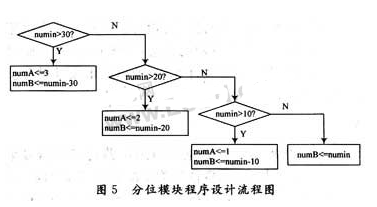

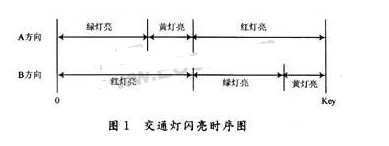

所设计的交通信号灯控制电路,主要适用于在两条干道汇合点形成的十字交叉路口,路口设计两组红绿灯分别对两个方向上的交通运行状态进行管理。交通灯的持续闪亮时间由键盘输入控制。灯亮时序如图1所示,当B方向的红灯亮时,A方向对应绿灯亮,由绿灯转换成红灯的过渡阶段黄灯亮,即B方向红灯亮的时间等于A方向绿灯和黄灯亮的时间之和。同理,当A方向的红灯变亮时,B方向的交通灯也遵循此规则。各干道上安装有数码管,以倒计时的形式显示本道各信号灯闪亮的时间。当出现特殊情况时,各方向上均亮红灯,倒计时停止。特殊运行状态结束后,控制器恢复原来的状态,继续运行。

2 系统整体设计

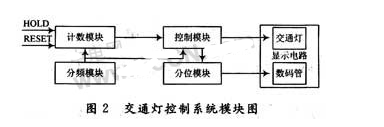

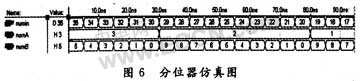

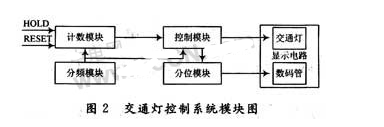

整个系统设计如图2所示,该系统主要由计数模块、控制模块、分频模块、分位模块以及显示电路构成。其中分频模块主要将系统输入的基准时钟信号转换为1 Hz的激励信号,驱动计数模块和控制模块工作。控制模块根据计数器的计数情况对交通灯的亮灭及持续时间进行控制,并通过分位电路将灯亮时间以倒计时的形式通过数码管显示出来。图中Reset是复位信号,高电平有效,可以实现对计数器的异步清零。Hold为保持信号,当Hold为“1”,计数器暂停计数,表示出现特殊情况,各方向车辆都处于禁行状态。

3 主要功能模块设计及仿真

3.1 计数模块设计

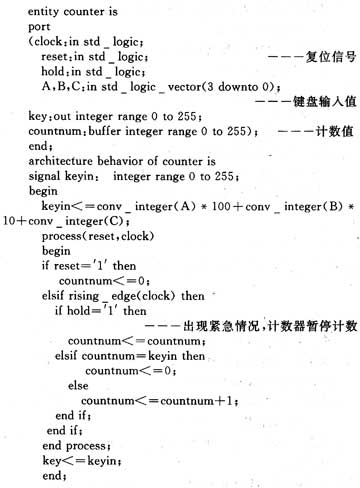

计数模块主要实现累加循环计数,计数的最大值由键盘输入控制,输出的计数值为控制模块的灯控提供参考,计数器的主程序设计如下:

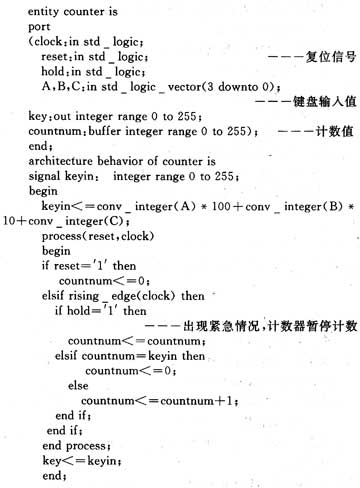

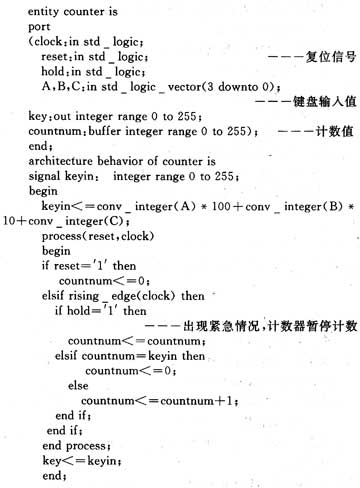

计数模块的仿真如图3所示,从图中可以看出,在时钟的驱动下,计数值不断自加,当计数值countnum等于键盘输入值32(key=32)时,计数返回到0,开始下一轮计数。当Hold检测到特殊情况时置‘1’,使计数器暂停计数。

3.2 控制器模块的仿真设计

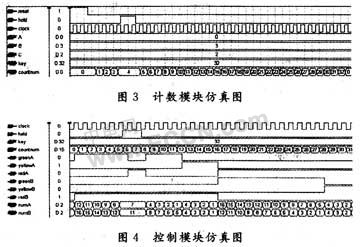

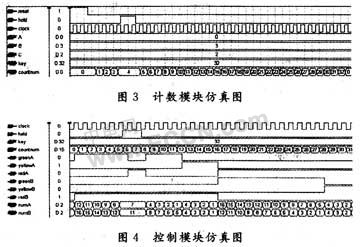

在控制器模块中,红、绿、黄三盏灯工作的总时间由键盘输入,各交通灯时间分配规则如下:红灯时间占总时间的1/2,绿灯时间占3/8,黄灯时间占1/8,本设计中键盘输入值为32(key=32),正常情况下红灯亮16 s,绿灯亮12 s,黄灯亮4 s。

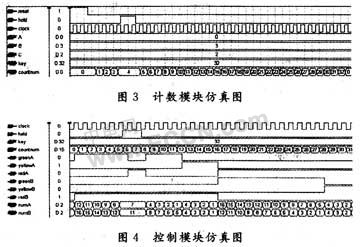

控制器仿真情况如图4所示,当hold为低电平,计数值countnum<12时,greenA输出高电平,A东西方向绿灯亮起车辆通行,此时与之相对应的redB输出高电平,B方向红灯亮起车辆禁行。A方向显示交通灯闪烁持续时间的数码管numA从12开始递减,同时B方向显示交通灯闪烁持续时间的数码管numB从16开始递减。当12<countnum<16时,yellowA输出高电平,A方向黄灯亮起,numA从数值4开始倒计时,此时greenB仍处于低电平,numB继续倒计时,B方向红灯闪亮车辆仍处于禁行状态。当countnum>16,redA输出高电平,A方向红灯亮起车辆禁行,numA从数值16开始倒计时,此时greenB输出高电平,B方向绿灯亮起车辆通行,numB从数值12开始递减。当16<countnum<28时,redA继续处于高电平状态,numA继续倒计时,A方向车辆禁行,而此时yellowB输出高电平,B方向黄灯亮起,numB从数值4开始递减。当hold为‘1’时,表示进入紧急状态,FLASH置‘1’,各方向的红灯均亮起,所有机动车禁行。

3.3 分位模块设计

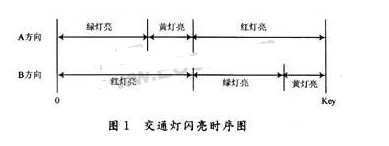

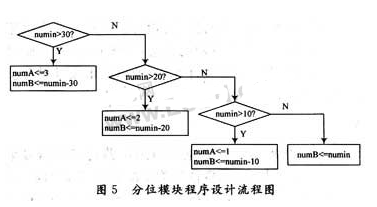

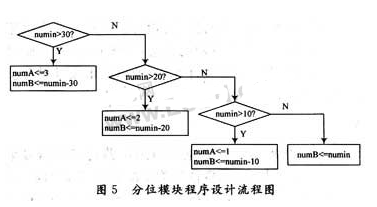

分位模块的设计主要是将灯亮时间分为十位和个位,通过两个相应的数码管分别显示出来。本设计中灯亮时间最长不超过40 s(numin<40),numA,numB分别表示十位、个位上的数字,分位模块程序设计的流程图如图5所示。

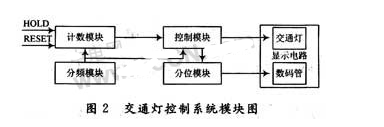

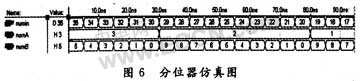

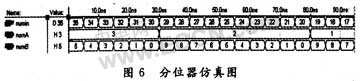

分位模块的仿真如图6所示,numin的数值大小可以通过numA,numB的组合以十进制数值显示,从而实现了分位功能。

4 系统的硬件设计及调试

本系统的主要逻辑设计由一片EPlK30TC144-3芯片完成,编写的VHDL源程序在Altera公司的逻辑综合工具Max+PlusⅡ下经过编译和功能仿真测试后,针对下载芯片进行管脚配置,下载到EPlK30TC144-3芯片中,进行相应的硬件调试,调试结果与软件仿真的结果相吻合,验证了设计完成了预定功能。

5 结 语

本文利用硬件描述语言VHDL编程,借助Altera公司的Max+PlusⅡ软件环境下进行了编译及仿真测试,通过FPGA芯片实现了一个实用的交通信号灯控制系统,设计由于采用了EDA技术,不但大大缩短了开发研制周期,提高了设计效率,而且使系统具有设计灵活,实现简单,性能稳定的特点。

交通灯是城市交通监管系统的重要组成部分,对于保证机动车辆的安全运行,维持城市道路的顺畅起到了重要作用。目前很多城市交叉路口的交通灯实行的是定时控制,灯亮的时间是预先设定好的,在时间和空间方面的应变性能较差,一定程度上造成了交通资源的浪费,加重了道路交通压力。本文在EDA技术的基础上,利用FPGA的相关知识设计了交通灯控制系统,可以根据实际情况对灯亮时间进行自由调整,整个设计系统通过Max+PlusⅡ软件进行了模拟仿真,并下载到FPGA器件中进行硬件的调试,验证了设计的交通信号灯控制电路完全可以实现预定的功能,具有一定的实用性。

1 系统设计要求

所设计的交通信号灯控制电路,主要适用于在两条干道汇合点形成的十字交叉路口,路口设计两组红绿灯分别对两个方向上的交通运行状态进行管理。交通灯的持续闪亮时间由键盘输入控制。灯亮时序如图1所示,当B方向的红灯亮时,A方向对应绿灯亮,由绿灯转换成红灯的过渡阶段黄灯亮,即B方向红灯亮的时间等于A方向绿灯和黄灯亮的时间之和。同理,当A方向的红灯变亮时,B方向的交通灯也遵循此规则。各干道上安装有数码管,以倒计时的形式显示本道各信号灯闪亮的时间。当出现特殊情况时,各方向上均亮红灯,倒计时停止。特殊运行状态结束后,控制器恢复原来的状态,继续运行。

2 系统整体设计

整个系统设计如图2所示,该系统主要由计数模块、控制模块、分频模块、分位模块以及显示电路构成。其中分频模块主要将系统输入的基准时钟信号转换为1 Hz的激励信号,驱动计数模块和控制模块工作。控制模块根据计数器的计数情况对交通灯的亮灭及持续时间进行控制,并通过分位电路将灯亮时间以倒计时的形式通过数码管显示出来。图中Reset是复位信号,高电平有效,可以实现对计数器的异步清零。Hold为保持信号,当Hold为“1”,计数器暂停计数,表示出现特殊情况,各方向车辆都处于禁行状态。

3 主要功能模块设计及仿真

3.1 计数模块设计

计数模块主要实现累加循环计数,计数的最大值由键盘输入控制,输出的计数值为控制模块的灯控提供参考,计数器的主程序设计如下:

计数模块的仿真如图3所示,从图中可以看出,在时钟的驱动下,计数值不断自加,当计数值countnum等于键盘输入值32(key=32)时,计数返回到0,开始下一轮计数。当Hold检测到特殊情况时置‘1’,使计数器暂停计数。

3.2 控制器模块的仿真设计

在控制器模块中,红、绿、黄三盏灯工作的总时间由键盘输入,各交通灯时间分配规则如下:红灯时间占总时间的1/2,绿灯时间占3/8,黄灯时间占1/8,本设计中键盘输入值为32(key=32),正常情况下红灯亮16 s,绿灯亮12 s,黄灯亮4 s。

控制器仿真情况如图4所示,当hold为低电平,计数值countnum<12时,greenA输出高电平,A东西方向绿灯亮起车辆通行,此时与之相对应的redB输出高电平,B方向红灯亮起车辆禁行。A方向显示交通灯闪烁持续时间的数码管numA从12开始递减,同时B方向显示交通灯闪烁持续时间的数码管numB从16开始递减。当12<countnum<16时,yellowA输出高电平,A方向黄灯亮起,numA从数值4开始倒计时,此时greenB仍处于低电平,numB继续倒计时,B方向红灯闪亮车辆仍处于禁行状态。当countnum>16,redA输出高电平,A方向红灯亮起车辆禁行,numA从数值16开始倒计时,此时greenB输出高电平,B方向绿灯亮起车辆通行,numB从数值12开始递减。当16<countnum<28时,redA继续处于高电平状态,numA继续倒计时,A方向车辆禁行,而此时yellowB输出高电平,B方向黄灯亮起,numB从数值4开始递减。当hold为‘1’时,表示进入紧急状态,FLASH置‘1’,各方向的红灯均亮起,所有机动车禁行。

3.3 分位模块设计

分位模块的设计主要是将灯亮时间分为十位和个位,通过两个相应的数码管分别显示出来。本设计中灯亮时间最长不超过40 s(numin<40),numA,numB分别表示十位、个位上的数字,分位模块程序设计的流程图如图5所示。

分位模块的仿真如图6所示,numin的数值大小可以通过numA,numB的组合以十进制数值显示,从而实现了分位功能。

4 系统的硬件设计及调试

本系统的主要逻辑设计由一片EPlK30TC144-3芯片完成,编写的VHDL源程序在Altera公司的逻辑综合工具Max+PlusⅡ下经过编译和功能仿真测试后,针对下载芯片进行管脚配置,下载到EPlK30TC144-3芯片中,进行相应的硬件调试,调试结果与软件仿真的结果相吻合,验证了设计完成了预定功能。

5 结 语

本文利用硬件描述语言VHDL编程,借助Altera公司的Max+PlusⅡ软件环境下进行了编译及仿真测试,通过FPGA芯片实现了一个实用的交通信号灯控制系统,设计由于采用了EDA技术,不但大大缩短了开发研制周期,提高了设计效率,而且使系统具有设计灵活,实现简单,性能稳定的特点。

举报

举报

举报

举报