近年来,随着生活水平的不断改善,个人财富日益增长,人们对安全防盗的要求也逐渐提高。安全可靠、使用方便的电子密码锁成了人们防盗的首选。以Max +PlusⅡ(Multiple Array Matrix and ProgrammingLogic User SystemⅡ,多阵列矩阵及可编程逻辑用户系统Ⅱ)为工作平台,使用PLD可编程器件和VHDL语言设计的带音乐的电子密码锁具有密码预置,误码锁死及开锁音乐提示等功能。这种设计不仅简化了系统结构,降低了成本,更提高了系统的可靠和保密性。采用PLD可编程逻辑器件开发的数字系统,可以方便地升级和改进。

1 设计思路

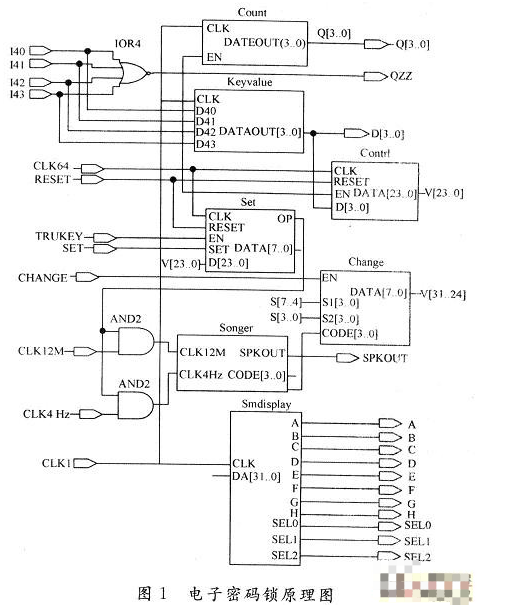

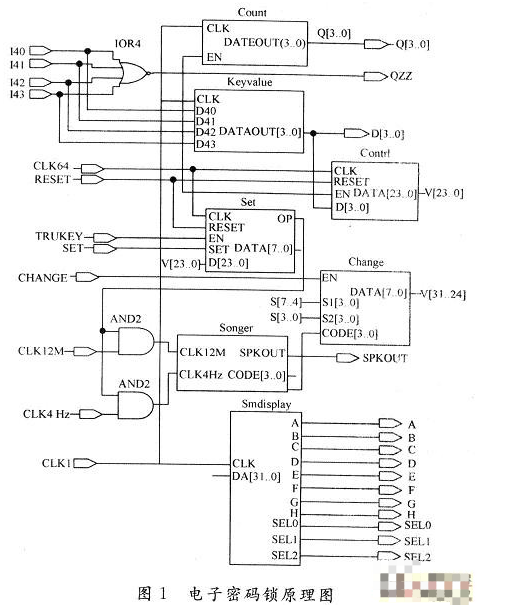

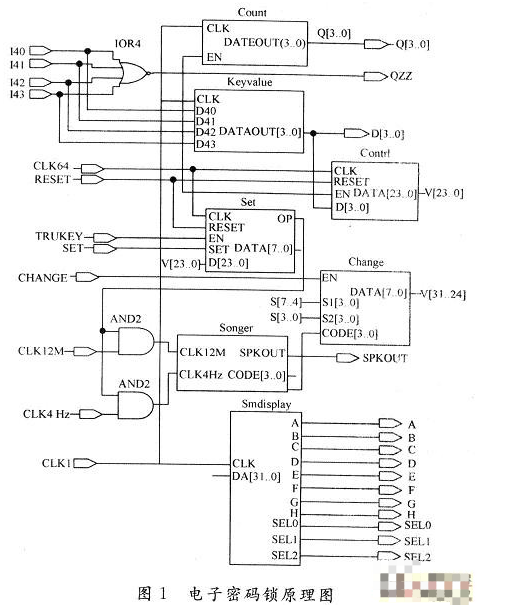

密码锁电路由键盘控制、密码设置和音乐演奏三大功能模块组成,原理如图1所示。Count,Keyvalue,Contrl,Smdisplay构成键盘控制模块,Songer是音乐演奏模块,Set是密码设置模块。

1.1 键盘控制

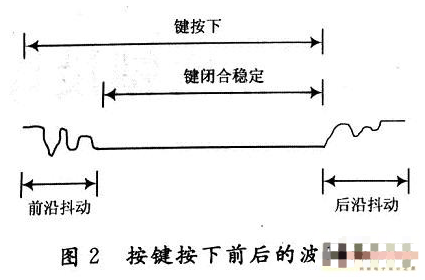

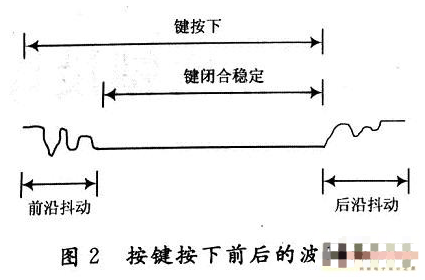

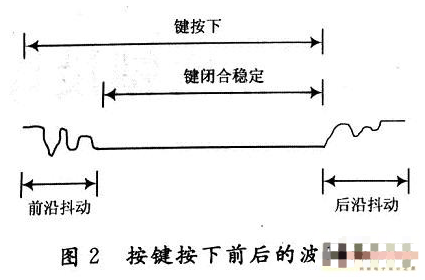

键盘主要完成向系统输入数据,传送命令等功能。它是一个机械弹性按键开关的集合,利用机械触点的合、断作用产生高、低电平。通过对电平高低状态的检测,以确认按键按下与否。一个电压信号通过机械触点的断开、闭合过程的波形如图2所示。

在该键盘电路中,Count模块提供键盘的行扫描信号Q[3..0]。在没有按键按下时,信号EN为高电平,行扫描输出信号Q[3..0]的循环变化顺序为0001 OO100100 1000 0001(依次扫描4行按键);当有按键按下时,信号EN为低电平,行扫描输出信号Q[3..0]停止扫描,并锁存当前的行扫描值。例如按下第一行的按键,那么Q[3..O]=0001。

Keyvalue模块的主要功能是对输入按键的行信号Q[3..0]和列信号14[3..0]的当前组合值进行判断来确定输入按键的键值。

Contrl模块的主要功能是实现按键的消抖,判断是否有按键按下。确保对按键的提取处于图2所示的闭合稳定时间范围内,这就对本模块的输入时钟信号有一定的要求,在本设计中该模块输入的时钟信号频率为64 Hz。Smdisplay模块主要是完成数码管动态扫描和七段译码显示的功能。

1.2 音乐演奏电路Songer

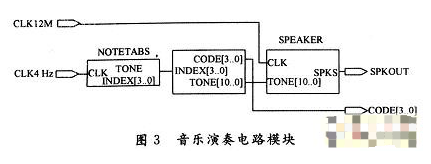

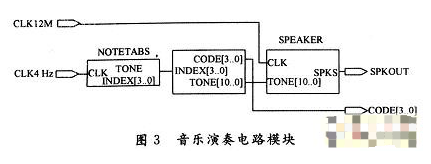

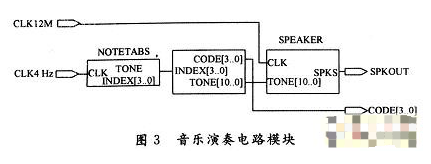

根据声乐学知识,组成乐曲的每个音符的发音频率值及其持续的时间是乐曲能连续演奏所需的两个基本要素。获得这两个要素所对应的数值以及通过纯硬件的手段来利用这些数值实现所希望乐曲的演奏效果是关键。如图3所示,该电路需要由NOTETABS(音调发生器)、TONETABA、SPEAKER(数控分频器)三个模块组成,分别实现了声音产生、节拍控制、音调控制的功能。

1.3 密码设置

Set模块是实现密码锁功能的核心模块。其主要作用是设置密码,Set为设置密码的有效信号,可以实现修改密码的功能。En为输入密码确认信号,当输入完六位密码后确认输入,一旦输入的密码跟所设置的密码一致时,则输出信号OP有效(高电平);OP控制演奏音乐,此时音乐响起。若密码不正确,则指示输入错误及输入次数,输完三次无效后密码锁锁死,必须由RESET信号(启动信号,给一个低电平)重新打开密码锁功能。

2 电路的VHDL描述

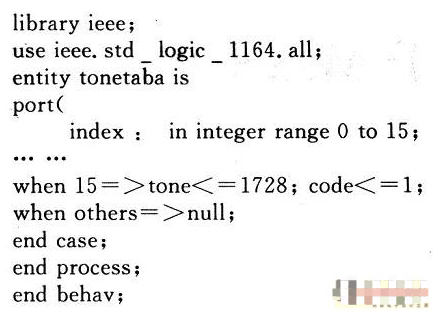

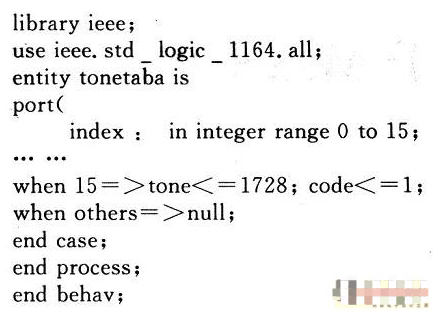

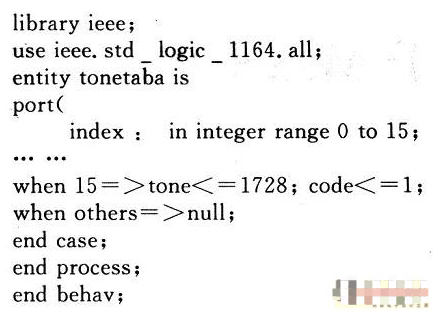

键盘控制电路,音乐演奏电路以及密码设置模块均使用硬件描述语言VHSIC Hardware Description Lan-guage(VHDL)设计而成。例如:TONETABA的VHDL模型如下:

VHDL语言具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,支持各种模式的设计方法:自顶向下与自底向上或混合方法,从而大大简化了硬件的设计任务,提高了设计效率和可靠性。它同时具有与具体硬件电路无关和与设计平台无关的特性,所以用VHDL进行电子系统设计,设计者可以专心致力于其功能的实现,而不需要对其他相关因素花费过多的时间和精力。

3 设计步骤

3.1 设计输入

首先在合适的路径下建立本设计的文件夹,然后用VHDL语言编辑Count,Keyvalue,Contrl,Smdisplay等电路,并在Max+PlusⅡ软件中使用文本编辑器输入上述各电路模块的VHDL程序,编译生成各模块;最后在Max+PlusⅡ软件中使用图形编辑器以自底向上的方法编辑原理图。先编辑图3电路,以Singer.gdf命名,其次使用“Create default Symbol”生成Songer模块,然后再编辑如图1所示原理电路图。

3.2 仿真测试及编程下载配置

将设计好的项目存盘,并将其设置成Project。选择目标器件为ACEX系列中的EP1K30QC208-2,启动编译,如果发现编译出现错误,修正后再次编译。编译后即可对波形文件进行仿真,并进行测试和波形分析。分析完成后进行编程下载配置。

3.3 硬件测试

在高电平时,通过键盘的0~F号键进行6位密码输入,密码输入完毕后通过单击确认键进行密码设置确认。当输入的密码与设置的密码一致时,扬声器开始循环演奏乐曲,且数码管SM8显示输入密码的次数,数码管SM7显示密码输入是否正确。如果密码正确,则SM7显示‘0’;如果密码错误,则SM7显示‘E’。数码管SM6~SM1显示输入的6位密码。在密码输入正确开始演奏乐曲时,如果将拨位开关KD4拨向上,则数码管SM8显示乐曲的音符,而此时若将拨位开关KD3拨向上则停止演奏乐曲。发光二极管LED1~LED4显示输入按键的键值,LED16监控是否有按键按下。

4 结 语

使用Max+PlusⅡ软件和VHDL语言设计电路,思路简单,功能明了;不仅可以进行逻辑仿真,还可以进行时序仿真;使用PLD器件不仅省去了电路制作的麻烦,还可以反复多次进行硬件实验,非常方便地修改设计,且设计的电路保密性很强。总之,采用Max+PlusⅡ软件和VHDL语言使得复杂的电子系统的设计变得简单容易,大大提高了设计效率。

近年来,随着生活水平的不断改善,个人财富日益增长,人们对安全防盗的要求也逐渐提高。安全可靠、使用方便的电子密码锁成了人们防盗的首选。以Max +PlusⅡ(Multiple Array Matrix and ProgrammingLogic User SystemⅡ,多阵列矩阵及可编程逻辑用户系统Ⅱ)为工作平台,使用PLD可编程器件和VHDL语言设计的带音乐的电子密码锁具有密码预置,误码锁死及开锁音乐提示等功能。这种设计不仅简化了系统结构,降低了成本,更提高了系统的可靠和保密性。采用PLD可编程逻辑器件开发的数字系统,可以方便地升级和改进。

1 设计思路

密码锁电路由键盘控制、密码设置和音乐演奏三大功能模块组成,原理如图1所示。Count,Keyvalue,Contrl,Smdisplay构成键盘控制模块,Songer是音乐演奏模块,Set是密码设置模块。

1.1 键盘控制

键盘主要完成向系统输入数据,传送命令等功能。它是一个机械弹性按键开关的集合,利用机械触点的合、断作用产生高、低电平。通过对电平高低状态的检测,以确认按键按下与否。一个电压信号通过机械触点的断开、闭合过程的波形如图2所示。

在该键盘电路中,Count模块提供键盘的行扫描信号Q[3..0]。在没有按键按下时,信号EN为高电平,行扫描输出信号Q[3..0]的循环变化顺序为0001 OO100100 1000 0001(依次扫描4行按键);当有按键按下时,信号EN为低电平,行扫描输出信号Q[3..0]停止扫描,并锁存当前的行扫描值。例如按下第一行的按键,那么Q[3..O]=0001。

Keyvalue模块的主要功能是对输入按键的行信号Q[3..0]和列信号14[3..0]的当前组合值进行判断来确定输入按键的键值。

Contrl模块的主要功能是实现按键的消抖,判断是否有按键按下。确保对按键的提取处于图2所示的闭合稳定时间范围内,这就对本模块的输入时钟信号有一定的要求,在本设计中该模块输入的时钟信号频率为64 Hz。Smdisplay模块主要是完成数码管动态扫描和七段译码显示的功能。

1.2 音乐演奏电路Songer

根据声乐学知识,组成乐曲的每个音符的发音频率值及其持续的时间是乐曲能连续演奏所需的两个基本要素。获得这两个要素所对应的数值以及通过纯硬件的手段来利用这些数值实现所希望乐曲的演奏效果是关键。如图3所示,该电路需要由NOTETABS(音调发生器)、TONETABA、SPEAKER(数控分频器)三个模块组成,分别实现了声音产生、节拍控制、音调控制的功能。

1.3 密码设置

Set模块是实现密码锁功能的核心模块。其主要作用是设置密码,Set为设置密码的有效信号,可以实现修改密码的功能。En为输入密码确认信号,当输入完六位密码后确认输入,一旦输入的密码跟所设置的密码一致时,则输出信号OP有效(高电平);OP控制演奏音乐,此时音乐响起。若密码不正确,则指示输入错误及输入次数,输完三次无效后密码锁锁死,必须由RESET信号(启动信号,给一个低电平)重新打开密码锁功能。

2 电路的VHDL描述

键盘控制电路,音乐演奏电路以及密码设置模块均使用硬件描述语言VHSIC Hardware Description Lan-guage(VHDL)设计而成。例如:TONETABA的VHDL模型如下:

VHDL语言具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,支持各种模式的设计方法:自顶向下与自底向上或混合方法,从而大大简化了硬件的设计任务,提高了设计效率和可靠性。它同时具有与具体硬件电路无关和与设计平台无关的特性,所以用VHDL进行电子系统设计,设计者可以专心致力于其功能的实现,而不需要对其他相关因素花费过多的时间和精力。

3 设计步骤

3.1 设计输入

首先在合适的路径下建立本设计的文件夹,然后用VHDL语言编辑Count,Keyvalue,Contrl,Smdisplay等电路,并在Max+PlusⅡ软件中使用文本编辑器输入上述各电路模块的VHDL程序,编译生成各模块;最后在Max+PlusⅡ软件中使用图形编辑器以自底向上的方法编辑原理图。先编辑图3电路,以Singer.gdf命名,其次使用“Create default Symbol”生成Songer模块,然后再编辑如图1所示原理电路图。

3.2 仿真测试及编程下载配置

将设计好的项目存盘,并将其设置成Project。选择目标器件为ACEX系列中的EP1K30QC208-2,启动编译,如果发现编译出现错误,修正后再次编译。编译后即可对波形文件进行仿真,并进行测试和波形分析。分析完成后进行编程下载配置。

3.3 硬件测试

在高电平时,通过键盘的0~F号键进行6位密码输入,密码输入完毕后通过单击确认键进行密码设置确认。当输入的密码与设置的密码一致时,扬声器开始循环演奏乐曲,且数码管SM8显示输入密码的次数,数码管SM7显示密码输入是否正确。如果密码正确,则SM7显示‘0’;如果密码错误,则SM7显示‘E’。数码管SM6~SM1显示输入的6位密码。在密码输入正确开始演奏乐曲时,如果将拨位开关KD4拨向上,则数码管SM8显示乐曲的音符,而此时若将拨位开关KD3拨向上则停止演奏乐曲。发光二极管LED1~LED4显示输入按键的键值,LED16监控是否有按键按下。

4 结 语

使用Max+PlusⅡ软件和VHDL语言设计电路,思路简单,功能明了;不仅可以进行逻辑仿真,还可以进行时序仿真;使用PLD器件不仅省去了电路制作的麻烦,还可以反复多次进行硬件实验,非常方便地修改设计,且设计的电路保密性很强。总之,采用Max+PlusⅡ软件和VHDL语言使得复杂的电子系统的设计变得简单容易,大大提高了设计效率。

1

1

举报

举报

1

1

举报

举报