随着超大规模集成电路(Very Large Scale Integration VLSI)工艺技术的发展,芯片的规模越来越大,集成规模以摩尔定律增长。现场可编程逻辑器件(FPGA)由于兼具可编程逻辑器件的现场可编程的灵活性,以及门阵列器件集成度高的优点,在数字系统设计被广泛采用。同时,ASIC技术的不断完善以及功能强大的EDA软件开发平台的出现,使得FPGA器件在现代数字系统设计和微电子技术应用中起着越来越重要的作用。近几年来,Xilinx等公司推出了内部嵌入存储器、微处理器的FPGA器件,使得这种器件的应用更显其优越性;但在某些应用场合如数据采集时,需要将采集到的数据传送给PC机,然后由PC机进行数据处理,这时就要借助单片机来完成。因此,有必要在FPGA器件中设计一种通信接口电路,以使设计的应用系统具备通信功能。由于SCI通信接口电路具有结构相对简单、易于实现等特点,因此本文以SCI接口电路为例介绍基于FPGA器件实现的接口电路IP核的设计。

SCI接口电路结构

SCI接口端口映射

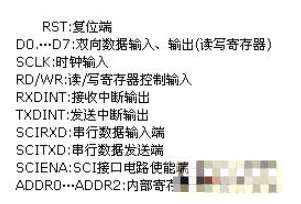

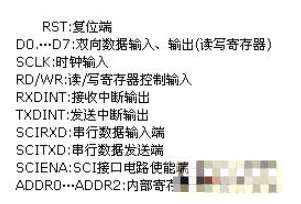

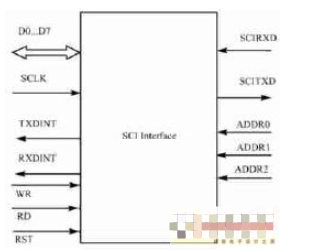

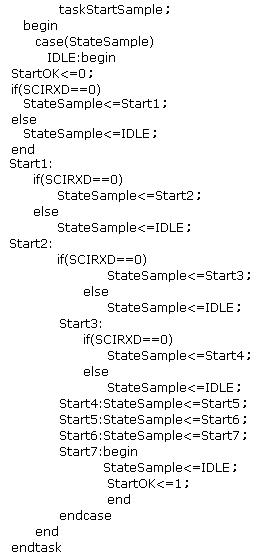

SCI的端口映射如图1所示,共有20个端口,各端口的功能为:

图1 SCI接口端口映射

SCI接口结构框图

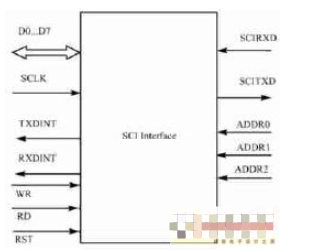

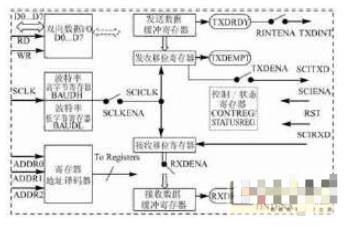

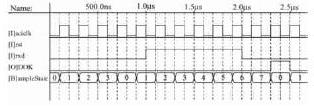

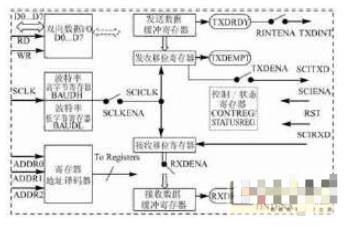

为SCI接口内部结构框图如图2所示,主要包括以下单元:

图2 SCI接口结构框图

发送器(TX)及其控制与状态寄存器。发送数据缓冲寄存器(TXBUF0…7)包含SCI接口要发送的数据;发送移位寄存器(TXSHF);发送状态寄存器位(TXRDY、TXEMPT);发送控制寄存器位(TINTENA、TXENA)。

接收器(RX)及其控制与状态寄存器。接收数据缓冲寄存器(RXBUF0…7)包含SCI接口从SCIRXD接收到的数据;接收移位寄存器(RXSHF);接收状态寄存器位(RXRDY);接收控制寄存器位(RINTENA、RXENA)。

可编程波特率发生器。由波特率高byte寄存器和波特率低byte寄存器组成,可得到64k种不同的位传输速率。当系统时钟为10MHZ时,其位传输速率为19.07~625.0kb/s。寄存器地址译码器。寄存器地址译码器负责对ADDR0…ADDR2进行译码,确保能读/写SCI中相应的寄存器。其与RD和WR配合完成对SCI内部各寄存器的读/写操作。

工作原理

数据传输格式

为简化设计,SCI以固定的串行数据格式传送数据,采用NRZ帧格式对数据进行编码,一个数据由1bit起始位、8bit数据位和一个停止bit共10bit组成。为确保采样到的数据位可靠,选取每位数据包含8个SCICLK周期。

波特率的产生

SCI内部的串行时钟(SCICLK)由系统时钟SCLK与波特率寄存器共同决定。通过16bit波特率选择寄存器,可以为内部串行时钟提供64k种不同的传输速率,其计算公式为:

Baud=SCLK/[(BRR+1)*8]其中BRR为16bit波特率选择寄存器的值。

SCI异步通信

如前所述,在异步通信模式下一帧数据包含一个起始bit、8个数据bit、一个停止bit。每个数据位占用8个SCICLK周期。

接收数据时序

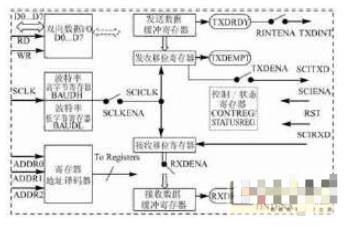

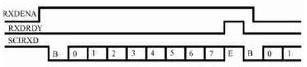

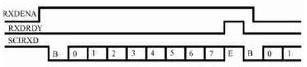

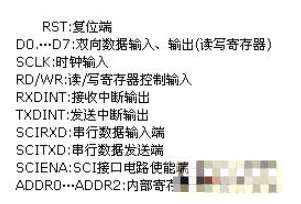

接收器在收到有效的起始位后开始操作,有效的起始位由连续的0电平组成,长度为4个连续的内部SCICLK周期。对于起始位后的各位,接收器通过对该位的中间进行3次采样来决定位值,采用在第4、第5、第6个SCICLK周期,位值取决于多数采样点的值。数据从SCIRXD进入RXSHF,移位进入RXBUF寄存器,并产生中断请求,RXDRDY置1,表示已经接收到新字符]。接收一帧数据的时序如图3所示。

图3 接收一帧数据时序

发送数据时序

发送器与接收器工作原理基本相同,在TXDRDY为低时,向发送数据缓冲寄存器写入一个数据后启动发送;然后数据进入TXSHF,同时TXDRDY为高,表示TXBUF可以写入新值,并产生一个中断请求。数据发送时序如图4所示。

图4 发送一帧数据时序

VerilogHDL实现

状态机嵌套模型

由于SCI接口牵涉到复杂的状态机描述,需要采用有限状态机的嵌套,形成树状的控制逻辑。这一点和所提倡的层次化、结构化的自顶向下的设计方法相吻合。图5是一种简单的状态机嵌套模型。

图5 状态机嵌套模型

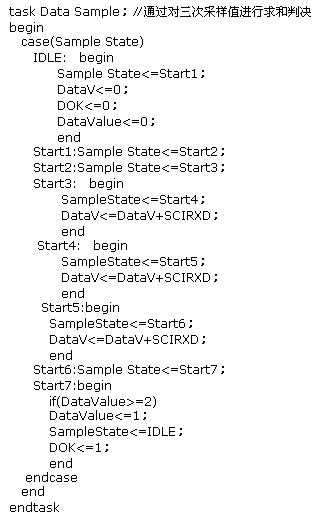

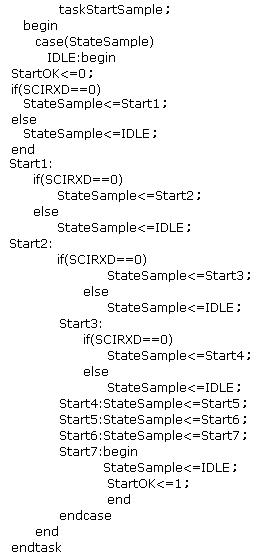

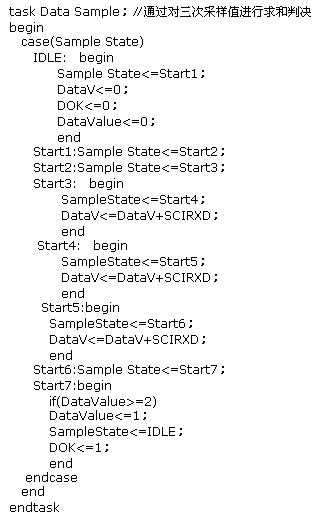

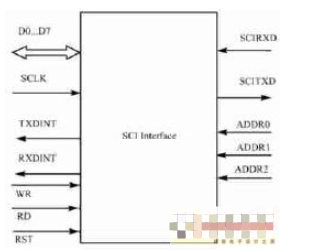

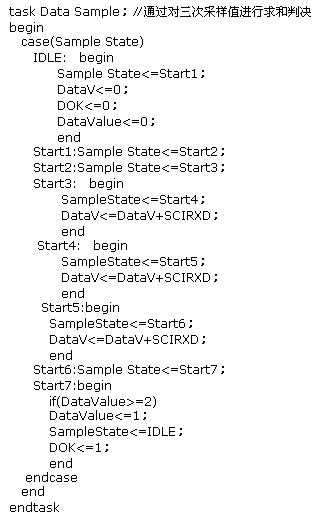

采样一位数据的状态机

接收数据起始位检测状态机

仿真结果

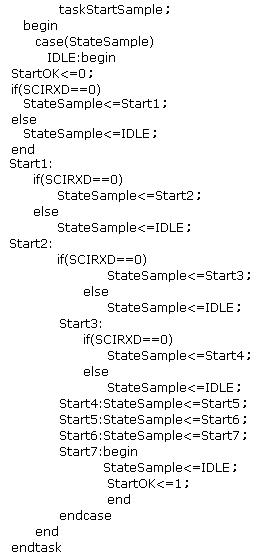

图6 起始位检测仿真波形

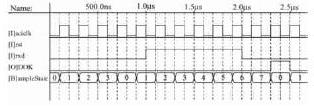

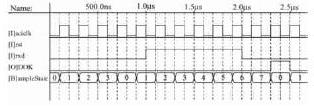

由图7仿真波形可知,采样一位数据的状态机在数据位的第4、5、6个内部sclk时钟进行。位值由多数采样的值决定,图中rxd在第4、5、6图7 采样一位数据的仿真波形个sclk时的值为1,故dok在第8个sclk时钟输出1,表示此次采样的一位数据为1。

图7 采样一位数据的仿真波形

结论

SCI接口电路由VerilogHDL语言描述,可读性好,便于修改与测试,可方便地嵌入到用户的FPGA系统。笔者利用Xilinx公司的Spartan ⅡFPGAXC2S100成功地实现了FPGA与PC机的串行通信。如在此基础上增加其它的控制寄存器,则可设计出功能更为完善的SCI接口电路。

随着超大规模集成电路(Very Large Scale Integration VLSI)工艺技术的发展,芯片的规模越来越大,集成规模以摩尔定律增长。现场可编程逻辑器件(FPGA)由于兼具可编程逻辑器件的现场可编程的灵活性,以及门阵列器件集成度高的优点,在数字系统设计被广泛采用。同时,ASIC技术的不断完善以及功能强大的EDA软件开发平台的出现,使得FPGA器件在现代数字系统设计和微电子技术应用中起着越来越重要的作用。近几年来,Xilinx等公司推出了内部嵌入存储器、微处理器的FPGA器件,使得这种器件的应用更显其优越性;但在某些应用场合如数据采集时,需要将采集到的数据传送给PC机,然后由PC机进行数据处理,这时就要借助单片机来完成。因此,有必要在FPGA器件中设计一种通信接口电路,以使设计的应用系统具备通信功能。由于SCI通信接口电路具有结构相对简单、易于实现等特点,因此本文以SCI接口电路为例介绍基于FPGA器件实现的接口电路IP核的设计。

SCI接口电路结构

SCI接口端口映射

SCI的端口映射如图1所示,共有20个端口,各端口的功能为:

图1 SCI接口端口映射

SCI接口结构框图

为SCI接口内部结构框图如图2所示,主要包括以下单元:

图2 SCI接口结构框图

发送器(TX)及其控制与状态寄存器。发送数据缓冲寄存器(TXBUF0…7)包含SCI接口要发送的数据;发送移位寄存器(TXSHF);发送状态寄存器位(TXRDY、TXEMPT);发送控制寄存器位(TINTENA、TXENA)。

接收器(RX)及其控制与状态寄存器。接收数据缓冲寄存器(RXBUF0…7)包含SCI接口从SCIRXD接收到的数据;接收移位寄存器(RXSHF);接收状态寄存器位(RXRDY);接收控制寄存器位(RINTENA、RXENA)。

可编程波特率发生器。由波特率高byte寄存器和波特率低byte寄存器组成,可得到64k种不同的位传输速率。当系统时钟为10MHZ时,其位传输速率为19.07~625.0kb/s。寄存器地址译码器。寄存器地址译码器负责对ADDR0…ADDR2进行译码,确保能读/写SCI中相应的寄存器。其与RD和WR配合完成对SCI内部各寄存器的读/写操作。

工作原理

数据传输格式

为简化设计,SCI以固定的串行数据格式传送数据,采用NRZ帧格式对数据进行编码,一个数据由1bit起始位、8bit数据位和一个停止bit共10bit组成。为确保采样到的数据位可靠,选取每位数据包含8个SCICLK周期。

波特率的产生

SCI内部的串行时钟(SCICLK)由系统时钟SCLK与波特率寄存器共同决定。通过16bit波特率选择寄存器,可以为内部串行时钟提供64k种不同的传输速率,其计算公式为:

Baud=SCLK/[(BRR+1)*8]其中BRR为16bit波特率选择寄存器的值。

SCI异步通信

如前所述,在异步通信模式下一帧数据包含一个起始bit、8个数据bit、一个停止bit。每个数据位占用8个SCICLK周期。

接收数据时序

接收器在收到有效的起始位后开始操作,有效的起始位由连续的0电平组成,长度为4个连续的内部SCICLK周期。对于起始位后的各位,接收器通过对该位的中间进行3次采样来决定位值,采用在第4、第5、第6个SCICLK周期,位值取决于多数采样点的值。数据从SCIRXD进入RXSHF,移位进入RXBUF寄存器,并产生中断请求,RXDRDY置1,表示已经接收到新字符]。接收一帧数据的时序如图3所示。

图3 接收一帧数据时序

发送数据时序

发送器与接收器工作原理基本相同,在TXDRDY为低时,向发送数据缓冲寄存器写入一个数据后启动发送;然后数据进入TXSHF,同时TXDRDY为高,表示TXBUF可以写入新值,并产生一个中断请求。数据发送时序如图4所示。

图4 发送一帧数据时序

VerilogHDL实现

状态机嵌套模型

由于SCI接口牵涉到复杂的状态机描述,需要采用有限状态机的嵌套,形成树状的控制逻辑。这一点和所提倡的层次化、结构化的自顶向下的设计方法相吻合。图5是一种简单的状态机嵌套模型。

图5 状态机嵌套模型

采样一位数据的状态机

接收数据起始位检测状态机

仿真结果

图6 起始位检测仿真波形

由图7仿真波形可知,采样一位数据的状态机在数据位的第4、5、6个内部sclk时钟进行。位值由多数采样的值决定,图中rxd在第4、5、6图7 采样一位数据的仿真波形个sclk时的值为1,故dok在第8个sclk时钟输出1,表示此次采样的一位数据为1。

图7 采样一位数据的仿真波形

结论

SCI接口电路由VerilogHDL语言描述,可读性好,便于修改与测试,可方便地嵌入到用户的FPGA系统。笔者利用Xilinx公司的Spartan ⅡFPGAXC2S100成功地实现了FPGA与PC机的串行通信。如在此基础上增加其它的控制寄存器,则可设计出功能更为完善的SCI接口电路。

举报

举报

举报

举报