软件无线电是一种基于宽带A/D器件、高速DSP芯片,以软件为核心(Software-Oriented 的崭新的体系结构。其基本思想就是将宽带A/D尽可能地靠近射频天线以便将接收到的模拟信号尽可能早地数字化,尽量通过软件来实现电台的各种功能。通过运行不同的算法,软件无线电可以实时地配置信号波形,使它能够提供各种话音编码、信道调制、加密算法等无线电通信业务。我们知道信号失真是长期困扰模拟处理的难题,如本振频率漂移、相位噪声、混频产生的虚假信号、放大时产生的谐波以及互调、机内噪声等问题。尽管设计人员想方设法,但结果并不能令人满意,而软件无线电技术简单有效地解决了这些问题。在数字化之后,本振、混频、放大、滤波都仅仅是数字运算,不会产生谐波、互调等虚假信号。与传统的模拟方式相比,软件无线电具有灵活性、适应性和开放性等特点,被誉为无线电领域的又一次革命。

1 接收机总体设计

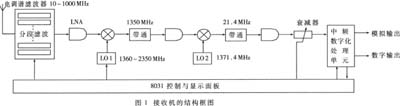

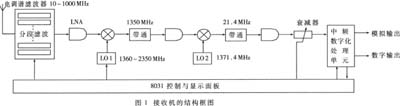

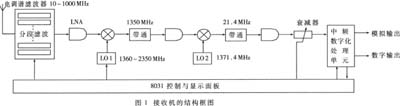

由于受器件水平的制约,直接对射频采样处理还有一定难度。在保留软件无线电通用、灵活、开放的前提下,采用了中频数化方案1,整个接收机的结构框图如图1所示。

该接收机接收信号频率范围:10~100MHz,为防止频谱混叠,前端电调谐滤波器分为8段滤波器,由8031控制选用。第一本振LO1采用数字锁相环产生所需频率,通过预置,可产生正弦信号频率范围:1360~2350MHz,步进值10Hz,电调谐滤波器与一本振互动联调。混频后,将信号通过一中心频率为1350MHz的带通滤波器后,进行二次混频。第二本振LO2产生信号的频率固定设置为:1371.4MHz,因此中频信号为:21.4MHz,通过AGC控制输出信号强度范围为:-50~-10dBm/50Ω。

2 中频数字化单元设计

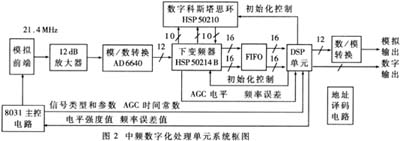

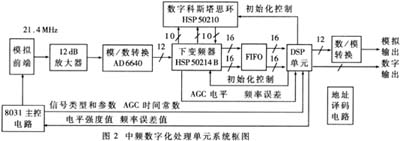

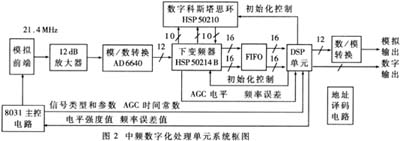

该单元是接收机的核心部件,主要完成几种信号(AM、FM、SSB、CW、FSK、BPSK,QPSK)的解调工作,同时负责对模拟前端提供AGC控制用电平强度值和AFC控制用载波频率误差值。8031主控电路板则要为中频数字化单元提供:信号类型、中频带宽、AGC时间常数、BFO值、PSK信号波特率等控制命令。中频数字化处理单元硬件系统大体构成如图2所示1。

2.1 数据采集部分

该部分电路主要由数控放大器和模/数转换器AD6640构成,负责完成数据采集工作。固定增益放大器18dB的中频输入信号为:(21.4MHz,-50~-10dBm/50Ω 0.7mV~70mV),输出为(-38dBm~+2dBm/50Ω?2.8mV~0.4V)。AD6640是AD公司生产的新一代模数转换器件,分辨率12bit,输入动态范围±1V,采样速率可达65Msps,在5V供电时功耗仅为710mW。注意A/D前采用固定增益放大电路,并不影响对模拟接收机的AGC输出。因该放大电路的增益是已知的,检测出信号电平后可以倒推出放大前的电平变化情况。至于采样速率的确定,此处既可以采用过采样又可以采用欠采样技术。所谓欠采样技术就是对于带通信号(频率范围:fL<f<Fh=而言,抽样频率只要满足:≤fs≤

(K为整数且2≤K≤ fH-fL≤fL 就可保证采样后的频谱不产生折叠。这对于减小运算量是很有好处的,但对接收机抗混叠滤波器要求较高。考虑到HSP50214B处理速率高达65MSPS,可以采用过采样技术。根据理论上的ADC的信噪比计算公式:SNR=6.02M+1.7Db+10log10可知:抽样速率每增加一倍,信噪比大约可提高3dB。因此,在速率允许的情况下,我们仍决定采用过采样技术,采样频率50MHz。

2.2 数字下变频单元

数字下变频单元由美国Harris生产的专用可编程下变频器HSP50214B和专用可编程数字科斯塔司环电路HSP50210构成。HSP50214B大体可分成13个部分3(见图3),

主要功能是将IF数据下变频成基带数据。其前端处理速度高达65Msps,后端处理速度最高达55Msps。总的抽取因子范围:4~16384,输出采样速率可达12.94Msps,输出低通带宽最宽为982kHz(IF带宽1.96MHz)。最高支持14bits字长的数据并行输入,输出形式灵活多样,既可并行输出又可串行输出,既可选择直角坐标数据输出又能选择极坐标数据输出,可选择输出幅度、瞬时相位和频率等参数。另外,HSP50214B还内带电平检测器,可为IF自动增益控制提供支持。总之,HSP50214B功能非常强大,使用相当灵活,可以解调AM、FM、FSK信号。与HSP50210一起使用,还可以解调SSB和PSK信号。

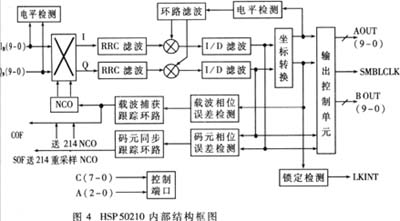

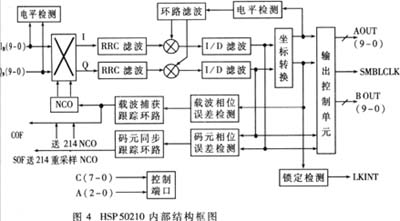

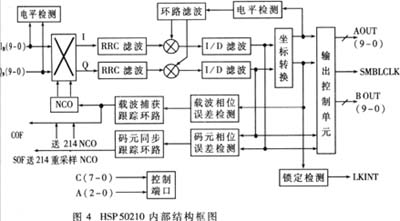

HSP50210是Harris公司生产的数字科斯塔司环专用电路,其功能也很强大。时钟处理速率高达52MHz,内部具有以下功能模块4(见图4):(1)可选升余弦匹配滤波器/积分和去除滤波器(I/D滤波器);(2)二阶载波和码元跟踪滤波器;(3)自动增益控制电路;(4)鉴频器;(5)锁定检测器;(6)数据质量和信号电平检测电路;(7)直角坐标向极坐标转化电路;(8)8-Bits微机控制接口。

主要用HSP50210来提取相干载波、码元同步信号和载波跟踪情况指示。其内部的AGC环路、内部NCO载波跟踪、混频电路及RRC滤波器等均旁路不用。由于HSP50210需要HSP50214B提供两路正交数据,而其每一路数据长度只有10bits,因此要注意数据匹配问题。注意:载波跟踪误差COF利用同步信号COFSYNC串行送给214B的NCO,码元跟踪误差SOF利用同步信号SOFSYNC串行送给214B的重采样NCO,所以214B和210必须采用统一时钟才能保证同步传送数据不出问题。

2.3 DSP单元

DSP单元采用美国TI公司生产的TMS320C542专用数字信号处理芯片和外部程序扩展存储器以及数据扩展存储器组成。C542定点DSP芯片,处理速度最高可达40MIPS,可以满足实时处理要求。主要完成工作:接收8031送过来的命令,根据命令完成对HSP50214B和HSP50210的初始化设置工作。当FIFO半满时申请DSP的/INT1中断,DSP响应中断读入1024个数据,做必要的处理后根据信号类型送出。程序定期查询8031有无新命令送过来,如有则根据新命令重新设置214B和210的相关参数,否则继续执行原来的接收程序。根据AGC时间常数,从214B读取电平检测值和频率偏移送8031,作为模拟部分的调整依据。

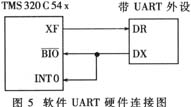

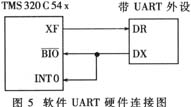

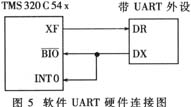

TMS320C54x只有高速同步串行通信接口,无法直接与8031进行异步通信。采用软件模拟UART方式较好地解决了这个问题2。该方法无需额外硬件开销,仅仅需要两个通用I/O脚(BIO和XF)、外部中断INT0以及一个定时器就可实现,硬件连接非常简单(见图5)。

图5中,XF脚用于发送数据,脚和INT0脚用于接收数据。此方法可以模拟半双工通信与全双工通信。软件模拟UART技术允许用户设置:

·数据位数(1~16);

·奇偶校验(奇校验或偶校验)或无奇偶校验;

·停止位(1~2);

·波特率。

2.4 控制单元

控制单元主要包括:地址译码电路和与主控电路板上的8031单片机通信控制接口。译码电路采用EPLD(EPM7128SQC-7)实现,以保护电路的灵活性。与8031通信采用串口通信方式,优点是接口简单,调试方便,传输速率(采用RS-232C接口串行总线标准)20kb/s。

2.5 输出单元

输出单元主要包括模拟信号输出和数字信号输出两部分。模拟输出电路主要负责AM、SSB、FM、FSK信号的输出。数字输出端口负责输出B/QPSK信号(I,Q两路数据和同步时钟)。

由于该接收机从中频21.4MHz后采用了全数字设计,在模拟前端采用了电调谐预选滤波器与一本振之间的互动联调(二者可通过8031设置),因而具有极大的灵活性。通过加载不同软件,对模拟部分进行相应控制,本接收机可在10~1000MHz的范围内实现对AM、FM、SSB、CW、FSK、BPSK、QPSK的解调。实验测试表明:接收效果良好,控制灵活,适应范围广,具有较好的开放性。

软件无线电是一种基于宽带A/D器件、高速DSP芯片,以软件为核心(Software-Oriented 的崭新的体系结构。其基本思想就是将宽带A/D尽可能地靠近射频天线以便将接收到的模拟信号尽可能早地数字化,尽量通过软件来实现电台的各种功能。通过运行不同的算法,软件无线电可以实时地配置信号波形,使它能够提供各种话音编码、信道调制、加密算法等无线电通信业务。我们知道信号失真是长期困扰模拟处理的难题,如本振频率漂移、相位噪声、混频产生的虚假信号、放大时产生的谐波以及互调、机内噪声等问题。尽管设计人员想方设法,但结果并不能令人满意,而软件无线电技术简单有效地解决了这些问题。在数字化之后,本振、混频、放大、滤波都仅仅是数字运算,不会产生谐波、互调等虚假信号。与传统的模拟方式相比,软件无线电具有灵活性、适应性和开放性等特点,被誉为无线电领域的又一次革命。

1 接收机总体设计

由于受器件水平的制约,直接对射频采样处理还有一定难度。在保留软件无线电通用、灵活、开放的前提下,采用了中频数化方案1,整个接收机的结构框图如图1所示。

该接收机接收信号频率范围:10~100MHz,为防止频谱混叠,前端电调谐滤波器分为8段滤波器,由8031控制选用。第一本振LO1采用数字锁相环产生所需频率,通过预置,可产生正弦信号频率范围:1360~2350MHz,步进值10Hz,电调谐滤波器与一本振互动联调。混频后,将信号通过一中心频率为1350MHz的带通滤波器后,进行二次混频。第二本振LO2产生信号的频率固定设置为:1371.4MHz,因此中频信号为:21.4MHz,通过AGC控制输出信号强度范围为:-50~-10dBm/50Ω。

2 中频数字化单元设计

该单元是接收机的核心部件,主要完成几种信号(AM、FM、SSB、CW、FSK、BPSK,QPSK)的解调工作,同时负责对模拟前端提供AGC控制用电平强度值和AFC控制用载波频率误差值。8031主控电路板则要为中频数字化单元提供:信号类型、中频带宽、AGC时间常数、BFO值、PSK信号波特率等控制命令。中频数字化处理单元硬件系统大体构成如图2所示1。

2.1 数据采集部分

该部分电路主要由数控放大器和模/数转换器AD6640构成,负责完成数据采集工作。固定增益放大器18dB的中频输入信号为:(21.4MHz,-50~-10dBm/50Ω 0.7mV~70mV),输出为(-38dBm~+2dBm/50Ω?2.8mV~0.4V)。AD6640是AD公司生产的新一代模数转换器件,分辨率12bit,输入动态范围±1V,采样速率可达65Msps,在5V供电时功耗仅为710mW。注意A/D前采用固定增益放大电路,并不影响对模拟接收机的AGC输出。因该放大电路的增益是已知的,检测出信号电平后可以倒推出放大前的电平变化情况。至于采样速率的确定,此处既可以采用过采样又可以采用欠采样技术。所谓欠采样技术就是对于带通信号(频率范围:fL<f<Fh=而言,抽样频率只要满足:≤fs≤

(K为整数且2≤K≤ fH-fL≤fL 就可保证采样后的频谱不产生折叠。这对于减小运算量是很有好处的,但对接收机抗混叠滤波器要求较高。考虑到HSP50214B处理速率高达65MSPS,可以采用过采样技术。根据理论上的ADC的信噪比计算公式:SNR=6.02M+1.7Db+10log10可知:抽样速率每增加一倍,信噪比大约可提高3dB。因此,在速率允许的情况下,我们仍决定采用过采样技术,采样频率50MHz。

2.2 数字下变频单元

数字下变频单元由美国Harris生产的专用可编程下变频器HSP50214B和专用可编程数字科斯塔司环电路HSP50210构成。HSP50214B大体可分成13个部分3(见图3),

主要功能是将IF数据下变频成基带数据。其前端处理速度高达65Msps,后端处理速度最高达55Msps。总的抽取因子范围:4~16384,输出采样速率可达12.94Msps,输出低通带宽最宽为982kHz(IF带宽1.96MHz)。最高支持14bits字长的数据并行输入,输出形式灵活多样,既可并行输出又可串行输出,既可选择直角坐标数据输出又能选择极坐标数据输出,可选择输出幅度、瞬时相位和频率等参数。另外,HSP50214B还内带电平检测器,可为IF自动增益控制提供支持。总之,HSP50214B功能非常强大,使用相当灵活,可以解调AM、FM、FSK信号。与HSP50210一起使用,还可以解调SSB和PSK信号。

HSP50210是Harris公司生产的数字科斯塔司环专用电路,其功能也很强大。时钟处理速率高达52MHz,内部具有以下功能模块4(见图4):(1)可选升余弦匹配滤波器/积分和去除滤波器(I/D滤波器);(2)二阶载波和码元跟踪滤波器;(3)自动增益控制电路;(4)鉴频器;(5)锁定检测器;(6)数据质量和信号电平检测电路;(7)直角坐标向极坐标转化电路;(8)8-Bits微机控制接口。

主要用HSP50210来提取相干载波、码元同步信号和载波跟踪情况指示。其内部的AGC环路、内部NCO载波跟踪、混频电路及RRC滤波器等均旁路不用。由于HSP50210需要HSP50214B提供两路正交数据,而其每一路数据长度只有10bits,因此要注意数据匹配问题。注意:载波跟踪误差COF利用同步信号COFSYNC串行送给214B的NCO,码元跟踪误差SOF利用同步信号SOFSYNC串行送给214B的重采样NCO,所以214B和210必须采用统一时钟才能保证同步传送数据不出问题。

2.3 DSP单元

DSP单元采用美国TI公司生产的TMS320C542专用数字信号处理芯片和外部程序扩展存储器以及数据扩展存储器组成。C542定点DSP芯片,处理速度最高可达40MIPS,可以满足实时处理要求。主要完成工作:接收8031送过来的命令,根据命令完成对HSP50214B和HSP50210的初始化设置工作。当FIFO半满时申请DSP的/INT1中断,DSP响应中断读入1024个数据,做必要的处理后根据信号类型送出。程序定期查询8031有无新命令送过来,如有则根据新命令重新设置214B和210的相关参数,否则继续执行原来的接收程序。根据AGC时间常数,从214B读取电平检测值和频率偏移送8031,作为模拟部分的调整依据。

TMS320C54x只有高速同步串行通信接口,无法直接与8031进行异步通信。采用软件模拟UART方式较好地解决了这个问题2。该方法无需额外硬件开销,仅仅需要两个通用I/O脚(BIO和XF)、外部中断INT0以及一个定时器就可实现,硬件连接非常简单(见图5)。

图5中,XF脚用于发送数据,脚和INT0脚用于接收数据。此方法可以模拟半双工通信与全双工通信。软件模拟UART技术允许用户设置:

·数据位数(1~16);

·奇偶校验(奇校验或偶校验)或无奇偶校验;

·停止位(1~2);

·波特率。

2.4 控制单元

控制单元主要包括:地址译码电路和与主控电路板上的8031单片机通信控制接口。译码电路采用EPLD(EPM7128SQC-7)实现,以保护电路的灵活性。与8031通信采用串口通信方式,优点是接口简单,调试方便,传输速率(采用RS-232C接口串行总线标准)20kb/s。

2.5 输出单元

输出单元主要包括模拟信号输出和数字信号输出两部分。模拟输出电路主要负责AM、SSB、FM、FSK信号的输出。数字输出端口负责输出B/QPSK信号(I,Q两路数据和同步时钟)。

由于该接收机从中频21.4MHz后采用了全数字设计,在模拟前端采用了电调谐预选滤波器与一本振之间的互动联调(二者可通过8031设置),因而具有极大的灵活性。通过加载不同软件,对模拟部分进行相应控制,本接收机可在10~1000MHz的范围内实现对AM、FM、SSB、CW、FSK、BPSK、QPSK的解调。实验测试表明:接收效果良好,控制灵活,适应范围广,具有较好的开放性。

举报

举报

举报

举报