1 概述

近年来,随着数字信号处理技术的迅速发展和新理论、新算法的不断涌现,加之数字信号处理器件性能的全面提高,使实际系统对模数转换器的要求越来越高。因此,在实际的应用中,一般都要求模数转换器必须同时具备很高的采样率和精度、很大的动态范围、极宽的频率响应范围和灵活的数字接口。

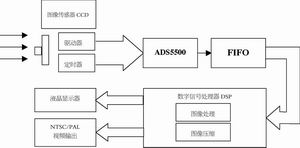

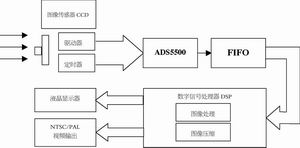

ADS5500是TI公司开发的一款14位分辨率、125Msps采样速率的高性能模数转换器,芯片为64引脚TQFP PowerPAD封装。为实现更高的系统集成度,其内部还包括有宽带宽的线性采样/保持和内部基准电压源的完整转换解决方案。100MHz时ADS5500的信噪比(SNR)为70dB,无失真动态范围(SFDR)为82dB,差分输入电压为2.2Vpp,工作电压为3.3V(单极性),且功耗仅为750mW。内部基准电压源简化了系统设计,并行CMOS兼容数据输出接口确保了与普通逻辑电路的无缝连接,方便了与数字信号处理器的连接。其内部结构框图示于图1。

图1 ADS5500的内部结构框图

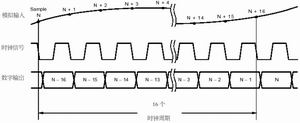

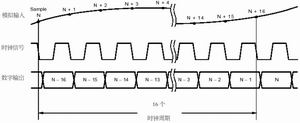

图2 ADS5500工作信号时序

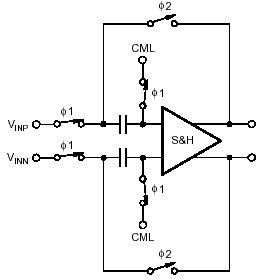

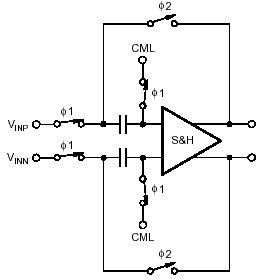

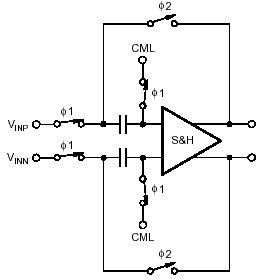

图3 模拟输入部分

2 设计考虑

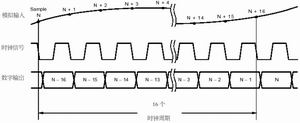

ADS5500是一款低功耗、采样率为125MSPS的14位流水线模数转换器,仅需一个3.3V的单极性电源就可正常工作。数据转换过程启动于时钟信号波形的上升沿,一旦模拟信号被转换器的采样/保持部分捕获后,输入信号的采样过程被依序分割为一系列的流水线操作,使时钟信号的上升沿和下降沿都能进行数据的转换工作。从输入模拟信号到输出14位的数据需要16个时钟周期的延迟。图2给出了ADS5500输入、输出信号和时钟波形的对应时序。

3 输入配置

ADS5500的模拟输入部分主要由一个差分跟踪/保持放大器和开关电容组成(图3)。

差分输入技术确保了高采样率条件下的高性能,同时也带来了非常高的可用输入带宽,这一点对于某些中频采样或欠采样应用尤为重要。

对于低频输入信号的输入配置可以采用差分输入/输出放大器(如OPA695),用来简化前端驱动电路。这种配置的优点在于其具有较大的灵活性,放大器可用来完成模拟输入信号的极性转换(单极性~差分)、信号放大及ADC的前端预滤波等工作。

4 基准源电路

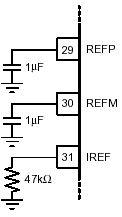

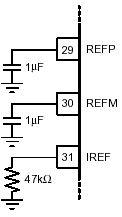

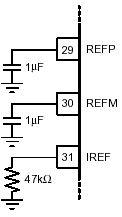

ADS5500的内基准电压源简化了电路板的电路布局,对此,板上可不用其它附加电路。但从优化性能的角度考虑,可在REFP和REFM引脚上各连接1个1mF的电容器并接地。此外,为更好设置芯片的工作电流,还应在IREF引脚上连接1个47Ω的电阻,并与AGND引脚相连(图4)。

图4 REFP、REFM和IREF引脚优化系统性能

图5 时钟输入信号引脚连接电路

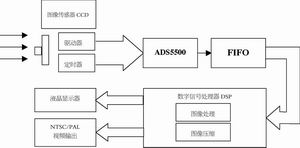

图6 ADS5500构建实时图像处理系统

5 时钟输入信号

芯片的时钟输入信号可以是单极性或差分信号,普通模式下,时钟输入信号的电压幅值设置为1.5V,CLKP引脚、CLKM引脚各通过5kΩ电阻与CM引脚相连(图5)。

从实用角度考虑,选用低抖动时钟源并对其进行相应的带通滤波可大大提高高频采样系统性能。芯片内部的ADC内核在时钟信号波形的上升沿和下降沿都能进行数据转换,进一步提高了芯片的工作效率。当无时钟源或时钟频率低于10MSPS时,芯片将自动切换至休眠模式。

6 输出选项

芯片产生14位的数据输出信号(D13-D0),1个数据就绪信号(CLKOUT引脚)和1个数据溢出指示位(OVR引脚,当输出数据幅值超过最大值时,该位被置为1)。

通过改变DFS引脚电平可设置输出信号的数据格式和时钟输出信号的极性。输出信号的数据格式有直接二进制码和二进制补码两种形式,而时钟极性则表现为输出数据在时钟波形上升沿或下降沿有效。DFS引脚电平有四种选择范围,因而就有四种对应关系。表1给出了这四种模式的对应关系。

7 应用举例

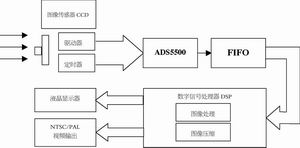

图6是一个实时图像处理系统,CCD传感器把原始图像(模拟信号)送至ADS5500高频采样,得到高精度的数字图像信号,再通过高速同步FIFO送入到图像处理单元,由数字信号处理器完成图像的处理和压缩,并将处理后的数据显示在液晶显示器或CRT显示器上。

8 结语

ADS5500接口简单,使用方便、灵活,14位采样精度,同时又有很高的转换速度。在大多数需要高速数据采集和高精度测量的应用场合中,该芯片具有很强的实用性。

1 概述

近年来,随着数字信号处理技术的迅速发展和新理论、新算法的不断涌现,加之数字信号处理器件性能的全面提高,使实际系统对模数转换器的要求越来越高。因此,在实际的应用中,一般都要求模数转换器必须同时具备很高的采样率和精度、很大的动态范围、极宽的频率响应范围和灵活的数字接口。

ADS5500是TI公司开发的一款14位分辨率、125Msps采样速率的高性能模数转换器,芯片为64引脚TQFP PowerPAD封装。为实现更高的系统集成度,其内部还包括有宽带宽的线性采样/保持和内部基准电压源的完整转换解决方案。100MHz时ADS5500的信噪比(SNR)为70dB,无失真动态范围(SFDR)为82dB,差分输入电压为2.2Vpp,工作电压为3.3V(单极性),且功耗仅为750mW。内部基准电压源简化了系统设计,并行CMOS兼容数据输出接口确保了与普通逻辑电路的无缝连接,方便了与数字信号处理器的连接。其内部结构框图示于图1。

图1 ADS5500的内部结构框图

图2 ADS5500工作信号时序

图3 模拟输入部分

2 设计考虑

ADS5500是一款低功耗、采样率为125MSPS的14位流水线模数转换器,仅需一个3.3V的单极性电源就可正常工作。数据转换过程启动于时钟信号波形的上升沿,一旦模拟信号被转换器的采样/保持部分捕获后,输入信号的采样过程被依序分割为一系列的流水线操作,使时钟信号的上升沿和下降沿都能进行数据的转换工作。从输入模拟信号到输出14位的数据需要16个时钟周期的延迟。图2给出了ADS5500输入、输出信号和时钟波形的对应时序。

3 输入配置

ADS5500的模拟输入部分主要由一个差分跟踪/保持放大器和开关电容组成(图3)。

差分输入技术确保了高采样率条件下的高性能,同时也带来了非常高的可用输入带宽,这一点对于某些中频采样或欠采样应用尤为重要。

对于低频输入信号的输入配置可以采用差分输入/输出放大器(如OPA695),用来简化前端驱动电路。这种配置的优点在于其具有较大的灵活性,放大器可用来完成模拟输入信号的极性转换(单极性~差分)、信号放大及ADC的前端预滤波等工作。

4 基准源电路

ADS5500的内基准电压源简化了电路板的电路布局,对此,板上可不用其它附加电路。但从优化性能的角度考虑,可在REFP和REFM引脚上各连接1个1mF的电容器并接地。此外,为更好设置芯片的工作电流,还应在IREF引脚上连接1个47Ω的电阻,并与AGND引脚相连(图4)。

图4 REFP、REFM和IREF引脚优化系统性能

图5 时钟输入信号引脚连接电路

图6 ADS5500构建实时图像处理系统

5 时钟输入信号

芯片的时钟输入信号可以是单极性或差分信号,普通模式下,时钟输入信号的电压幅值设置为1.5V,CLKP引脚、CLKM引脚各通过5kΩ电阻与CM引脚相连(图5)。

从实用角度考虑,选用低抖动时钟源并对其进行相应的带通滤波可大大提高高频采样系统性能。芯片内部的ADC内核在时钟信号波形的上升沿和下降沿都能进行数据转换,进一步提高了芯片的工作效率。当无时钟源或时钟频率低于10MSPS时,芯片将自动切换至休眠模式。

6 输出选项

芯片产生14位的数据输出信号(D13-D0),1个数据就绪信号(CLKOUT引脚)和1个数据溢出指示位(OVR引脚,当输出数据幅值超过最大值时,该位被置为1)。

通过改变DFS引脚电平可设置输出信号的数据格式和时钟输出信号的极性。输出信号的数据格式有直接二进制码和二进制补码两种形式,而时钟极性则表现为输出数据在时钟波形上升沿或下降沿有效。DFS引脚电平有四种选择范围,因而就有四种对应关系。表1给出了这四种模式的对应关系。

7 应用举例

图6是一个实时图像处理系统,CCD传感器把原始图像(模拟信号)送至ADS5500高频采样,得到高精度的数字图像信号,再通过高速同步FIFO送入到图像处理单元,由数字信号处理器完成图像的处理和压缩,并将处理后的数据显示在液晶显示器或CRT显示器上。

8 结语

ADS5500接口简单,使用方便、灵活,14位采样精度,同时又有很高的转换速度。在大多数需要高速数据采集和高精度测量的应用场合中,该芯片具有很强的实用性。

举报

举报

举报

举报