在雷达系统研制过程中,回波信号模拟器是不可缺少的设备,它可以灵活地产生雷达在各种工作状态下的回波信号,有助于雷达的实验室调试,降低试验成本,增加灵活性,对其设计、改进、定型都有重要意义。

本文设计的面目标模拟器基于波形存储直读的DDWS(直接数字波形合成)法实现,模拟成像雷达接收其自身发射的单个射频线性调频脉冲,经复杂的地面目标反射后,形成的射频回波信号经下变频后输出。DSWS就是将预先存储的经理想采样的数字波形直接进行D/A转换而得到所需的模拟信号。该模拟器采用波形存储直读法产生基带I/Q信号,经正交调制产生中频,最大带宽80 MHz,可直接输出视频信号和中频信号。该面目标模拟器具有较大的数据存储空间和高精度的输出时刻控制。设计中对I、Q路基带数据进行存储,单路存储空间256 Mbit(32 MB),总存储空间64 MB,可以满足大多数需求;通过进行延时补偿使得输出信号输出时刻精确可控。

该模拟器采用USB接口加载回波数据,可通过计算机方便地修改波形数据。加载理想数据对信号处理机进行功能验证,又可以加载实验数据实现真实目标场景再现、进行设备出厂前的系统联调。系统核心控制单元采用Xilinx公司的VirtexⅡ系列XC2V500型FPGA(现场可编程门阵列),完成系统的功能控制、高精度延时计算、数据存储控制等关键任务。

1 系统结构描述

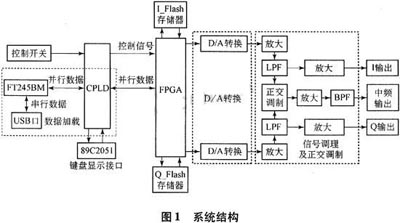

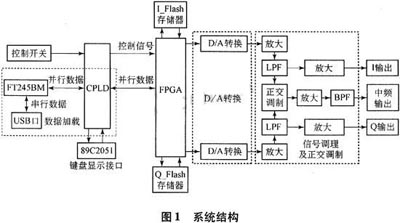

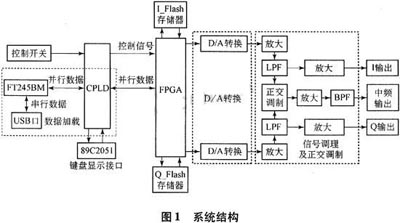

该模拟器系统结构如图1所示。

按照操作流程系统功能分为数据加载和波形输出两部分。波形数据加载通过计算机USB口进行,存储在大容量Flash存储器中。波形输出时首先输入初始高度、速度、加速度等参数,在同步脉冲的触发下,把数据从Flash存储器读出存入FPGA内部的Block SRAM中,在延时时刻到达后,在FPGA的控制下把数据输出至D/A转换器转换为模拟信号。同时,FPGA还要实现对系统时钟的管理,完成时钟的去歪斜、频率变换,确保时钟的相参性。电路设计中为实现对载漏和镜像的高抑制,正交调制器采用了专用的正交调制芯片,同时,电路布线采用I、Q两路完全对称结构,尽量保证两路的幅相平衡;专门设计了可调节环节,如幅度及直流偏置调整电位器,尽量将两路的幅度及直流偏置的差异调到最小。

2 关键技术分析

要使模拟器能模拟面目标散射回波的功能,必须有充足的存储空间存储回波数据。为检验雷达在不同场景下的性能,要求面目标模拟器能方便地修改波形数据。因此,具有较快写入速度的数据存储器的选择和高效可靠的数据加载的实现成为系统设计的一个关键因素。模拟器的信号输出时刻要有较高精度,以便不失真地再现目标场景。高精度输出延时计算成为系统设计的又一个关键技术。本模拟器的高精度延时计算没有采用DSP芯片,而是在FPGA内实现,简化了系统设计。

2.1 存储器选择

设计中存储的面目标回波数据分为I、Q两路存储。每路数据量为256 Mbit,总数据量为5l2 Mbit(64 MB)。波形输出时D/A转换器时钟为100 MHz,如果数据直接由Flash存储器输出至D/A转换器,则Flash存储器具有100 MB/s的输出速度时才能满足D/A转换器的数据更新速度。采用如此高速的大容量Flash存储器会使系统设计成本大大增加。

因此,设计时采用了数据预读入的方法来解决Flash存储器输出跟不上D/A转换器要求的问题。其基本思想是用FPGA内部的高速Block Select RAM作为缓冲器。设计中使用的FPGA内部的高速RAM读写速度均在2.31 ns以下,完全可以满足D/A转换器的要求。每路存储器对应2个Block RAM、2个RAM乒乓操作,一个RAM用于预存从Flash存储器读出的下一个触发周期的波形数据,另一个用于延时时刻到达后输出本触发周期的波形数据。图2中第1行表示雷达的触发脉冲(为正脉冲),下面2行的方框示意2个RAM。其工作过程为:第N-1触发周期内从Flash存储器读出数据写入A,延时时刻到达后B中的数据输出给D/A转换器;第N触发周期内从Flash存储器读出数据写入B,延时时刻到达后A中的数据输出给D/A转换器;依此循环往复进行。这样数据的转存和输出分隔开来,互不影响,只要Flash存储器的速度满足在一个触发周期内把一条回波数据输出完毕就可以确保回波依次输出。这就大大降低了对Flash存储器的要求,降低了设计成本。

基于以上思想,设计中选择两片Intel公司大容量Strata Flash存储器E28F256J3A-150作为数据存储器。该Flash芯片具有写缓冲(write buffer)模式和异步页读(Asynchronous Page Mode)模式,数据宽度可在8 bit和16 bit之间选择。当该芯片工作在异步页读模式时,其最快的单个数据平均读出时间为56.25 ns,在脉冲重频周期为100μs时,一个周期内可完成1 777个数据点的转存,满足系统设计要求。同时,它的写缓冲模式使得它具有较快的写入速度,每片高达256 Mbit的容量使得I、Q两路各用1片即可存储所有数据。

2.2 数据加载

数据加载通过计算机USB口,经过FT245BM将串行数据转换为并行数据后在FPGA控制下存储在Flash存储器中。为了保证数据加载的正确,系统还具有回读校验功能,加载结束立即把数据回读到PC存储,与加载源文件比较后给出正确与否及加载错误的数据个数等信息,由用户根据比较结果决定是重新进行加载还是退出加载过程。数据在系统中的传递过程示意如下:USB(串行数据)?FT245BM(8位并行数据)?FPGA(16位并行数据)?Flash存储器(16位并行数据)。

FT245BM 芯片是FTDI(Future Technology DevicesInternational Ltd)公司推出的进行USB和并行I/O口协议转换的专用芯片。FT245BM支持USB1.1及USB2.0规范,数据传输速度可达到1 MB/s。使用FT-DI提供的VCP(虚拟串口)驱动程序,用该芯片实现的外设在PC中即被当做一个标准的串行设备对待。用VC语言中提供的串口通信MSComm控件很容易可以完成控制程序编写。通过FT245BM既充分利用USB高速数据传输,又避免了在FPGA中开发USB协议接口的麻烦,缩短研发周期;同时使得模拟器与PC的接口简单。

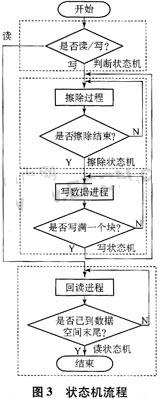

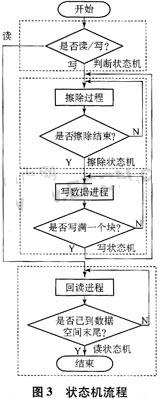

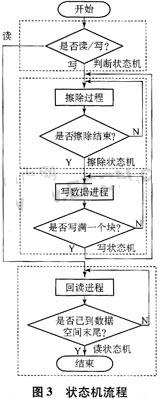

数据加载时Flash存储器工作于写缓冲模式。首先以块为单位进行擦除,每块擦除时间为1 s;擦除结束在写人数据之前要先向Flash存储器写入WriteBuffer命令,随后向存储器的缓冲区写人数据,一次写缓冲操作最多可连续写入16字(1字=16 bit)数据,每个字写入时间至少25 ns;而后再对Flash存储器写入Write Buffer Confirm命令启动Flash存储器内的WSM(Write State Machine),把前面写入的16字编程存入其内部存储空间,内部编程时间至少要218μs。这样复杂的一个异步过程,采用常规的组合或时序逻辑无法完成控制。因此,设计中由FPGA控制Flash存储器的片选和写使能信号,采用状态机来实现。为方便程序的后续维护,提高可靠性和可读性,根据Flash存储器的操作状态设计了4个状态机:判断状态机、擦除状态机、写数据状态机、回读状态机。4个状态机的关系如图3所示。

2.3 高精度延时计算的实现和数据输出

系统的延时计算和输出控制均在FPGA中实现。为提高计算精度,在设计中通过对数据进行合理缩放,既充分利用了FPGA内16 bit×16 bit的乘法器核的精度,又不会导致加法运算溢出。由于硬件中实现除法比较困难,我们把除法运算转换为乘法运算,以提高运算速度和精度。比如,在计算时有一个除以10 000的运算,采用下面的方法来实现。设y=x/10000,则

这样就把除法运算转化为2个截尾处理和1个乘法运算。为补偿截尾处理引起的数据缩小,经过实验比较后,设计中把53 687放大为53 705,可使在不同数据时的平均误差尽量小。式(1)在Verilog程序中只需要1个乘法器就可以完成。基于以上方法实现的延时计算最大绝对误差只有±3 ns。延时计算的最后结果以数据输出时钟的周期个数来表示。输出的波形数据需要预读入FPGA内的RAM中。在触发脉冲的前沿一到就开始从Flash存储器中读取一条回波的数据转存入FPGA内,Flash存储器工作在异步页读模式;同时,触发脉冲的前沿一到便开始对时钟计数,计数个数与延时计算结果相等时启动数据输出。数据从Flash存储器输出至RAM时是16位的,而D/A转换器分辨率只有8位,设计中充分利用了FPGA内双口Block Select RAM的两边数据宽度可不同的特点,避免设计用于不同宽度数据转换的专用程序。

信号在雷达系统中传输时,传输线和器件的迟滞作用导致信号到达处理机的时间比实际计算时刻有固定延迟,且在不同传输线长度时延时大小不同。系统具有键盘接口,可根据实测延时值预先补偿掉系统误差,保证回波信号到达信号处理机的时刻与实际时刻准确吻合。经实际检验,信号处理机识别的高度与理论高度误差在1 m,与6 ns 对应的0.9 m吻合。考虑到信号处理机本身的不精确性,延时预补偿非常准确有效。

3 实验结果

对本文设计的模拟器产生的理想线性调频信号,用示波器采集后进行脉冲压缩,采用Hamming加权后,脉冲压缩峰值旁瓣比大于35 dB,主瓣展宽与理论值相当,测试结果如图4所示。

本模拟器还可通过对信号进行预失真、补偿系统误差来提高性能。补偿后的信号脉压结果见图5,可以看到脉冲压缩峰值旁瓣比大于41 dB,接近理论值。

4 结束语

本文所提出的方案由单片FPGA完成对模拟器系统的控制并进行高精度延时计算,简化了设计,外围接口简单通用,充分发挥了可编程器件的优势。本文设计的模拟器以大容量Flash存储器作为波形数据的存储介质,利用FT245BM简化系统与计算机接口设计的同时,提高了系统数据加载的速度和可靠性。用户可方便快捷地完成数据更改,既可以加载理想数据对信号处理机进行功能验证,又可以加载用户实际实验数据模拟实际工作环境完成系统联调,降低实验成本。

在雷达系统研制过程中,回波信号模拟器是不可缺少的设备,它可以灵活地产生雷达在各种工作状态下的回波信号,有助于雷达的实验室调试,降低试验成本,增加灵活性,对其设计、改进、定型都有重要意义。

本文设计的面目标模拟器基于波形存储直读的DDWS(直接数字波形合成)法实现,模拟成像雷达接收其自身发射的单个射频线性调频脉冲,经复杂的地面目标反射后,形成的射频回波信号经下变频后输出。DSWS就是将预先存储的经理想采样的数字波形直接进行D/A转换而得到所需的模拟信号。该模拟器采用波形存储直读法产生基带I/Q信号,经正交调制产生中频,最大带宽80 MHz,可直接输出视频信号和中频信号。该面目标模拟器具有较大的数据存储空间和高精度的输出时刻控制。设计中对I、Q路基带数据进行存储,单路存储空间256 Mbit(32 MB),总存储空间64 MB,可以满足大多数需求;通过进行延时补偿使得输出信号输出时刻精确可控。

该模拟器采用USB接口加载回波数据,可通过计算机方便地修改波形数据。加载理想数据对信号处理机进行功能验证,又可以加载实验数据实现真实目标场景再现、进行设备出厂前的系统联调。系统核心控制单元采用Xilinx公司的VirtexⅡ系列XC2V500型FPGA(现场可编程门阵列),完成系统的功能控制、高精度延时计算、数据存储控制等关键任务。

1 系统结构描述

该模拟器系统结构如图1所示。

按照操作流程系统功能分为数据加载和波形输出两部分。波形数据加载通过计算机USB口进行,存储在大容量Flash存储器中。波形输出时首先输入初始高度、速度、加速度等参数,在同步脉冲的触发下,把数据从Flash存储器读出存入FPGA内部的Block SRAM中,在延时时刻到达后,在FPGA的控制下把数据输出至D/A转换器转换为模拟信号。同时,FPGA还要实现对系统时钟的管理,完成时钟的去歪斜、频率变换,确保时钟的相参性。电路设计中为实现对载漏和镜像的高抑制,正交调制器采用了专用的正交调制芯片,同时,电路布线采用I、Q两路完全对称结构,尽量保证两路的幅相平衡;专门设计了可调节环节,如幅度及直流偏置调整电位器,尽量将两路的幅度及直流偏置的差异调到最小。

2 关键技术分析

要使模拟器能模拟面目标散射回波的功能,必须有充足的存储空间存储回波数据。为检验雷达在不同场景下的性能,要求面目标模拟器能方便地修改波形数据。因此,具有较快写入速度的数据存储器的选择和高效可靠的数据加载的实现成为系统设计的一个关键因素。模拟器的信号输出时刻要有较高精度,以便不失真地再现目标场景。高精度输出延时计算成为系统设计的又一个关键技术。本模拟器的高精度延时计算没有采用DSP芯片,而是在FPGA内实现,简化了系统设计。

2.1 存储器选择

设计中存储的面目标回波数据分为I、Q两路存储。每路数据量为256 Mbit,总数据量为5l2 Mbit(64 MB)。波形输出时D/A转换器时钟为100 MHz,如果数据直接由Flash存储器输出至D/A转换器,则Flash存储器具有100 MB/s的输出速度时才能满足D/A转换器的数据更新速度。采用如此高速的大容量Flash存储器会使系统设计成本大大增加。

因此,设计时采用了数据预读入的方法来解决Flash存储器输出跟不上D/A转换器要求的问题。其基本思想是用FPGA内部的高速Block Select RAM作为缓冲器。设计中使用的FPGA内部的高速RAM读写速度均在2.31 ns以下,完全可以满足D/A转换器的要求。每路存储器对应2个Block RAM、2个RAM乒乓操作,一个RAM用于预存从Flash存储器读出的下一个触发周期的波形数据,另一个用于延时时刻到达后输出本触发周期的波形数据。图2中第1行表示雷达的触发脉冲(为正脉冲),下面2行的方框示意2个RAM。其工作过程为:第N-1触发周期内从Flash存储器读出数据写入A,延时时刻到达后B中的数据输出给D/A转换器;第N触发周期内从Flash存储器读出数据写入B,延时时刻到达后A中的数据输出给D/A转换器;依此循环往复进行。这样数据的转存和输出分隔开来,互不影响,只要Flash存储器的速度满足在一个触发周期内把一条回波数据输出完毕就可以确保回波依次输出。这就大大降低了对Flash存储器的要求,降低了设计成本。

基于以上思想,设计中选择两片Intel公司大容量Strata Flash存储器E28F256J3A-150作为数据存储器。该Flash芯片具有写缓冲(write buffer)模式和异步页读(Asynchronous Page Mode)模式,数据宽度可在8 bit和16 bit之间选择。当该芯片工作在异步页读模式时,其最快的单个数据平均读出时间为56.25 ns,在脉冲重频周期为100μs时,一个周期内可完成1 777个数据点的转存,满足系统设计要求。同时,它的写缓冲模式使得它具有较快的写入速度,每片高达256 Mbit的容量使得I、Q两路各用1片即可存储所有数据。

2.2 数据加载

数据加载通过计算机USB口,经过FT245BM将串行数据转换为并行数据后在FPGA控制下存储在Flash存储器中。为了保证数据加载的正确,系统还具有回读校验功能,加载结束立即把数据回读到PC存储,与加载源文件比较后给出正确与否及加载错误的数据个数等信息,由用户根据比较结果决定是重新进行加载还是退出加载过程。数据在系统中的传递过程示意如下:USB(串行数据)?FT245BM(8位并行数据)?FPGA(16位并行数据)?Flash存储器(16位并行数据)。

FT245BM 芯片是FTDI(Future Technology DevicesInternational Ltd)公司推出的进行USB和并行I/O口协议转换的专用芯片。FT245BM支持USB1.1及USB2.0规范,数据传输速度可达到1 MB/s。使用FT-DI提供的VCP(虚拟串口)驱动程序,用该芯片实现的外设在PC中即被当做一个标准的串行设备对待。用VC语言中提供的串口通信MSComm控件很容易可以完成控制程序编写。通过FT245BM既充分利用USB高速数据传输,又避免了在FPGA中开发USB协议接口的麻烦,缩短研发周期;同时使得模拟器与PC的接口简单。

数据加载时Flash存储器工作于写缓冲模式。首先以块为单位进行擦除,每块擦除时间为1 s;擦除结束在写人数据之前要先向Flash存储器写入WriteBuffer命令,随后向存储器的缓冲区写人数据,一次写缓冲操作最多可连续写入16字(1字=16 bit)数据,每个字写入时间至少25 ns;而后再对Flash存储器写入Write Buffer Confirm命令启动Flash存储器内的WSM(Write State Machine),把前面写入的16字编程存入其内部存储空间,内部编程时间至少要218μs。这样复杂的一个异步过程,采用常规的组合或时序逻辑无法完成控制。因此,设计中由FPGA控制Flash存储器的片选和写使能信号,采用状态机来实现。为方便程序的后续维护,提高可靠性和可读性,根据Flash存储器的操作状态设计了4个状态机:判断状态机、擦除状态机、写数据状态机、回读状态机。4个状态机的关系如图3所示。

2.3 高精度延时计算的实现和数据输出

系统的延时计算和输出控制均在FPGA中实现。为提高计算精度,在设计中通过对数据进行合理缩放,既充分利用了FPGA内16 bit×16 bit的乘法器核的精度,又不会导致加法运算溢出。由于硬件中实现除法比较困难,我们把除法运算转换为乘法运算,以提高运算速度和精度。比如,在计算时有一个除以10 000的运算,采用下面的方法来实现。设y=x/10000,则

这样就把除法运算转化为2个截尾处理和1个乘法运算。为补偿截尾处理引起的数据缩小,经过实验比较后,设计中把53 687放大为53 705,可使在不同数据时的平均误差尽量小。式(1)在Verilog程序中只需要1个乘法器就可以完成。基于以上方法实现的延时计算最大绝对误差只有±3 ns。延时计算的最后结果以数据输出时钟的周期个数来表示。输出的波形数据需要预读入FPGA内的RAM中。在触发脉冲的前沿一到就开始从Flash存储器中读取一条回波的数据转存入FPGA内,Flash存储器工作在异步页读模式;同时,触发脉冲的前沿一到便开始对时钟计数,计数个数与延时计算结果相等时启动数据输出。数据从Flash存储器输出至RAM时是16位的,而D/A转换器分辨率只有8位,设计中充分利用了FPGA内双口Block Select RAM的两边数据宽度可不同的特点,避免设计用于不同宽度数据转换的专用程序。

信号在雷达系统中传输时,传输线和器件的迟滞作用导致信号到达处理机的时间比实际计算时刻有固定延迟,且在不同传输线长度时延时大小不同。系统具有键盘接口,可根据实测延时值预先补偿掉系统误差,保证回波信号到达信号处理机的时刻与实际时刻准确吻合。经实际检验,信号处理机识别的高度与理论高度误差在1 m,与6 ns 对应的0.9 m吻合。考虑到信号处理机本身的不精确性,延时预补偿非常准确有效。

3 实验结果

对本文设计的模拟器产生的理想线性调频信号,用示波器采集后进行脉冲压缩,采用Hamming加权后,脉冲压缩峰值旁瓣比大于35 dB,主瓣展宽与理论值相当,测试结果如图4所示。

本模拟器还可通过对信号进行预失真、补偿系统误差来提高性能。补偿后的信号脉压结果见图5,可以看到脉冲压缩峰值旁瓣比大于41 dB,接近理论值。

4 结束语

本文所提出的方案由单片FPGA完成对模拟器系统的控制并进行高精度延时计算,简化了设计,外围接口简单通用,充分发挥了可编程器件的优势。本文设计的模拟器以大容量Flash存储器作为波形数据的存储介质,利用FT245BM简化系统与计算机接口设计的同时,提高了系统数据加载的速度和可靠性。用户可方便快捷地完成数据更改,既可以加载理想数据对信号处理机进行功能验证,又可以加载用户实际实验数据模拟实际工作环境完成系统联调,降低实验成本。

举报

举报

举报

举报