在DC-DC电源管理芯片中,电压的稳定尤为重要,因此需要在芯片内部集成欠压锁定电路来提高电源的可靠性和安全性。对于其它的集成电路,为提高电路的可靠性和稳定性,欠压锁定电路同样十分重要。

传统的欠压锁定电路要求简单、实用,但忽略了欠压锁定电路的功耗,使系统在正常工作时,仍然有较大的静态功耗,这样就降低了电源的效率,并且无效的功耗增加了芯片散热系统的负担,影响系统的稳定性。

基于传统的欠压锁定电路,本文提出一种CMOS工艺下的低压低静态功耗欠压锁定电路,并通过HSPICE仿真。此电路可以在1.5V~6V的电源电压范围下工作,阈值可调,翻转速度很快。电源电压正常工作时,此电路的静态功耗可低于2μW。此电路结构简单,用标准CMOS工艺实现容易,可用于由电池供电的电源管理芯片或便携设备中作欠压保护电路。

1 欠压锁定电路工作原理

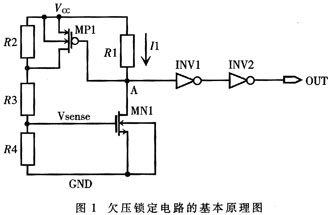

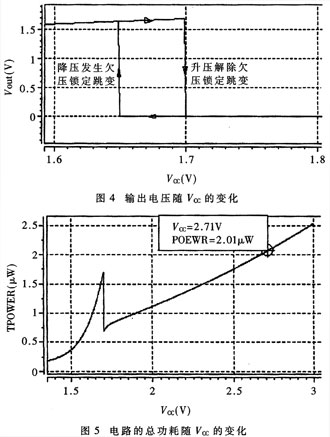

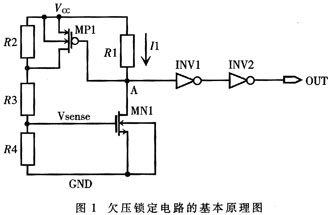

欠压锁定电路的基本原理图如图1所示。电路包括电压采样电路、比较器、输出缓冲器和反馈回路。Vcc为待检测的电源电压,电阻R2、R3、R4组成Vcc的分压采样电路,实现对Vcc的采样;NMOS开关管MNl和电阻R1构成比较器,对采样电压和MNl的VTH进行比较,并输出比较结果;反向器INV1和INV2组成缓冲器电路,可对比较器的输出波形进行整形和缓冲,提高电路的负载能力;PMOS开关管MP1构成正反馈回路,可以实现电路的迟滞功能,防止电路在Vcc的阈值附近振荡,增加系统的稳定性。调整R2、R3、R4的大小可实现不同阈值和迟滞量的Vcc欠压保护。

欠压锁定电路结构简单,工作电压范围宽,适应性强,且无需额外的基准电压[2],因此有着广泛的应用。电路正常工作时,MN1导通,流过R1的电流I1作为比较器的灌电流,全部流经MN1到地。为使电路性能可靠,有较好的响应速度,电流I1通常需5μA~10μA。静态时该电流为无效用电流,增加了系统的功耗,浪费了电源的能量,对系统的效率、散热及稳定性产生了不好的影响,并且其响应速度也不够快。如果用增大R1的阻值减小电流I1的大小,虽然可以降低功耗,但减慢了电路的响应速度,并严重影响了电路的稳定性,因此需要对该电路作进一步的改进。

2 改进的电路

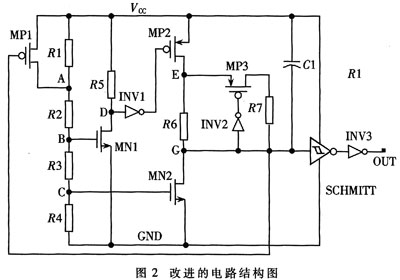

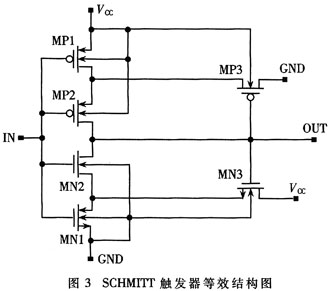

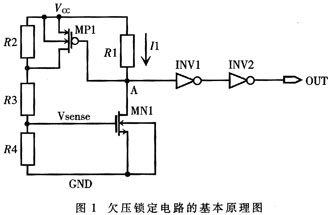

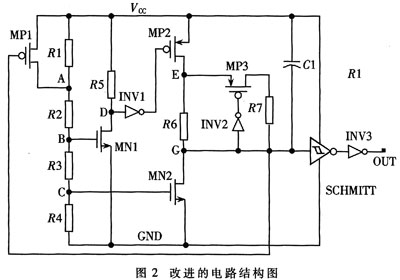

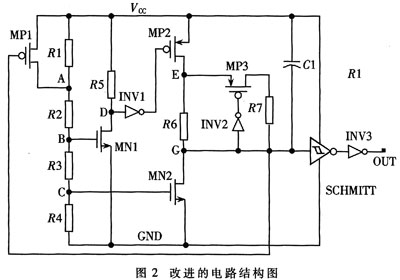

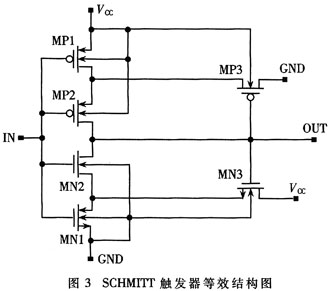

改进的电路如图2所示,电路结构由采样、先导控制、比较器、迟滞反馈回路、加速响应电路、缓冲器六部分构成。电阻R1、R2、R3、R4构成分压电阻网络实现对Vcc的采样;MNl、R5、INVl组成先导控制电路,实现对比较器灌电流的控制;MN2、R6、MP2组成比较器,实现采样电压与MN2的VTH比较;MP1构成正反馈回路,可实现Vcc的迟滞功能;INV2、MP3、R7构成正反馈回路,可加速比较器的翻转,从而提高电路的响应速度;SCHMITT触发器和INV3是缓冲电路,对比较器的输出波形进行缓冲和整形,SCHMITT触发器的结构如图3所示,其工作原理详见参考文献[3];另外,电容C1起滤波和储能作用。

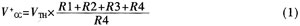

本电路通过低功耗的先导控制电路控制电流较大的比较器的灌电流,使比较器只有在状态发生翻转时有微弱的电流流过MN2。在其余时间,无论比较器是输出高电平还是低电平,都没有电流流过MN2,也就是说使电路无论是在正常工作状态还是在欠压锁定状态,比较器都不消耗功率,这样就可以把电路的静态功耗降到最低。为了加快比较器的翻转速度,可通过先导控制电路和加速响应电路来实现。在Vcc电压升高过程中,当电压较低时,由于MNl、MN2截止,D电位处于高电位,可通过先导控制电路使MP2导通,同时MP3也导通,给电容C1充电,使G点的电压等于Vcc,使输出端为高电平,电路处于欠压锁定状态;随着Vcc电压升高,由于B点的电压高于C点的电压,使MNl比MN2先导通,先导控制电路使MP2截止,使比较器的灌电流消失,此时由于电容C1没有放电回路,使G点保持高电平,电路仍处于欠压锁定状态;当Vcc进一步上升使C点的电压高于MN2的阈值时,MN2导通,由于没有灌电流的作用,MN2迅速给C1放电,使G点电压迅速下降到0V,电路解除欠压锁定,进入正常工作状态,此时MP1导通,R1被短接。此后Vcc继续升高,先导控制电路使MP2保持截止状态,使电路保持在正常工作状态。由于比较器中没有灌电流,比较器的静态功耗为零。因此Vcc电压在上升过程中,其阈值为:

在Vcc电压下降使电路由正常工作状态转为欠压锁定状态的过程中,由于MN2截止之后的很短时间内,MNl仍然导通,使MP2仍处于截止状态,电容C1无放电回路,G点仍处于低电平,电路仍处于正常工作状态,此时,比较器的静态功耗也为零;此后MN1截止,使MP1导通,MN2仍处于截止,由于灌电流的作用,使G点电压高,通过INV2、MP3、R7的正反馈作用,使MP3导通,由于R7阻值较小,使流过MP3、R7的电流较大,G点电压迅速提升到Vcc,电路进入欠压锁定状态;此后,MN2截止,使电路保持欠压锁定状态,由于比较器中没有电流流过MN2,因此比较器基本上无静态功耗。因此Vcc电压在下降过程中,其阈值为:

如图2所示,改变电阻R3的大小,可以调整MN1和MN2导通和截止的时间次序。为了降低R5、MN1的功耗,应增大R5的阻值,减小MN1的W/L,使流过MN1和R5的电流很小。为了减小MN1和MN2制造工艺的不匹配问题,要求MN2由若干个与NN1相同的NMOS管并联构成。

3 HSPICE仿真结果与分析

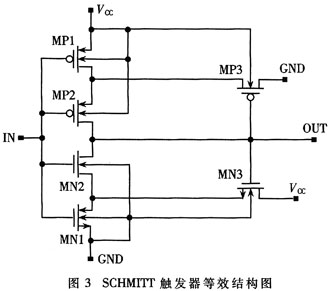

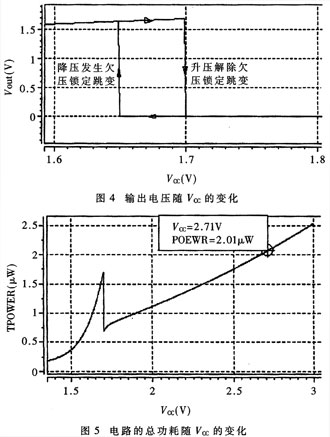

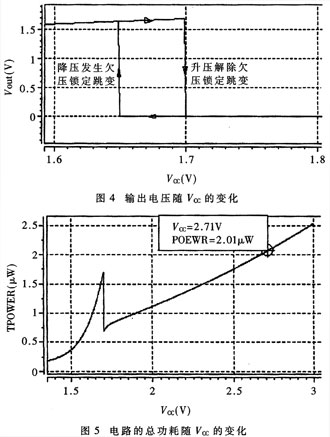

根据上面的计算结果,采用0.6μm工艺模型,利用Hspice对电路进行模拟仿真。在模拟仿真过程中,各器件的参数有调整。在仿真时,分别增大和减小电源电压进行DC扫描,输出端的波形如图4所示,电路的总功耗如图5所示。

从图4的仿真的波形中可以看出:当增大电源电压时,电压低于1.7V为欠压锁定;当减小电源电压时,电压低于1.65V为欠压锁定。仍可进一步调整参数,以改变电源电压欠压阈值。

从图5的仿真波形中可以看出:当Vcc的电压正常时,电路的总功耗随着Vcc的升高而增大,当Vcc=2.7V时,总功耗约为2μW,可见电路的静态功耗很低。

本电路采用标准CMOS工艺,通过先导控制技术和加速响应回路成功地实现了欠压锁定电路的快速响应和低静态功耗的功能,解决了电路在低功耗和快速响应之间的矛盾,可适应1.5V~6V的电源电压工作范围,且阈值电压可调,在低电压低功耗IC集成电路芯片中,有较大的应用价值。

在DC-DC电源管理芯片中,电压的稳定尤为重要,因此需要在芯片内部集成欠压锁定电路来提高电源的可靠性和安全性。对于其它的集成电路,为提高电路的可靠性和稳定性,欠压锁定电路同样十分重要。

传统的欠压锁定电路要求简单、实用,但忽略了欠压锁定电路的功耗,使系统在正常工作时,仍然有较大的静态功耗,这样就降低了电源的效率,并且无效的功耗增加了芯片散热系统的负担,影响系统的稳定性。

基于传统的欠压锁定电路,本文提出一种CMOS工艺下的低压低静态功耗欠压锁定电路,并通过HSPICE仿真。此电路可以在1.5V~6V的电源电压范围下工作,阈值可调,翻转速度很快。电源电压正常工作时,此电路的静态功耗可低于2μW。此电路结构简单,用标准CMOS工艺实现容易,可用于由电池供电的电源管理芯片或便携设备中作欠压保护电路。

1 欠压锁定电路工作原理

欠压锁定电路的基本原理图如图1所示。电路包括电压采样电路、比较器、输出缓冲器和反馈回路。Vcc为待检测的电源电压,电阻R2、R3、R4组成Vcc的分压采样电路,实现对Vcc的采样;NMOS开关管MNl和电阻R1构成比较器,对采样电压和MNl的VTH进行比较,并输出比较结果;反向器INV1和INV2组成缓冲器电路,可对比较器的输出波形进行整形和缓冲,提高电路的负载能力;PMOS开关管MP1构成正反馈回路,可以实现电路的迟滞功能,防止电路在Vcc的阈值附近振荡,增加系统的稳定性。调整R2、R3、R4的大小可实现不同阈值和迟滞量的Vcc欠压保护。

欠压锁定电路结构简单,工作电压范围宽,适应性强,且无需额外的基准电压[2],因此有着广泛的应用。电路正常工作时,MN1导通,流过R1的电流I1作为比较器的灌电流,全部流经MN1到地。为使电路性能可靠,有较好的响应速度,电流I1通常需5μA~10μA。静态时该电流为无效用电流,增加了系统的功耗,浪费了电源的能量,对系统的效率、散热及稳定性产生了不好的影响,并且其响应速度也不够快。如果用增大R1的阻值减小电流I1的大小,虽然可以降低功耗,但减慢了电路的响应速度,并严重影响了电路的稳定性,因此需要对该电路作进一步的改进。

2 改进的电路

改进的电路如图2所示,电路结构由采样、先导控制、比较器、迟滞反馈回路、加速响应电路、缓冲器六部分构成。电阻R1、R2、R3、R4构成分压电阻网络实现对Vcc的采样;MNl、R5、INVl组成先导控制电路,实现对比较器灌电流的控制;MN2、R6、MP2组成比较器,实现采样电压与MN2的VTH比较;MP1构成正反馈回路,可实现Vcc的迟滞功能;INV2、MP3、R7构成正反馈回路,可加速比较器的翻转,从而提高电路的响应速度;SCHMITT触发器和INV3是缓冲电路,对比较器的输出波形进行缓冲和整形,SCHMITT触发器的结构如图3所示,其工作原理详见参考文献[3];另外,电容C1起滤波和储能作用。

本电路通过低功耗的先导控制电路控制电流较大的比较器的灌电流,使比较器只有在状态发生翻转时有微弱的电流流过MN2。在其余时间,无论比较器是输出高电平还是低电平,都没有电流流过MN2,也就是说使电路无论是在正常工作状态还是在欠压锁定状态,比较器都不消耗功率,这样就可以把电路的静态功耗降到最低。为了加快比较器的翻转速度,可通过先导控制电路和加速响应电路来实现。在Vcc电压升高过程中,当电压较低时,由于MNl、MN2截止,D电位处于高电位,可通过先导控制电路使MP2导通,同时MP3也导通,给电容C1充电,使G点的电压等于Vcc,使输出端为高电平,电路处于欠压锁定状态;随着Vcc电压升高,由于B点的电压高于C点的电压,使MNl比MN2先导通,先导控制电路使MP2截止,使比较器的灌电流消失,此时由于电容C1没有放电回路,使G点保持高电平,电路仍处于欠压锁定状态;当Vcc进一步上升使C点的电压高于MN2的阈值时,MN2导通,由于没有灌电流的作用,MN2迅速给C1放电,使G点电压迅速下降到0V,电路解除欠压锁定,进入正常工作状态,此时MP1导通,R1被短接。此后Vcc继续升高,先导控制电路使MP2保持截止状态,使电路保持在正常工作状态。由于比较器中没有灌电流,比较器的静态功耗为零。因此Vcc电压在上升过程中,其阈值为:

在Vcc电压下降使电路由正常工作状态转为欠压锁定状态的过程中,由于MN2截止之后的很短时间内,MNl仍然导通,使MP2仍处于截止状态,电容C1无放电回路,G点仍处于低电平,电路仍处于正常工作状态,此时,比较器的静态功耗也为零;此后MN1截止,使MP1导通,MN2仍处于截止,由于灌电流的作用,使G点电压高,通过INV2、MP3、R7的正反馈作用,使MP3导通,由于R7阻值较小,使流过MP3、R7的电流较大,G点电压迅速提升到Vcc,电路进入欠压锁定状态;此后,MN2截止,使电路保持欠压锁定状态,由于比较器中没有电流流过MN2,因此比较器基本上无静态功耗。因此Vcc电压在下降过程中,其阈值为:

如图2所示,改变电阻R3的大小,可以调整MN1和MN2导通和截止的时间次序。为了降低R5、MN1的功耗,应增大R5的阻值,减小MN1的W/L,使流过MN1和R5的电流很小。为了减小MN1和MN2制造工艺的不匹配问题,要求MN2由若干个与NN1相同的NMOS管并联构成。

3 HSPICE仿真结果与分析

根据上面的计算结果,采用0.6μm工艺模型,利用Hspice对电路进行模拟仿真。在模拟仿真过程中,各器件的参数有调整。在仿真时,分别增大和减小电源电压进行DC扫描,输出端的波形如图4所示,电路的总功耗如图5所示。

从图4的仿真的波形中可以看出:当增大电源电压时,电压低于1.7V为欠压锁定;当减小电源电压时,电压低于1.65V为欠压锁定。仍可进一步调整参数,以改变电源电压欠压阈值。

从图5的仿真波形中可以看出:当Vcc的电压正常时,电路的总功耗随着Vcc的升高而增大,当Vcc=2.7V时,总功耗约为2μW,可见电路的静态功耗很低。

本电路采用标准CMOS工艺,通过先导控制技术和加速响应回路成功地实现了欠压锁定电路的快速响应和低静态功耗的功能,解决了电路在低功耗和快速响应之间的矛盾,可适应1.5V~6V的电源电压工作范围,且阈值电压可调,在低电压低功耗IC集成电路芯片中,有较大的应用价值。

举报

举报

举报

举报