10多年来,模数转换器(ADC)作为产业发展助力剂已在工业过程控制、医疗仪器、通信系统和雷达等产品中得到广泛应用。其参数性能的不断提高使得这些‘蓝领’器件能紧跟上最新技术要求。

2007年2月份在旧金山举办的国际固态电路会议(ISSCC)展示了ADC的丰收成果。有关Nyquist Track的大量论文重新定义了这方面的技术发展水平,其中有两个已进入新的领域。另外也不要忘记来自一般怀疑者的最新论点。

1 ICY ADC

来自IMEC和KU Leuven的论文“A Cryogenic ADC Operating Down to 4.2K”介绍了一种连续逼近寄存器(SAR)ADC。该ADC可用于温度低至4.2K的应用场合,在这种温度下晶体管的工作状态有别于我们大多数人常见的状态。该芯片是用传统0.7mm CMOS技术实现的8位SAR。它的采样率为3kHz,工作电压为5V,在300pF负载电容下消耗350mW功率。

“用于X射线和远红外成像的低温检测器以及用于空间探索和粒子实验的光谱学都要求附近电子器件也要冷却到超低温度。”该论文指出,“低温ADC可提高冷热电子器件之间的信号完整性。”

低温工作时会产生一种被称为“载流冻结”的现象。低于77K温度下的CMOS性能要好于正常温度,这时的问题包括I-V传输特性中的磁滞异常,包括反向跨导区(图1)。

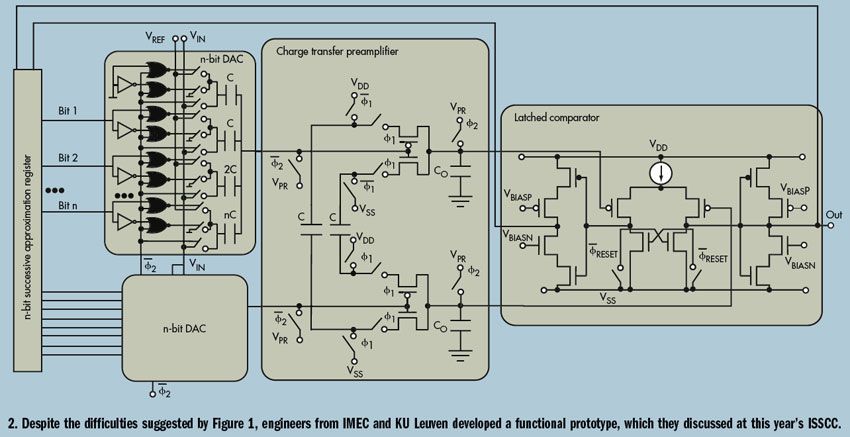

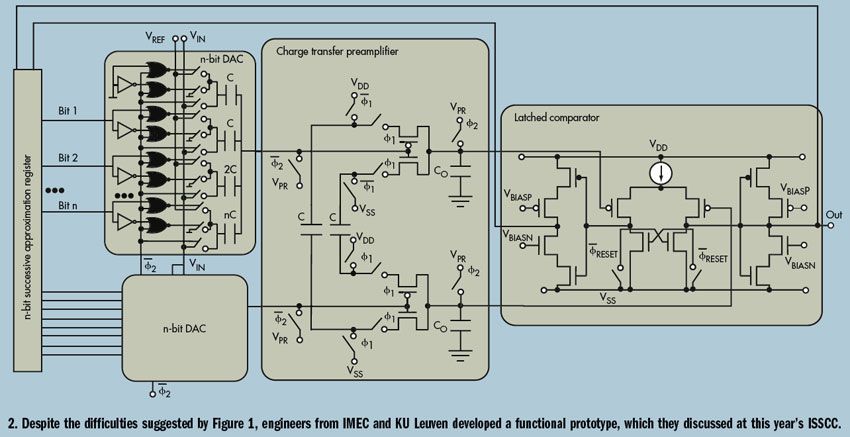

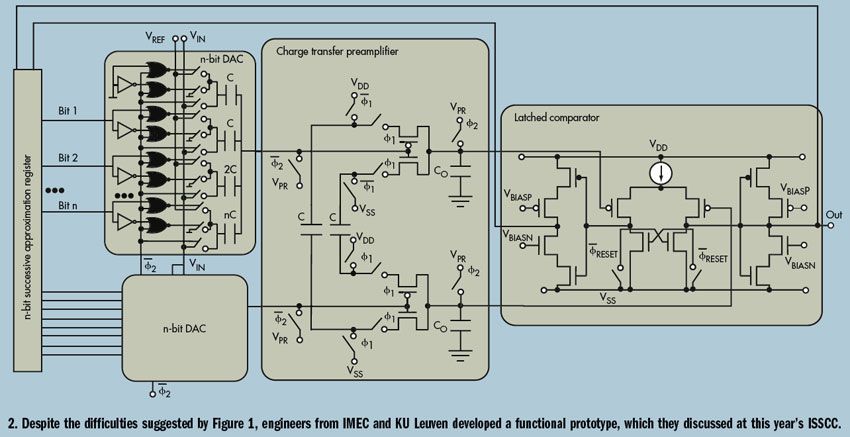

作者采用类似经验主义的设计方法创建了在正常环境温度和4.2K之间能正常工作的CMOS ADC。他们使用从低温晶体管测试中抽取的参数并用Spice仿真ADC的低温特性。他们的芯片由“一个电容性DAC(数模转换器)、一个电荷转移预放(CTA)、一个闭锁比较器和一个外部设置表SAR”组成(图2)。

据作者介绍,“当把ADC从正常环境温度冷却到4.2K时,没有观察到由于低温引起的不稳定性或磁滞现象,而INL(积分非线性误差)从0.5增加到了20.8 LSB(最低有效位),DNL(差分非线性误差)从0.4增加到了1.1 LSB。”

在“A 50GS/s Distributed T/H Amplifier in 0.18 mm SiGe BiCMOS”一文中,来自阿尔卡特-朗讯的作者介绍了一种基于分布式拓扑结构、50G样点/秒的分布式跟踪-保持型放大器(DTHA)。面临高比特率光纤收发器和毫米波无线设备中越来越高的采样速率压力,他们采用分布式微带线开发了三级DTHA来增加带宽。该放大器的无寄生动态范围(SFDR)要好于40dB。

“DTHA有一个集总输入缓冲器,该缓冲器由一个发射极退化差分放大器及随后的一对发射极跟随器组成。输入端有一个50V片上电阻提供良好的输入匹配。输入缓冲器提供一致的增益和非常低的输出阻抗,可驱动分布式开关型发射极跟随器和输出缓冲器(SEFOB)电路。”论文指出。

“为了避免输入缓冲器输出和分布式SEFOB输入线的端点之间产生多次反射,差分放大器带有50V的负载电阻,它近似匹配分布式SEFOB级电路的对等阻抗。所有构建模块都采用有源电流源来增强低频时的CMRR(共模抑制比),并提供更灵活的电流调制方法。”论文中写道。

“分布式SEFOB电路由三个相同的SEF和通过平衡微带传输线连接的输出缓冲器组成。”论文还写道,“时钟分配是解决采样抖动的最重要因素。。。[A]采用共发共基放大器架构来降低输出的电容负载,并减少由于Miller电容引起的带宽损失。。。分布式输出电路产生顺序性‘跟踪’和‘保持’控制信号并提供给SEFOB单元。”

2 Delta-Sigma的绝技

在ISSCC的delta-sigma报告会期间,ADC设计师透露了在动态范围和功耗方面取得的进步。例如,恩智浦公司提交的“A 56mW CT Quadrature Cascaded SD Modulator with 77dB DR (dynamic range) in a Near Zero-IF 20MHz Band”一文就介绍了一种带连续(CT)正交环路过滤器的级联delta-sigma调制器(图3)。

“第一级电路包含了正交环路滤波器QLF1、模数转换器ADC1i和ADC1q、反馈数模转换器DAC1i和DAC1q。第一级的量化误差Qi+jQq通过将数字输出Y1i和Y1q分别馈给数模转换器DAC2i和DAC2q得到,同时要从ADC1i和ADC1q的输入中减去它们的输出。”该论文写道。

“这一量化误差信号Qi+jQq再馈给由环路滤波器QLF2、模数转换器ADC2i和ADC2q以及数模转换器DAC3i和DAC3q组成的第二级级联电路。两级电路的数字输出都包含了量化误差Qi+jQq,但转移函数不同。因此,第二级输出要馈给一个数字正交噪声取消滤波器(QNCF)以便匹配这两个转移函数。”

“从第一级数字输出的延迟值中减去QNCF输出就可抵消Qi+jQq。结果信号Yi+jYq在有用频段内的量化噪声就非常小。最后,正交抽取滤波器(QDF)还会滤除带外的量化噪声。”论文总结道。

再看看其它架构。“A 10b 160MS/s 84mW 1V Subranging ADC in 90nm CMOS”一文的观点是,子区型(subranging)ADC非常适合混合信号ASIC。加利福尼亚大学洛杉矶分校(UCLA)的Huber等人编写的这篇论文介绍了一款带完整THA的10位、160兆样点/秒的子区型ADC(5位粗ADC、6位精确ADC,带相关的预放和比较器)。

原型功耗在1V时为84mW,在整个奈奎斯特频段上该器件可以获得好于9.1的等效数字或位(ENOB)和75dB的无寄生动态范围(SFDR),到200MHz时仍有8.5的ENOB和7dB的SFDR。在设计中粗ADC和精确ADC的取样开关用相位相反的时钟驱动,因此精确ADC延时增加了1/2个时钟周期,从而使粗ADC有足够的时间执行它自己的量化。

来自UCLA的另外一个小组与***的Realtek合作提交了“An 11b 800MS/s Time-Interleaved ADC with Digital Background Calibration”论文。这篇文章详细介绍了一款针对双绞线上提供10GBastT(IEEE 802.3an)应用而设计的时间交叉采样ADC。这种ADC必须有800兆样点/秒的处理速度,带宽有400MHz,ENOB大于9位。

采用90nm CMOS工艺完成的上述设计使用了4个取样速率为200MHz的交织管线式子ADC、数字校正逻辑、参考电压缓冲器和一个时钟发生器。它在子ADC对之间还采用了运放共享技术。每个子ADC由12个1.5位/级乘法DAC组成,可生成12位输出,有两个额外的位用于校正。

该器件的原型功耗约12mW。在采样率为800MHz时,DNL和INL分别小于0.5和1.6LSB。校正后的信噪加失真率(SINAD)在15MHz和400MHz输入时分别为58dB和54dB。

3 最新的通信芯片

凌力尔特公司的LTC2285是用于数字化高频、宽动态范围信号的双路、14位、125MS/s、低功耗的3V ADC。这款ADC主要设计用于WiMAX基站,它的高数据速率将达到目前标准62MS/s转换器的两倍。

LTC2285的交流性能参数包含奈奎斯特频点处的72.2dB SNR和82dB SFDR。典型的直流参数包括61.5 LSB INL和60.6 LSB DNL。转换噪声是1.3 LSB(rms)。该芯片的工作电压是3V,但独立的输出电压允许输出驱动0.5到3.6V的逻辑电路。目前该芯片已有样品供应,批量生产将在9月份开始。起价为73.5美元。

用于类似应用的AD9640是模拟器件公司(ADI)推出的双路、14位、采样速度超过135MS/s的ADC。该器件在中频为70MHz时的SNR是72.7dBFS,SFDR是85dBc。中频最高可达450MHz。为了简化时钟和减少抖动,AD9640内置有自己的时钟分频器,因此可以在基站DAC使用的同一时钟下工作。

为了简化自动增益控制(AGC),芯片专门包含了两块电路。一块电路用于监视输入的复合信号功率,并产生缓慢响应的增益加/减信号。另一块电路工作于快速检测(FD)模式,可以在最少两个时钟周期内检测出输入的超范围状态,并立即降低增益以避免过度驱动模拟前端。

AD9640具有12和14位分辨率,采样速率有80、105、125和150MS/s四种。14位版本的成本在37.5到87.5美元之间。

2006年年底时,TI公司发布了一款12位、500MS/s的管线型ADC产品,型号为ADS5463。在全速转换条件下其SNR可达64.5 dBFS,输入频率可达500MHz。ADS5463可提供84dBc的SFDR,10.5的ENOB,功耗为2.25W,起价为125美元。

2007年1月份,TI还推出了ADS5547和ADS5527。这两个分别为14位和12位、210MS/s的ADC现在是引脚兼容、高速ADS55xx系列中性能最好的产品。在70MHz的输入频率下,它们能提供高达73.3dBFS的SNR和85dBc的SFDR。

这两款ADC有一个特殊功能,即在低压差分信号(LVDS)和CMOS输出模式下,输出时钟可以在默认位置左右移动。这可以通过一个封装引脚或通过串口实现。移动时钟可实现建立和保持时间之间的调节。还可以调整输出时钟边沿与数据转换的关系。ADS5547的起价是82.5美元。

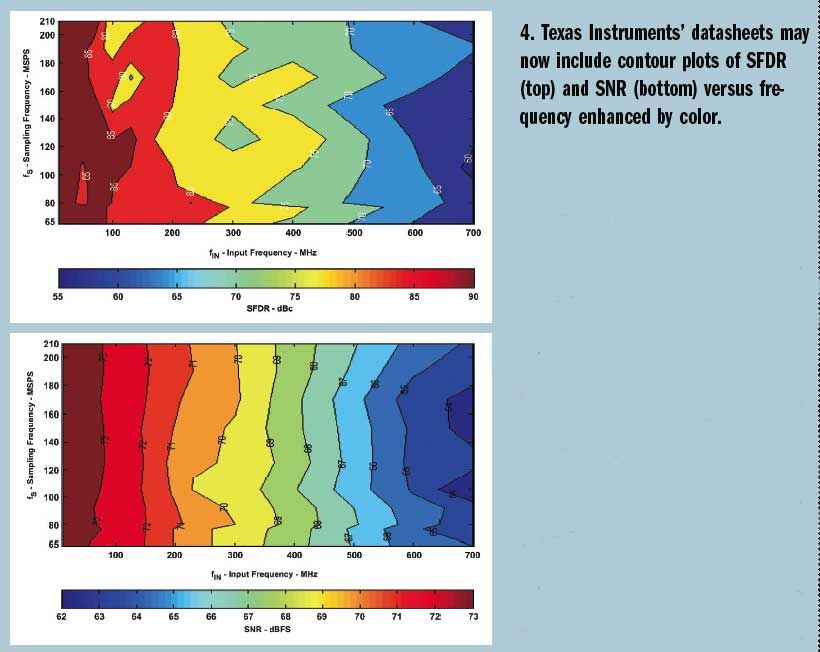

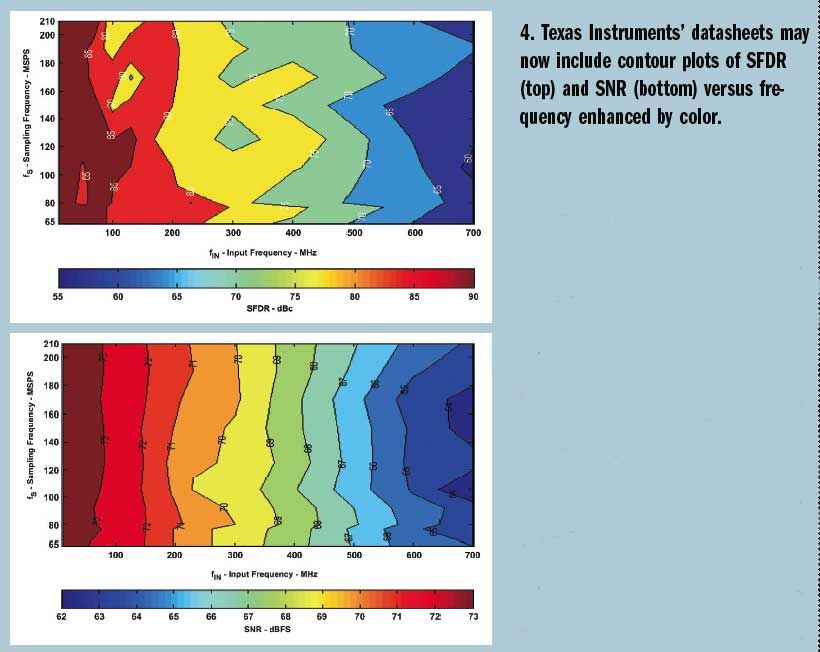

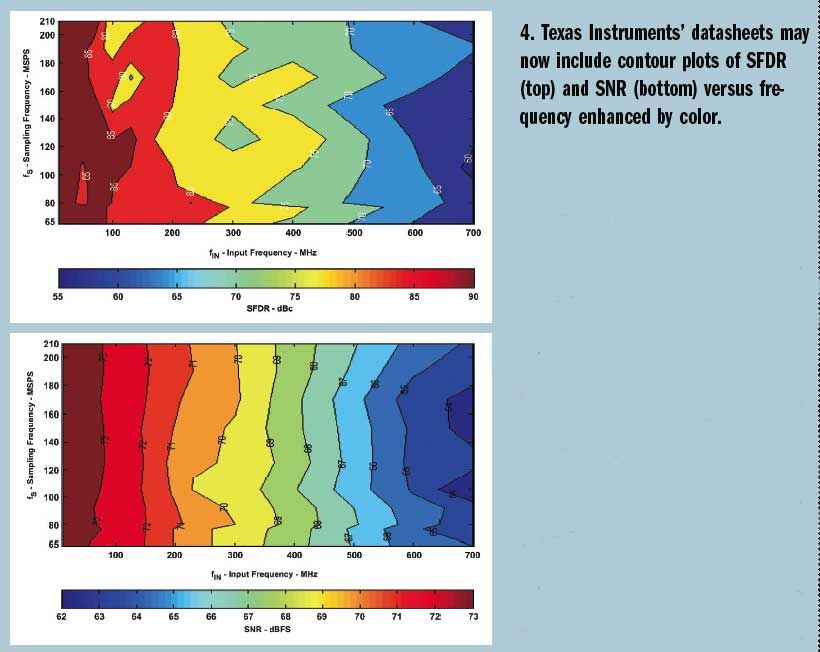

有关ADS5547的最引人注目的事之一是在产品手册中使用颜色显示性能曲线(图4)。在曲线图中的备注说明指出:“所有图的条件都是25C,AVDD=DRVDD=3.3V,采样频率=210MSPS,正弦波输入时钟,1.5 VPP差分/时钟幅度,50%的时钟占空比,21 dBFS差分模拟输入,内部参考模式,0dB增益,DDR LVDS数据输出(除非另外说明)。”

国家半导体公司(NS)也发布了有16位器件成员的管线ADC系列产品,其中性能最好的是带串行LVDS输出的14位、双路105MS/s芯片。典型的性能参数包括240MHz输入时72dB的SNR和83dB的SFDR。该系列产品由单路和双路、12位和14位、采样速率从65到105MS/s的转换器组成。最顶级的ADC14DS105起价为82.35美元。

在高端采样率方面,NS推出了8位、超高速ADC系列产品。这些产品基于其现有的折叠/内插式架构,可提供6GS/s的数据捕获速率,功耗为3.6W。它们采用一对3GS/s ADC0-83000 ADC交织的技术,无需额外的时钟调整电路。ADC08300的满功率输入带宽为3GHz。

NS公司还采用相同的架构开发了ADC0B83000器件。该器件整合了上述“不带B”版本器件的3GS/s采样率和一个可编程的4kB缓存,主要用于雷达和光信号检测以及距离修正(激光雷达)等应用场合。在这些应用场合,数据都是突发式捕获,并以较低的数据速率传送。

不带缓存的基本ADC083000具有3GHz的全功率带宽。因此它即使在第二奈奎斯特频段中也能采样宽带信号。通过调整片上的采样时钟相位,设计师无需外部时钟调整电路就可以在板上交织多个ADC。ADC083000可针对简单的数据捕获提供标准的1:4复分接输出,或针对精减的引脚数量提供新的1:2输出模式。它还能在输出端提供测试图案用于系统设计和测试。

当以3GS/s采样750MHz输入信号时,ADC083000通常能达到7.0的ENOB、44dB的SNR和54dB的SFDR。带缓存的ADC08B3000在采样后可将数据存储在4kB的FIFO中。一条或两条8位CMOS输出总线再以较低的速率将FIFO中的数据传送到ADC外部的处理器。最高速度是400MB/s。ADC083000在1000片批量时的价格为523美元。

10多年来,模数转换器(ADC)作为产业发展助力剂已在工业过程控制、医疗仪器、通信系统和雷达等产品中得到广泛应用。其参数性能的不断提高使得这些‘蓝领’器件能紧跟上最新技术要求。

2007年2月份在旧金山举办的国际固态电路会议(ISSCC)展示了ADC的丰收成果。有关Nyquist Track的大量论文重新定义了这方面的技术发展水平,其中有两个已进入新的领域。另外也不要忘记来自一般怀疑者的最新论点。

1 ICY ADC

来自IMEC和KU Leuven的论文“A Cryogenic ADC Operating Down to 4.2K”介绍了一种连续逼近寄存器(SAR)ADC。该ADC可用于温度低至4.2K的应用场合,在这种温度下晶体管的工作状态有别于我们大多数人常见的状态。该芯片是用传统0.7mm CMOS技术实现的8位SAR。它的采样率为3kHz,工作电压为5V,在300pF负载电容下消耗350mW功率。

“用于X射线和远红外成像的低温检测器以及用于空间探索和粒子实验的光谱学都要求附近电子器件也要冷却到超低温度。”该论文指出,“低温ADC可提高冷热电子器件之间的信号完整性。”

低温工作时会产生一种被称为“载流冻结”的现象。低于77K温度下的CMOS性能要好于正常温度,这时的问题包括I-V传输特性中的磁滞异常,包括反向跨导区(图1)。

作者采用类似经验主义的设计方法创建了在正常环境温度和4.2K之间能正常工作的CMOS ADC。他们使用从低温晶体管测试中抽取的参数并用Spice仿真ADC的低温特性。他们的芯片由“一个电容性DAC(数模转换器)、一个电荷转移预放(CTA)、一个闭锁比较器和一个外部设置表SAR”组成(图2)。

据作者介绍,“当把ADC从正常环境温度冷却到4.2K时,没有观察到由于低温引起的不稳定性或磁滞现象,而INL(积分非线性误差)从0.5增加到了20.8 LSB(最低有效位),DNL(差分非线性误差)从0.4增加到了1.1 LSB。”

在“A 50GS/s Distributed T/H Amplifier in 0.18 mm SiGe BiCMOS”一文中,来自阿尔卡特-朗讯的作者介绍了一种基于分布式拓扑结构、50G样点/秒的分布式跟踪-保持型放大器(DTHA)。面临高比特率光纤收发器和毫米波无线设备中越来越高的采样速率压力,他们采用分布式微带线开发了三级DTHA来增加带宽。该放大器的无寄生动态范围(SFDR)要好于40dB。

“DTHA有一个集总输入缓冲器,该缓冲器由一个发射极退化差分放大器及随后的一对发射极跟随器组成。输入端有一个50V片上电阻提供良好的输入匹配。输入缓冲器提供一致的增益和非常低的输出阻抗,可驱动分布式开关型发射极跟随器和输出缓冲器(SEFOB)电路。”论文指出。

“为了避免输入缓冲器输出和分布式SEFOB输入线的端点之间产生多次反射,差分放大器带有50V的负载电阻,它近似匹配分布式SEFOB级电路的对等阻抗。所有构建模块都采用有源电流源来增强低频时的CMRR(共模抑制比),并提供更灵活的电流调制方法。”论文中写道。

“分布式SEFOB电路由三个相同的SEF和通过平衡微带传输线连接的输出缓冲器组成。”论文还写道,“时钟分配是解决采样抖动的最重要因素。。。[A]采用共发共基放大器架构来降低输出的电容负载,并减少由于Miller电容引起的带宽损失。。。分布式输出电路产生顺序性‘跟踪’和‘保持’控制信号并提供给SEFOB单元。”

2 Delta-Sigma的绝技

在ISSCC的delta-sigma报告会期间,ADC设计师透露了在动态范围和功耗方面取得的进步。例如,恩智浦公司提交的“A 56mW CT Quadrature Cascaded SD Modulator with 77dB DR (dynamic range) in a Near Zero-IF 20MHz Band”一文就介绍了一种带连续(CT)正交环路过滤器的级联delta-sigma调制器(图3)。

“第一级电路包含了正交环路滤波器QLF1、模数转换器ADC1i和ADC1q、反馈数模转换器DAC1i和DAC1q。第一级的量化误差Qi+jQq通过将数字输出Y1i和Y1q分别馈给数模转换器DAC2i和DAC2q得到,同时要从ADC1i和ADC1q的输入中减去它们的输出。”该论文写道。

“这一量化误差信号Qi+jQq再馈给由环路滤波器QLF2、模数转换器ADC2i和ADC2q以及数模转换器DAC3i和DAC3q组成的第二级级联电路。两级电路的数字输出都包含了量化误差Qi+jQq,但转移函数不同。因此,第二级输出要馈给一个数字正交噪声取消滤波器(QNCF)以便匹配这两个转移函数。”

“从第一级数字输出的延迟值中减去QNCF输出就可抵消Qi+jQq。结果信号Yi+jYq在有用频段内的量化噪声就非常小。最后,正交抽取滤波器(QDF)还会滤除带外的量化噪声。”论文总结道。

再看看其它架构。“A 10b 160MS/s 84mW 1V Subranging ADC in 90nm CMOS”一文的观点是,子区型(subranging)ADC非常适合混合信号ASIC。加利福尼亚大学洛杉矶分校(UCLA)的Huber等人编写的这篇论文介绍了一款带完整THA的10位、160兆样点/秒的子区型ADC(5位粗ADC、6位精确ADC,带相关的预放和比较器)。

原型功耗在1V时为84mW,在整个奈奎斯特频段上该器件可以获得好于9.1的等效数字或位(ENOB)和75dB的无寄生动态范围(SFDR),到200MHz时仍有8.5的ENOB和7dB的SFDR。在设计中粗ADC和精确ADC的取样开关用相位相反的时钟驱动,因此精确ADC延时增加了1/2个时钟周期,从而使粗ADC有足够的时间执行它自己的量化。

来自UCLA的另外一个小组与***的Realtek合作提交了“An 11b 800MS/s Time-Interleaved ADC with Digital Background Calibration”论文。这篇文章详细介绍了一款针对双绞线上提供10GBastT(IEEE 802.3an)应用而设计的时间交叉采样ADC。这种ADC必须有800兆样点/秒的处理速度,带宽有400MHz,ENOB大于9位。

采用90nm CMOS工艺完成的上述设计使用了4个取样速率为200MHz的交织管线式子ADC、数字校正逻辑、参考电压缓冲器和一个时钟发生器。它在子ADC对之间还采用了运放共享技术。每个子ADC由12个1.5位/级乘法DAC组成,可生成12位输出,有两个额外的位用于校正。

该器件的原型功耗约12mW。在采样率为800MHz时,DNL和INL分别小于0.5和1.6LSB。校正后的信噪加失真率(SINAD)在15MHz和400MHz输入时分别为58dB和54dB。

3 最新的通信芯片

凌力尔特公司的LTC2285是用于数字化高频、宽动态范围信号的双路、14位、125MS/s、低功耗的3V ADC。这款ADC主要设计用于WiMAX基站,它的高数据速率将达到目前标准62MS/s转换器的两倍。

LTC2285的交流性能参数包含奈奎斯特频点处的72.2dB SNR和82dB SFDR。典型的直流参数包括61.5 LSB INL和60.6 LSB DNL。转换噪声是1.3 LSB(rms)。该芯片的工作电压是3V,但独立的输出电压允许输出驱动0.5到3.6V的逻辑电路。目前该芯片已有样品供应,批量生产将在9月份开始。起价为73.5美元。

用于类似应用的AD9640是模拟器件公司(ADI)推出的双路、14位、采样速度超过135MS/s的ADC。该器件在中频为70MHz时的SNR是72.7dBFS,SFDR是85dBc。中频最高可达450MHz。为了简化时钟和减少抖动,AD9640内置有自己的时钟分频器,因此可以在基站DAC使用的同一时钟下工作。

为了简化自动增益控制(AGC),芯片专门包含了两块电路。一块电路用于监视输入的复合信号功率,并产生缓慢响应的增益加/减信号。另一块电路工作于快速检测(FD)模式,可以在最少两个时钟周期内检测出输入的超范围状态,并立即降低增益以避免过度驱动模拟前端。

AD9640具有12和14位分辨率,采样速率有80、105、125和150MS/s四种。14位版本的成本在37.5到87.5美元之间。

2006年年底时,TI公司发布了一款12位、500MS/s的管线型ADC产品,型号为ADS5463。在全速转换条件下其SNR可达64.5 dBFS,输入频率可达500MHz。ADS5463可提供84dBc的SFDR,10.5的ENOB,功耗为2.25W,起价为125美元。

2007年1月份,TI还推出了ADS5547和ADS5527。这两个分别为14位和12位、210MS/s的ADC现在是引脚兼容、高速ADS55xx系列中性能最好的产品。在70MHz的输入频率下,它们能提供高达73.3dBFS的SNR和85dBc的SFDR。

这两款ADC有一个特殊功能,即在低压差分信号(LVDS)和CMOS输出模式下,输出时钟可以在默认位置左右移动。这可以通过一个封装引脚或通过串口实现。移动时钟可实现建立和保持时间之间的调节。还可以调整输出时钟边沿与数据转换的关系。ADS5547的起价是82.5美元。

有关ADS5547的最引人注目的事之一是在产品手册中使用颜色显示性能曲线(图4)。在曲线图中的备注说明指出:“所有图的条件都是25C,AVDD=DRVDD=3.3V,采样频率=210MSPS,正弦波输入时钟,1.5 VPP差分/时钟幅度,50%的时钟占空比,21 dBFS差分模拟输入,内部参考模式,0dB增益,DDR LVDS数据输出(除非另外说明)。”

国家半导体公司(NS)也发布了有16位器件成员的管线ADC系列产品,其中性能最好的是带串行LVDS输出的14位、双路105MS/s芯片。典型的性能参数包括240MHz输入时72dB的SNR和83dB的SFDR。该系列产品由单路和双路、12位和14位、采样速率从65到105MS/s的转换器组成。最顶级的ADC14DS105起价为82.35美元。

在高端采样率方面,NS推出了8位、超高速ADC系列产品。这些产品基于其现有的折叠/内插式架构,可提供6GS/s的数据捕获速率,功耗为3.6W。它们采用一对3GS/s ADC0-83000 ADC交织的技术,无需额外的时钟调整电路。ADC08300的满功率输入带宽为3GHz。

NS公司还采用相同的架构开发了ADC0B83000器件。该器件整合了上述“不带B”版本器件的3GS/s采样率和一个可编程的4kB缓存,主要用于雷达和光信号检测以及距离修正(激光雷达)等应用场合。在这些应用场合,数据都是突发式捕获,并以较低的数据速率传送。

不带缓存的基本ADC083000具有3GHz的全功率带宽。因此它即使在第二奈奎斯特频段中也能采样宽带信号。通过调整片上的采样时钟相位,设计师无需外部时钟调整电路就可以在板上交织多个ADC。ADC083000可针对简单的数据捕获提供标准的1:4复分接输出,或针对精减的引脚数量提供新的1:2输出模式。它还能在输出端提供测试图案用于系统设计和测试。

当以3GS/s采样750MHz输入信号时,ADC083000通常能达到7.0的ENOB、44dB的SNR和54dB的SFDR。带缓存的ADC08B3000在采样后可将数据存储在4kB的FIFO中。一条或两条8位CMOS输出总线再以较低的速率将FIFO中的数据传送到ADC外部的处理器。最高速度是400MB/s。ADC083000在1000片批量时的价格为523美元。

举报

举报

举报

举报