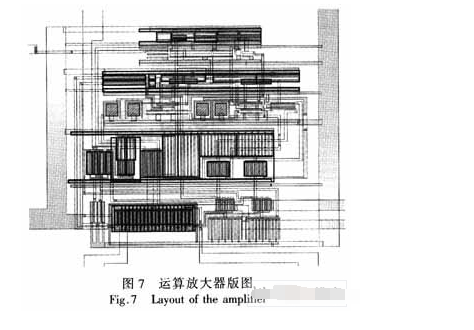

本文设计了一个可用于12 bit,20 MS/s流水线ADC中的采样/保持

电路。该电路使用CSMC公司的0.5μm CMOS工艺库,在20 MS/s采样频率下,当输入信号的频率为9.8193 MHz时,SFDR为76 dB,精度达0.012%,完全满足12 bit要求。本文运用增益增强型折叠式运算放大器,以获得较高的增益和带宽。同时采用栅压自举开关,并通过对电路中的开关组合优化,极大的提高了电路的线性性能;采用全差分结构、底极板采样来消除电荷注入和时钟馈通。该采样保持电路能够直接应用于高速高精度模/数转换器等各种高速模拟系统中。

举报

举报