1 概 述

根据对语音构成的分析,应运而生了多种对音频信号的压缩编码算法,如CELP、RELP、VSELP、MP-MLQ、LPC-10MBE等,它们通过不同的算法,实现对音频信号的压缩。这些压缩编码算法的压缩率、语音质量各有所长,其中美国DVSI(Digital Voice System .Inc)公司提出的先进多带激励AMBE(Advanced Multi-Band Excitation)压缩编码算法是其中的杰出代表。AMBE是基于MBE技术的低比特率、高质量语音压缩算法,具有语音音质好和编码波特率低等优点,并植于DVSI公司的AMBE-1000语音压缩芯片内。该芯片是一高性能的多速率语音编码/解码芯片,其语音编码/解码速率可以在2400~9600b/s之间,以50b的间隔变化。在芯片内部有相互独立的语音编码和解码通道,可同时完成语音的编码和解码任务;并且所有的编码和解码操作都在芯片内部完成,不需要外扩的存储器。AMBE-1000的这些特性使它非常适合于数字语音通信、加密语音通信以及其它需要对语音进行数字处理的场合。

2 AMBE-1000 的工作原理及硬件接口

2.1 基本工作流程

简单地说,AMBE-1000的工作过程如图1所示。AMBE-1000可看成由两个分开的编码器和解码器组成。编码器接收8kHz的语音数据采样流(如16位线性的,8位A律的或8位U律的)和输出一个期望的波特 率的信道数据流。反之,解码器接收一个信道数据流并合成一个语音数据流。AMBE-1000的编码器和解码器的接口时序是完全异步的。

2.2 信道接口

信道接口用于描述从编码器输出的压缩比特流和输入到解码器的压缩比特流。该接口也可输出状态信息,例如可以检测是否有双音多频(DTMF)的语音信号输入。此外,该接口对编/解码器执行更复杂的控制操作(通常在初始化时)。这些控制功能包括语音和纠错码速度的选择、A/D-D/A芯片的设备。在多数的语音传输系统中,实际编码比特流以一定格式从信道中摘录出来,并和系统信息合在一起构成系统传送数据流,通过传输信道发送;在接收端被摘录出来,并通过解码器构成AMBE-1000所需格式的数据流。

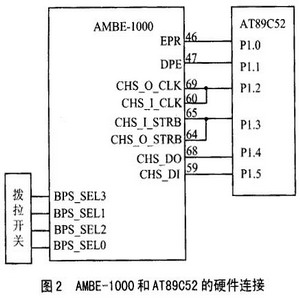

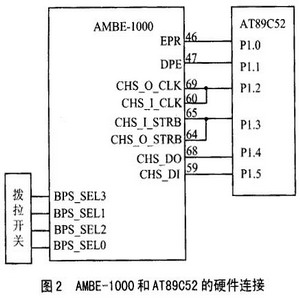

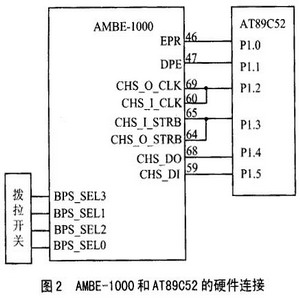

AMBE-1000有多种工作模式:并行和串行、有帧和无帧格式、主动和被动。其中,并行被动帧模式是最灵活和实用的一种工作模式。通过上拉电阻和拨位开关与相应的接口选择引脚相连,就可以选择相应的工作模式。通过采用上述的方法,就可通过选择开关在2400~9600b/s和50~4750b/s间自由选择语音速率和纠错码速率。在串行主动模式下,AMBE-1000的工作时钟为27MHz,CHS_O_CLK的时钟为4.5MHz(27MHz/6),即在0.22μs内需读取1位数据。即使单片机工作在24MHz下,也无法读取该数据,故须采用被动方式,这样就可以自己设置CHS_O_CLK的时钟,可该时钟也需要满足在20ms内能够读取34字节的数据(即1帧数据);同时并口占用较多的接口资源,故采用串行被动帧模式,其硬件连接如图2所示。

2.3 数据格式

AMBE-1000的数据在有帧格式下,每帧由17个字组成。编码器每20ms输出17个字,而解码器则要接收17个字。每帧的前5个字由帧标志(Header)、识别标志(ID)、状态(输出)或控制(输入)信息组成,其余的12个字构成编码/解码数据。这12个字共192位是AMBE-1000以9600b/s方式工作的最大数据率(192b/帧×50帧/s=9600b/s)。当编码/解码的数据率低于9600b/s时,不足的位补0。需要注意的是,无论AMBE-1000工作在什么速率,所有272位(17字×16b=272b)的帧数据(包括任何未用的结尾零)都必须从编码器输出或输入解码器。无帧格式只能用于串行模式。

2.4 AMBE-1000 和TLC32044 的接口电路

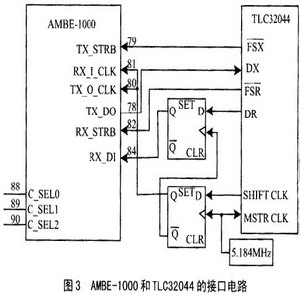

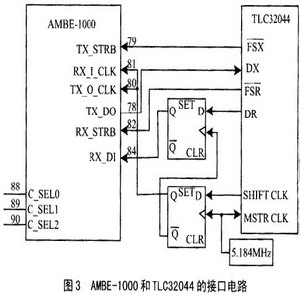

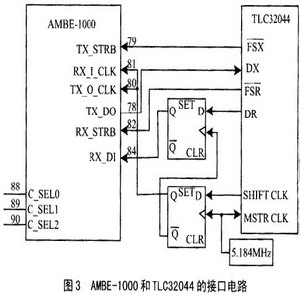

AMBE-1000要求A/D、D/A的语音数据与串行的方式输入、输出。该接口电路的关键是语音数据的帧同步,其硬件接口电路如图3所示。其中5.184MHz作为TLC32044的工作时钟,同时也作为D触发器的触发脉冲。由TLC32044产生的移位脉冲(SHIFT CLK),用于实现比特位的同步传输。通过设置C_SEL0-2为010,来选择TLC32044芯片。

2.5 时钟和复位

AMBE-1000的工作时钟为26~30MHz。它有3种输入方式:TTL时钟源直接输入、CMOS时钟源或振荡器直接输入、采用晶体振荡电路输入。在此系统中,时钟采用晶体振荡电路输入。有效复位信号为低电平,并且须持续6个时钟周期以上。

3 外围接口电路

3.1 TLC32044 的工作原理

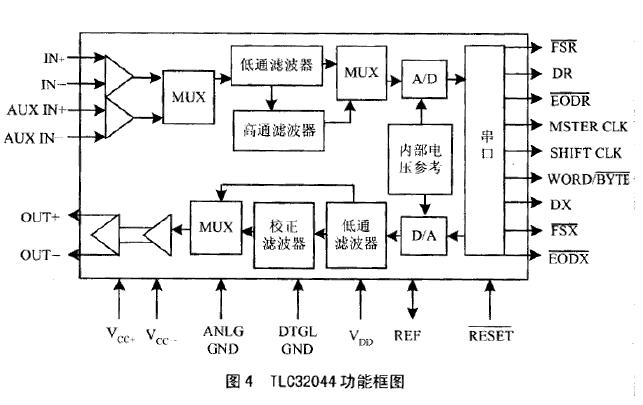

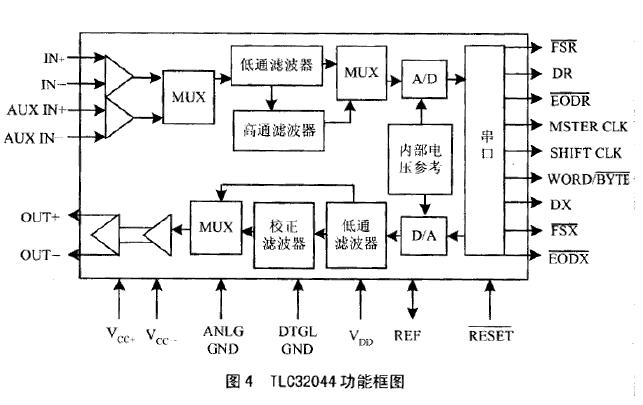

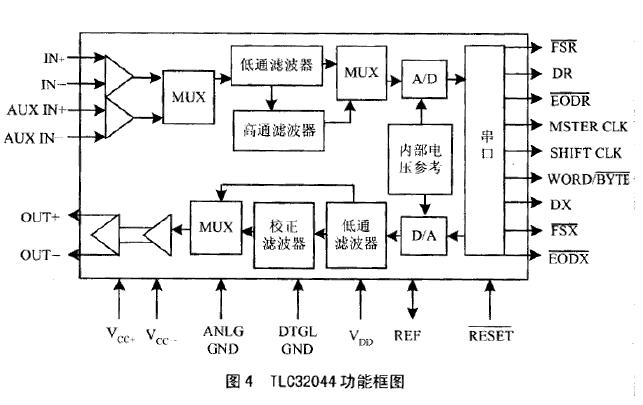

语音信号的数字处理少不了语音信号的A/D与D/A转换。在本次设计中,选用美国TI公司生产的一种14位动态可调的高精度可编程A/D、D/A的TLC32044芯片。如图4所示,TLC32044由反混迭输入滤波器、A/D、D/A、输出重构滤波器等组成。模拟和数字地、模拟和数字电源的分开可降低噪声和保证一个宽的动态范围。模拟电路部分采用差分电路以使噪声达到最小。TLC32044还具采样频率可编程,其采样频率可在7.2kHz~19.2kHz范围内用软件控制,它可工作在同步字、字节传输和异步字、字节传输等4种工作状态,分别采用16bit字或8bit字节串行通信方式,最高具有14bit的转换精度,只需外部提供一个5.184MHz的时钟便可工作。该芯片通过编程可同时容纳2路模拟信号输入。系统上电(或复位)后则按其默认的工作方式工作,即按16bit字或8bit字节串行通信方式,最高具有14bit的转换精度,只需外部提供一个5.184MHz的时钟便可工作。该芯片通过编程可同时容纳2路模拟信号输入。系统上电(或复位)后则按其默认的工作方式工作,即按16bit字同步串行通信,采样频率为8kHz。欲改变TLC32044的工状态,可通过编程并把控制字经由DX脚送入TLC32044。

在DR时序中的D1、D0位是空的,A/D转换的有效精度是D15~D2;而DX时序中的D1、D0位是作为控制位用的。FSR和FSX分别为接收与发送帧同步信号,为8kHz。在同步工作方式下,两者完全相同。

3.2 TLC32044 的外围接口电路

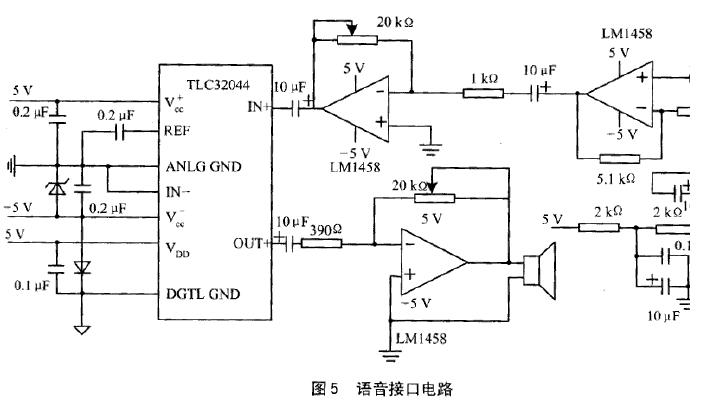

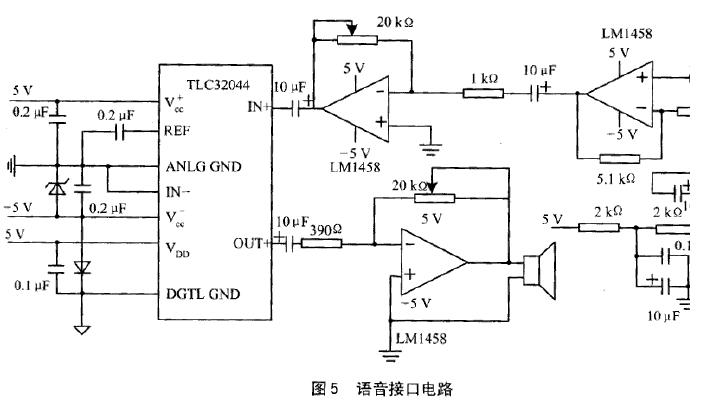

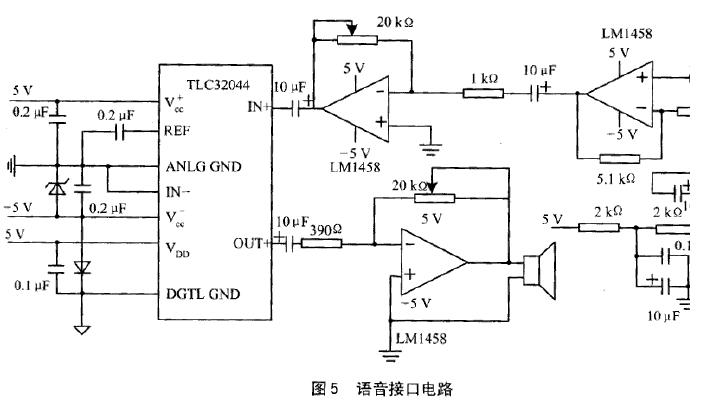

为了实现系统的语音输入和输出,同时保证有效的增益,须对输入输出的语音信号进行放大,电路如图5所示。在该系统中,采用高性能低噪声的LM1458放大器,通过20kΩ的可调电位器来调整输入输出语音信号的增益。在该电路中需要-5V电源,而一般电路仅提供+5V电源,故在电路设计上采用MAX660芯片,实现+5V~-5V电源的转换。这样,整个电路就可用单一电源供电。

4 系统分析

语音压缩系统框图如图6所示。该系统可以自主选择工作速率。在串行主动有帧模式下。可以把AMBE-1000的串行输入输出脚相互短接,进行系统自检,以确认系统是否正常。在系统设计时,须注意模拟地和数字地的区分,避免背景噪声的引入。该电路设计已运用于智能通信终端的端语音压缩,可减少语音的数据量,同时可增加话音的保密性。时该电路也可用于固态采访机,只须加上可擦写的Flash芯片及控制键即可。

1 概 述

根据对语音构成的分析,应运而生了多种对音频信号的压缩编码算法,如CELP、RELP、VSELP、MP-MLQ、LPC-10MBE等,它们通过不同的算法,实现对音频信号的压缩。这些压缩编码算法的压缩率、语音质量各有所长,其中美国DVSI(Digital Voice System .Inc)公司提出的先进多带激励AMBE(Advanced Multi-Band Excitation)压缩编码算法是其中的杰出代表。AMBE是基于MBE技术的低比特率、高质量语音压缩算法,具有语音音质好和编码波特率低等优点,并植于DVSI公司的AMBE-1000语音压缩芯片内。该芯片是一高性能的多速率语音编码/解码芯片,其语音编码/解码速率可以在2400~9600b/s之间,以50b的间隔变化。在芯片内部有相互独立的语音编码和解码通道,可同时完成语音的编码和解码任务;并且所有的编码和解码操作都在芯片内部完成,不需要外扩的存储器。AMBE-1000的这些特性使它非常适合于数字语音通信、加密语音通信以及其它需要对语音进行数字处理的场合。

2 AMBE-1000 的工作原理及硬件接口

2.1 基本工作流程

简单地说,AMBE-1000的工作过程如图1所示。AMBE-1000可看成由两个分开的编码器和解码器组成。编码器接收8kHz的语音数据采样流(如16位线性的,8位A律的或8位U律的)和输出一个期望的波特 率的信道数据流。反之,解码器接收一个信道数据流并合成一个语音数据流。AMBE-1000的编码器和解码器的接口时序是完全异步的。

2.2 信道接口

信道接口用于描述从编码器输出的压缩比特流和输入到解码器的压缩比特流。该接口也可输出状态信息,例如可以检测是否有双音多频(DTMF)的语音信号输入。此外,该接口对编/解码器执行更复杂的控制操作(通常在初始化时)。这些控制功能包括语音和纠错码速度的选择、A/D-D/A芯片的设备。在多数的语音传输系统中,实际编码比特流以一定格式从信道中摘录出来,并和系统信息合在一起构成系统传送数据流,通过传输信道发送;在接收端被摘录出来,并通过解码器构成AMBE-1000所需格式的数据流。

AMBE-1000有多种工作模式:并行和串行、有帧和无帧格式、主动和被动。其中,并行被动帧模式是最灵活和实用的一种工作模式。通过上拉电阻和拨位开关与相应的接口选择引脚相连,就可以选择相应的工作模式。通过采用上述的方法,就可通过选择开关在2400~9600b/s和50~4750b/s间自由选择语音速率和纠错码速率。在串行主动模式下,AMBE-1000的工作时钟为27MHz,CHS_O_CLK的时钟为4.5MHz(27MHz/6),即在0.22μs内需读取1位数据。即使单片机工作在24MHz下,也无法读取该数据,故须采用被动方式,这样就可以自己设置CHS_O_CLK的时钟,可该时钟也需要满足在20ms内能够读取34字节的数据(即1帧数据);同时并口占用较多的接口资源,故采用串行被动帧模式,其硬件连接如图2所示。

2.3 数据格式

AMBE-1000的数据在有帧格式下,每帧由17个字组成。编码器每20ms输出17个字,而解码器则要接收17个字。每帧的前5个字由帧标志(Header)、识别标志(ID)、状态(输出)或控制(输入)信息组成,其余的12个字构成编码/解码数据。这12个字共192位是AMBE-1000以9600b/s方式工作的最大数据率(192b/帧×50帧/s=9600b/s)。当编码/解码的数据率低于9600b/s时,不足的位补0。需要注意的是,无论AMBE-1000工作在什么速率,所有272位(17字×16b=272b)的帧数据(包括任何未用的结尾零)都必须从编码器输出或输入解码器。无帧格式只能用于串行模式。

2.4 AMBE-1000 和TLC32044 的接口电路

AMBE-1000要求A/D、D/A的语音数据与串行的方式输入、输出。该接口电路的关键是语音数据的帧同步,其硬件接口电路如图3所示。其中5.184MHz作为TLC32044的工作时钟,同时也作为D触发器的触发脉冲。由TLC32044产生的移位脉冲(SHIFT CLK),用于实现比特位的同步传输。通过设置C_SEL0-2为010,来选择TLC32044芯片。

2.5 时钟和复位

AMBE-1000的工作时钟为26~30MHz。它有3种输入方式:TTL时钟源直接输入、CMOS时钟源或振荡器直接输入、采用晶体振荡电路输入。在此系统中,时钟采用晶体振荡电路输入。有效复位信号为低电平,并且须持续6个时钟周期以上。

3 外围接口电路

3.1 TLC32044 的工作原理

语音信号的数字处理少不了语音信号的A/D与D/A转换。在本次设计中,选用美国TI公司生产的一种14位动态可调的高精度可编程A/D、D/A的TLC32044芯片。如图4所示,TLC32044由反混迭输入滤波器、A/D、D/A、输出重构滤波器等组成。模拟和数字地、模拟和数字电源的分开可降低噪声和保证一个宽的动态范围。模拟电路部分采用差分电路以使噪声达到最小。TLC32044还具采样频率可编程,其采样频率可在7.2kHz~19.2kHz范围内用软件控制,它可工作在同步字、字节传输和异步字、字节传输等4种工作状态,分别采用16bit字或8bit字节串行通信方式,最高具有14bit的转换精度,只需外部提供一个5.184MHz的时钟便可工作。该芯片通过编程可同时容纳2路模拟信号输入。系统上电(或复位)后则按其默认的工作方式工作,即按16bit字或8bit字节串行通信方式,最高具有14bit的转换精度,只需外部提供一个5.184MHz的时钟便可工作。该芯片通过编程可同时容纳2路模拟信号输入。系统上电(或复位)后则按其默认的工作方式工作,即按16bit字同步串行通信,采样频率为8kHz。欲改变TLC32044的工状态,可通过编程并把控制字经由DX脚送入TLC32044。

在DR时序中的D1、D0位是空的,A/D转换的有效精度是D15~D2;而DX时序中的D1、D0位是作为控制位用的。FSR和FSX分别为接收与发送帧同步信号,为8kHz。在同步工作方式下,两者完全相同。

3.2 TLC32044 的外围接口电路

为了实现系统的语音输入和输出,同时保证有效的增益,须对输入输出的语音信号进行放大,电路如图5所示。在该系统中,采用高性能低噪声的LM1458放大器,通过20kΩ的可调电位器来调整输入输出语音信号的增益。在该电路中需要-5V电源,而一般电路仅提供+5V电源,故在电路设计上采用MAX660芯片,实现+5V~-5V电源的转换。这样,整个电路就可用单一电源供电。

4 系统分析

语音压缩系统框图如图6所示。该系统可以自主选择工作速率。在串行主动有帧模式下。可以把AMBE-1000的串行输入输出脚相互短接,进行系统自检,以确认系统是否正常。在系统设计时,须注意模拟地和数字地的区分,避免背景噪声的引入。该电路设计已运用于智能通信终端的端语音压缩,可减少语音的数据量,同时可增加话音的保密性。时该电路也可用于固态采访机,只须加上可擦写的Flash芯片及控制键即可。

举报

举报

举报

举报