随着集成电路设计的不断发展,集成电路的规模越来越大,设计难度日趋复杂,传统的设计方法已越不能适应集成电路设计发展的需要。基于IP复用的数字IC设计方法是有效提高IC设计产能的关键技术,有助于快速实现工艺先进、功能强大的产品。

微控制器MCU是嵌入式系统的核心,8位MCU IP核具有很高的通用性和灵活性,广泛地应用于工业控制、机械设备、家用电器以及汽车电子等各个领域。本文介绍的是基于 RISC体系结构的8位高速MCUIP软核的设计与实现,采用Verilog HDL自上而下地描述了MCUIP软核的硬件结构,并验证了设计的可行性和正确性。在实际硬件电路中,该IP核的运行频率达到75MHz,可应用于高速控制领域。

系统结构设计

本设计的总线采用了哈佛结构,14位指令字长,8位数据字长,指令集与PIC16F676兼容。它具有35条指令,在连续工作的情况下,除了程序跳转指令要用2个指令周期外,其它的所有指令都可以在1个指令周期内完成。由于哈佛结构总线具有独立的指令总线和数据总线,可同时从程序存储器和数据存储器中分别读取数据,大大提高了MCU内部执行的并行性,简化了控制电路的设计。与更深级流水线相比,简单的指令周期避免了深度流水线增加电路结构复杂性和芯片面积。

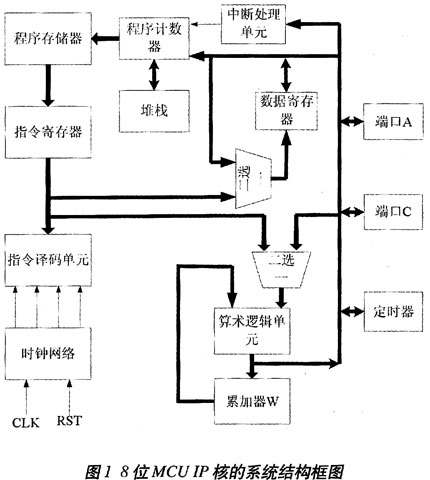

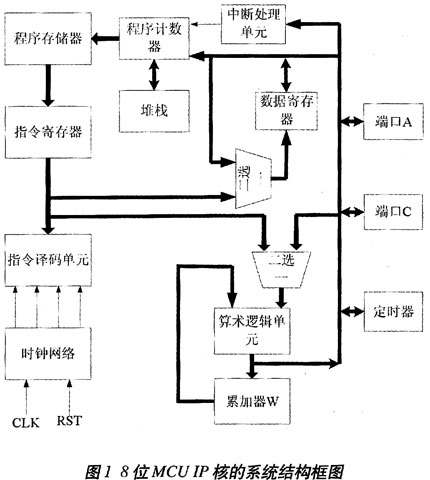

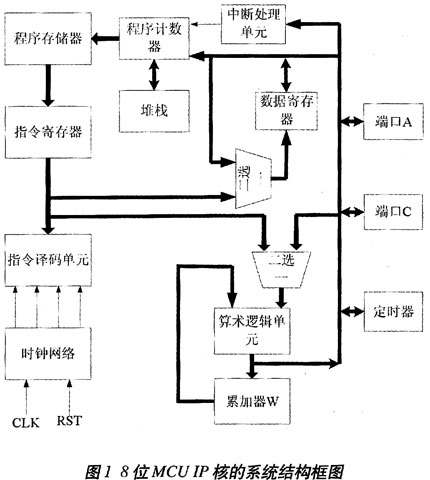

该微处理器在结构上可以划分为四个子系统,分别为控制单元、数据通道、存储单元、I/O单元。其中数据通道包含ALU和一个W工作寄存器。片内程序存储器ROM的容量是8k×14位;数据存储器由包括专用寄存器在内的256个可寻址的8位寄存器组成,通过数据总线与算术逻辑单元ALU相连,系统可以对数据存储器用直接或间接寻址方式进行访问。I/O单元提供了系统内部的数据总线与外界总线的连接接口,实现数据的输入/输出。控制单元则会根据指令产生相应的指示信号控制系统的协调运行。系统结构如图1所示。

MCU IP核的时序设计

时钟网络的时序设计

本设计的时序设计部分采用内部包含4个节拍时钟的结构,时钟网络模块在复位结束后会利用两级嵌套的D触发器将外部时钟(CLK)分频产生4个非重叠正交的节拍时钟信号q1、q2、q3、q4,一个指令周期分为4个状态。节拍时钟会与译码电路产生的控制信号配合,在不同时钟节拍选通不同的电路操作,进而协调整个系统的运行。

二级流水线时序设计

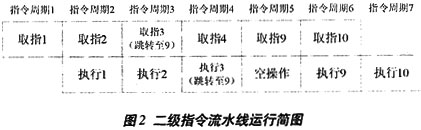

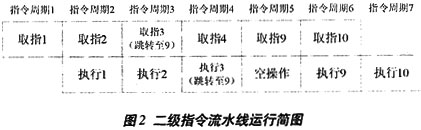

本设计所采用的二级流水线划分为取指和执行两级。系统运行时,会在前一指令周期的q4节拍从ROM中取出下一条待执行的指令并锁存在指令寄存器中,在下一指令周期的q1节拍从指令寄存器中取出指令,同时程序计数器(PC)加1,q2到q4对所取指令进行译码和执行。因此,一条指令的完整执行过程大概分为取指令、指令锁存、指令译码、取操作数、执行、回写、PC+1等7个步骤。从时序上看,指令取指周期与执行周期是并行执行的,即在取指的同时,上一条指令正在进入执行周期。

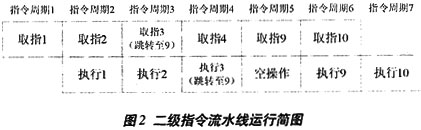

程序跳转指令与其它单周期指令一样进入流水线,在执行程序跳转指令时,屏蔽下一条指令进入指令译码单元,用空操作指令NOP代替。这样,控制逻辑不需要做太大修改就能满足流水线的执行。二级指令流水线操作过程如图2所示。

MCU IP核的内部电路实现

指令寄存器

指令寄存器(IR)是为了实现两级指令流水线而设计的。如果没有指令寄存器,那么取指和执行就分别需要占用一个指令周期。但如果利用IR,在上条指令执行的同时把下一条指令从程序存储器ROM中取出来寄存在IR中,这样在每个指令周期内同时有指令的取出和执行,等效来看,一条指令只需要一个指令周期就可以执行完毕,从而提高了效率。

指令寄存器IR的另外一个功能是当执行分支指令的时候产生空操作,这是采用指令流水线结构所必需的。例如在执行程序跳转指令GOTO的时候,由于GOTO指令会改变程序计数器PC的值,跳转到另外的地址,那么在执行GOTO指令时取得的紧接GOTO的下一条指令就不是要执行的下一条指令,这个已经取得的指令就必须被屏蔽。具体的操作是在执行GOTO指令的时候,指令译码单元产生清零信号使得指令寄存器内部14位寄存单元被清零,那么下一指令周期的输出就变为NOP指令。在执行该空操作的同时把GOTO指令跳转后指向地址对应的指令取出来,在下个指令周期执行。

指令译码单元

指令译码单元在每个时钟周期的q1节拍接收来自IR的14位执行指令,并对指令进行译码工作,给出其它各单元的操作控制信号,包括算术逻辑单元(ALU)的运算控制信号、RAM的读写控制、总线控制器的选择信号、PC寻址等。

算术逻辑单元

算术逻辑单元(ALU)是微控制器运算电路的核心部分,主要功能是按照指令译码器输出的控制信号,实现算术运算、逻辑运算、循环移位等操作。ALU的字宽是8位,在ALU中做运算的2个操作数分别来自W寄存器和数据总线,最后运算的结果由指令译码后的控制信号决定是存放在W寄存器中,还是通用寄存器RAM中。本文通过将加、减操作复用到一个8位超前进位加法器,大大缩短了ALU算术运算的时间,进而提高了整个系统的运行速度。

程序计数器和堆栈

13位的PC对8k×14bit的ROM进行寻址,八级堆栈存储的是ROM的地址,即在主程序中调用的子程序最多允许嵌套8次。当系统复位后PC从0000h地址开始执行,然后在每个指令周期q1节拍,PC自动加1。当执行GOTO指令时,就从指令中获取地址来改变PC的值,然后PC再在此基础上自动加1,顺序执行指令。当执行调用子程序指令CALL指令时,把取指的地址送到堆栈保护起来,然后PC装载子程序入口的地址,接着顺序执行子程序指令直到子程序执行完,程序返回时把堆栈中的地址装载到PC,PC继续自动加1顺序执行指令。

在每个时钟周期,PC会检测是否有来自中断处理单元的中断请求信号发生,一旦有中断响应,PC就会进入中断处理模式,把中断现场的地址送入堆栈保护起来,并在下一指令周期PC指向中断向量地址0004h,这是中断服务程序的入口地址,系统执行中断服务程序直到中断返回,再把保护在堆栈的中断现场地址加载到PC中,然后又顺序执行指令。

定时器/计数器

TIMER0为8位可读写的定时器/计数器单元,其内部有一个分频器,可以通过寄存器配置选择定时或计数工作方式,以及分频器的分频比,分频比最高可达l:128。当TIMER0从FFh到00h计数溢出时,将产生TIMER0中断。

中断处理单元

中断处理单元会响应各个中断源的中断,并向系统的控制电路发出总中断请求信号。该单元设置有8位中断控制寄存器和外设中断寄存器,使用标志位来记录各种中断请求。中断控制寄存器还包括各中断的使能控制位以及全局中断使能位。全局中断使能位将使能(置1时)所有未被屏蔽的中断,或禁止(清零时)所有中断。一旦进入中断服务程序,可通过查询中断标志位确定中断源。

双向I/O

PORTA和PORTC为2个6位双向I/O端口,每个端口有2个物理寄存器,分别是方向寄存器和数据寄存器。方向寄存器控制对应端口的输入/输出属性,数据寄存器负责锁存输入/输出数据。

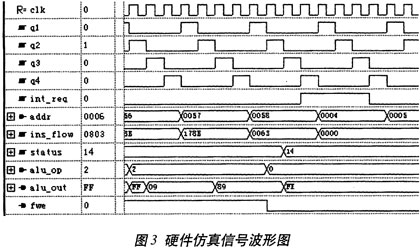

MCU IP核的硬件仿真

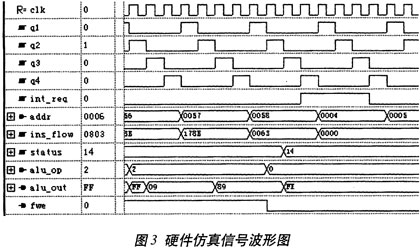

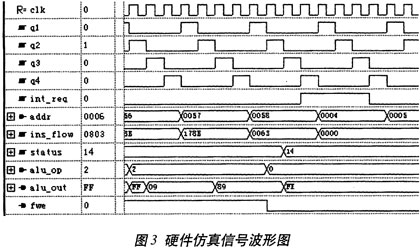

IP软核的仿真测试是设计过程中非常重要的环节,通过自主建立的测试向量库,编写了覆盖所有指令的测试文件,对软核的多种指令、地址和数据组合进行了仿真测试,提高了软核功能仿真的测试覆盖率,保证了设计的正确性。由PORTA和PORTC的输出来验证设计正确性。部分信号波形如图3所示,在正常情况下,地址是在每个指令周期进行加1取指的;当中断信号int_req=1时,地址在下一指令周期跳到中断向量地址0004h,同时屏蔽下一条指令进入指令译码单元,用NOP指令代替。

结语

本文介绍了一个8位RISC结构的高速微控制器IP软核的设计,其指令集与PIC16F676兼容,采用模块化结构,面向硬件映射,保证可综合性。该核使用VerilogHDL为RTL级描述语言,通过了ActiveHDL仿真验证后,用Quartus II 5.0进行综合,并在Altera的EP1C12Q24C08器件上实现了布局布线。经测试,时钟频率达到了75MHz,验证了设计的正确性,为今后的设计积累了大量有益的经验。

随着集成电路设计的不断发展,集成电路的规模越来越大,设计难度日趋复杂,传统的设计方法已越不能适应集成电路设计发展的需要。基于IP复用的数字IC设计方法是有效提高IC设计产能的关键技术,有助于快速实现工艺先进、功能强大的产品。

微控制器MCU是嵌入式系统的核心,8位MCU IP核具有很高的通用性和灵活性,广泛地应用于工业控制、机械设备、家用电器以及汽车电子等各个领域。本文介绍的是基于 RISC体系结构的8位高速MCUIP软核的设计与实现,采用Verilog HDL自上而下地描述了MCUIP软核的硬件结构,并验证了设计的可行性和正确性。在实际硬件电路中,该IP核的运行频率达到75MHz,可应用于高速控制领域。

系统结构设计

本设计的总线采用了哈佛结构,14位指令字长,8位数据字长,指令集与PIC16F676兼容。它具有35条指令,在连续工作的情况下,除了程序跳转指令要用2个指令周期外,其它的所有指令都可以在1个指令周期内完成。由于哈佛结构总线具有独立的指令总线和数据总线,可同时从程序存储器和数据存储器中分别读取数据,大大提高了MCU内部执行的并行性,简化了控制电路的设计。与更深级流水线相比,简单的指令周期避免了深度流水线增加电路结构复杂性和芯片面积。

该微处理器在结构上可以划分为四个子系统,分别为控制单元、数据通道、存储单元、I/O单元。其中数据通道包含ALU和一个W工作寄存器。片内程序存储器ROM的容量是8k×14位;数据存储器由包括专用寄存器在内的256个可寻址的8位寄存器组成,通过数据总线与算术逻辑单元ALU相连,系统可以对数据存储器用直接或间接寻址方式进行访问。I/O单元提供了系统内部的数据总线与外界总线的连接接口,实现数据的输入/输出。控制单元则会根据指令产生相应的指示信号控制系统的协调运行。系统结构如图1所示。

MCU IP核的时序设计

时钟网络的时序设计

本设计的时序设计部分采用内部包含4个节拍时钟的结构,时钟网络模块在复位结束后会利用两级嵌套的D触发器将外部时钟(CLK)分频产生4个非重叠正交的节拍时钟信号q1、q2、q3、q4,一个指令周期分为4个状态。节拍时钟会与译码电路产生的控制信号配合,在不同时钟节拍选通不同的电路操作,进而协调整个系统的运行。

二级流水线时序设计

本设计所采用的二级流水线划分为取指和执行两级。系统运行时,会在前一指令周期的q4节拍从ROM中取出下一条待执行的指令并锁存在指令寄存器中,在下一指令周期的q1节拍从指令寄存器中取出指令,同时程序计数器(PC)加1,q2到q4对所取指令进行译码和执行。因此,一条指令的完整执行过程大概分为取指令、指令锁存、指令译码、取操作数、执行、回写、PC+1等7个步骤。从时序上看,指令取指周期与执行周期是并行执行的,即在取指的同时,上一条指令正在进入执行周期。

程序跳转指令与其它单周期指令一样进入流水线,在执行程序跳转指令时,屏蔽下一条指令进入指令译码单元,用空操作指令NOP代替。这样,控制逻辑不需要做太大修改就能满足流水线的执行。二级指令流水线操作过程如图2所示。

MCU IP核的内部电路实现

指令寄存器

指令寄存器(IR)是为了实现两级指令流水线而设计的。如果没有指令寄存器,那么取指和执行就分别需要占用一个指令周期。但如果利用IR,在上条指令执行的同时把下一条指令从程序存储器ROM中取出来寄存在IR中,这样在每个指令周期内同时有指令的取出和执行,等效来看,一条指令只需要一个指令周期就可以执行完毕,从而提高了效率。

指令寄存器IR的另外一个功能是当执行分支指令的时候产生空操作,这是采用指令流水线结构所必需的。例如在执行程序跳转指令GOTO的时候,由于GOTO指令会改变程序计数器PC的值,跳转到另外的地址,那么在执行GOTO指令时取得的紧接GOTO的下一条指令就不是要执行的下一条指令,这个已经取得的指令就必须被屏蔽。具体的操作是在执行GOTO指令的时候,指令译码单元产生清零信号使得指令寄存器内部14位寄存单元被清零,那么下一指令周期的输出就变为NOP指令。在执行该空操作的同时把GOTO指令跳转后指向地址对应的指令取出来,在下个指令周期执行。

指令译码单元

指令译码单元在每个时钟周期的q1节拍接收来自IR的14位执行指令,并对指令进行译码工作,给出其它各单元的操作控制信号,包括算术逻辑单元(ALU)的运算控制信号、RAM的读写控制、总线控制器的选择信号、PC寻址等。

算术逻辑单元

算术逻辑单元(ALU)是微控制器运算电路的核心部分,主要功能是按照指令译码器输出的控制信号,实现算术运算、逻辑运算、循环移位等操作。ALU的字宽是8位,在ALU中做运算的2个操作数分别来自W寄存器和数据总线,最后运算的结果由指令译码后的控制信号决定是存放在W寄存器中,还是通用寄存器RAM中。本文通过将加、减操作复用到一个8位超前进位加法器,大大缩短了ALU算术运算的时间,进而提高了整个系统的运行速度。

程序计数器和堆栈

13位的PC对8k×14bit的ROM进行寻址,八级堆栈存储的是ROM的地址,即在主程序中调用的子程序最多允许嵌套8次。当系统复位后PC从0000h地址开始执行,然后在每个指令周期q1节拍,PC自动加1。当执行GOTO指令时,就从指令中获取地址来改变PC的值,然后PC再在此基础上自动加1,顺序执行指令。当执行调用子程序指令CALL指令时,把取指的地址送到堆栈保护起来,然后PC装载子程序入口的地址,接着顺序执行子程序指令直到子程序执行完,程序返回时把堆栈中的地址装载到PC,PC继续自动加1顺序执行指令。

在每个时钟周期,PC会检测是否有来自中断处理单元的中断请求信号发生,一旦有中断响应,PC就会进入中断处理模式,把中断现场的地址送入堆栈保护起来,并在下一指令周期PC指向中断向量地址0004h,这是中断服务程序的入口地址,系统执行中断服务程序直到中断返回,再把保护在堆栈的中断现场地址加载到PC中,然后又顺序执行指令。

定时器/计数器

TIMER0为8位可读写的定时器/计数器单元,其内部有一个分频器,可以通过寄存器配置选择定时或计数工作方式,以及分频器的分频比,分频比最高可达l:128。当TIMER0从FFh到00h计数溢出时,将产生TIMER0中断。

中断处理单元

中断处理单元会响应各个中断源的中断,并向系统的控制电路发出总中断请求信号。该单元设置有8位中断控制寄存器和外设中断寄存器,使用标志位来记录各种中断请求。中断控制寄存器还包括各中断的使能控制位以及全局中断使能位。全局中断使能位将使能(置1时)所有未被屏蔽的中断,或禁止(清零时)所有中断。一旦进入中断服务程序,可通过查询中断标志位确定中断源。

双向I/O

PORTA和PORTC为2个6位双向I/O端口,每个端口有2个物理寄存器,分别是方向寄存器和数据寄存器。方向寄存器控制对应端口的输入/输出属性,数据寄存器负责锁存输入/输出数据。

MCU IP核的硬件仿真

IP软核的仿真测试是设计过程中非常重要的环节,通过自主建立的测试向量库,编写了覆盖所有指令的测试文件,对软核的多种指令、地址和数据组合进行了仿真测试,提高了软核功能仿真的测试覆盖率,保证了设计的正确性。由PORTA和PORTC的输出来验证设计正确性。部分信号波形如图3所示,在正常情况下,地址是在每个指令周期进行加1取指的;当中断信号int_req=1时,地址在下一指令周期跳到中断向量地址0004h,同时屏蔽下一条指令进入指令译码单元,用NOP指令代替。

结语

本文介绍了一个8位RISC结构的高速微控制器IP软核的设计,其指令集与PIC16F676兼容,采用模块化结构,面向硬件映射,保证可综合性。该核使用VerilogHDL为RTL级描述语言,通过了ActiveHDL仿真验证后,用Quartus II 5.0进行综合,并在Altera的EP1C12Q24C08器件上实现了布局布线。经测试,时钟频率达到了75MHz,验证了设计的正确性,为今后的设计积累了大量有益的经验。

举报

举报

举报

举报