工艺技术的发展极大地提高了FPGA器件的密度。多个赛灵思Virtex系列中都包含了超过1百万系统门的器件。这种器件密度的提高和300mm晶圆片的使用,为FPGA批量生产创造了条件。

曾经只能使用ASIC来实现的设计现在可以在可编程器件中实现了。最新的90nm Virtex-4器件提供了超过200,000个逻辑单元、6MB的块RAM和接近100个DSP块。创建能够有效利用这些器件中的可用资源并满足性能要求的设计是极具挑战性的工作。幸运的是,今天的EDA软件工具已经发展到能够应对这些挑战了。

逻辑优化、逻辑布局和最小化互连延迟都是实现最大性能的重要工作。时序驱动综合技术对设计性能提供了重大改进。影响时序驱动综合的限制因素是估计布线延迟的精度。

物理综合——基于物理布局和布线信息进行综合——是有效解决这些问题的最前沿技术。物理综合与优化把综合引入到网表生成后的实现决策中,从而进一步扩展了这一技术。这将允许在实现时根据实际的布局布线信息对综合映射与打包决策进行动态复查。

物理综合与优化的优点

逻辑层次之间的互连延迟受逻辑单元布局的接近性、布线拥塞和网络之间对快速布线资源的局部竞争的影响。解决这一问题的方法是在映射、布局和布线期间重新审查综合决策。在映射阶段,可以根据每个时序路径的紧急程度对网表进行重新优化、打包和布局。这一方法减少了达到时序收敛所需的实现次数。

物理综合与优化流程

赛灵思ISE软件提供了多个实现物理综合与优化的软件选项。您可以根据您的设计的具体需求单独或合并使用这些选项。

——定义时序要求

进行有效物理综合的最重要一步是建立准确全面的时序约束。有了这些约束,实现工具就基于可靠信息做出决策,从而改善总体效果。对那些具有严格要求的时钟和I/O引脚进行约束,以减轻剩余设计部分的工作。

定义这些时序约束的最轻松途径是使用ConstraintsEditor。这一图形工具允许您输入时钟频率、多周期与虚假路径(falsepath)约束、I/O时序要求,以及大量其他澄清性要求。约束被写入一个用户约束文件(UCF)中,可在任何文本编辑器中进行编辑。

如果未提供用户定义的时序约束,ISE.8.1i软件提供了一个新功能,将自动为每个内部时钟生成时序约束。在“性能评估模式(PEM)”中,您可以在不必提供时序目标的情况下获得高性能的物理综合与优化效果。

——运行全局优化

对于包含IP核或其他网表的设计,实现的转换(NGDBuild)阶段后生成的NGD文件表示整个设计第一次被完整编译。全局优化是在7.1.01i版本Map中增加的一项新功能,将进行完整设计的组装,并尝试通过重新优化组合与寄存器逻辑来提高设计性能。全局优化(命令行键入map–global_opt)显示可提高设计时钟频率平均7%。

还有两个选项可以让您在此阶段进一步控制优化的完成:时序调整(retiming)(map-retiming)将前后移动寄存器以平衡组合逻辑延迟,和等效寄存器删除(map-equivalent_register_removal)将通过冗余功能性删除寄存器。

——允许时序驱动打包与布局

时序驱动打包与布局是物理综合实现流程的核心。当您采用这个选项(map-timing),布局布线的布局阶段将在Map中完成,允许在初始结果未达最优时对打包决策进行重新审查。时序驱动打包迭代流程替换了无关逻辑打包(unrelatedlogicpacking)。

赛灵思物理综合与优化中包含不同级别的优化。第一级优化是在ISE6.1i软件中引入的,从进行逻辑变换开始,其中包括扇出控制、逻辑复制、拥塞控制,以及改进的延迟估计。这些例程使设计实现了更高效的打包和布局,达到了更快的时钟频率和更高密度的逻辑利用率。

下一级增加了逻辑与寄存器优化;Map可重新安排单元以改进关键路径延迟。这些变换为满足设计时序要求提供了极大的灵活性。使用了大量不同技术(包括内部引脚交换、基本单元切换,以及逻辑重组)将物理单元转换成逻辑上等效的不同结构,以满足设计要求。

ISE8.1i软件引入了另外一级物理综合:组合逻辑优化。该-logic_opt开关将开启一个流程,对设计中的所有组合逻辑进行检查。给定布局和时序信息,您可以对优化LUT结构做出更可靠的决策,以改进总体设计。

物理综合与优化示例

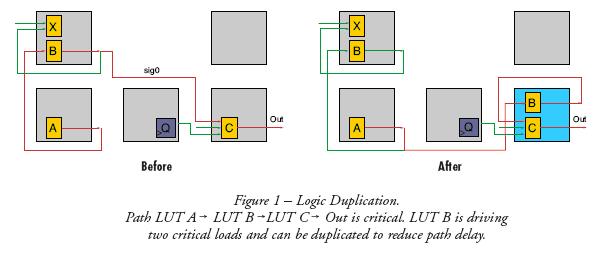

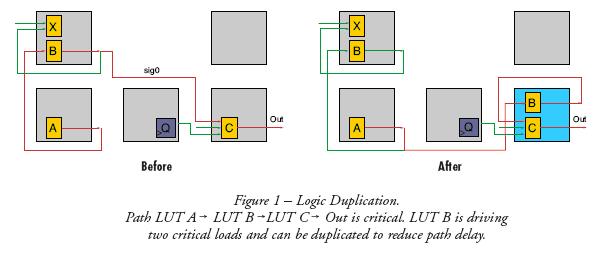

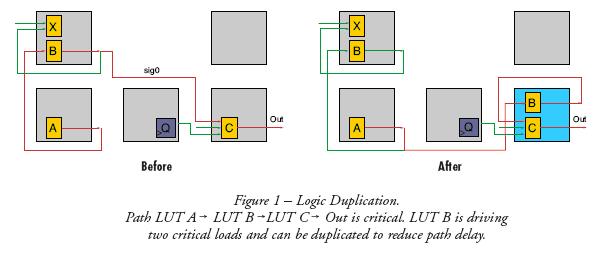

·逻辑复制:如果一个LUT或触发器驱动多个负载,而这些负载中有一个或多个负载的放置位置离驱动源的距离太远因而无法满足时序要求时,可以复制该LUT或触发器并放置在靠近该组负载的地方,从而减小布线延迟(图1)。

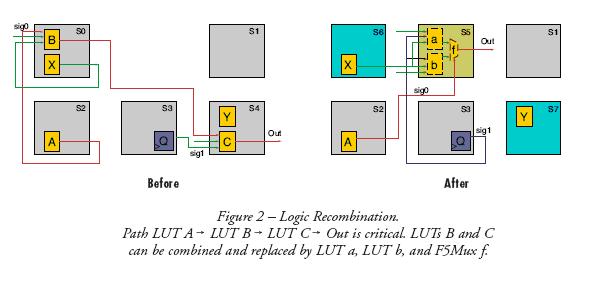

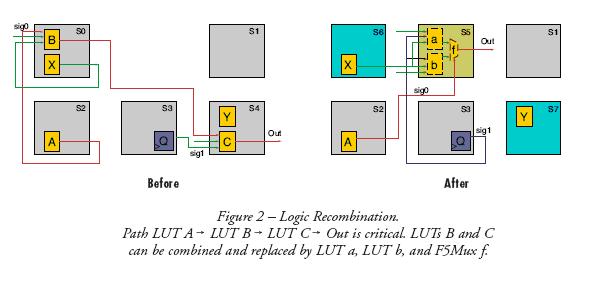

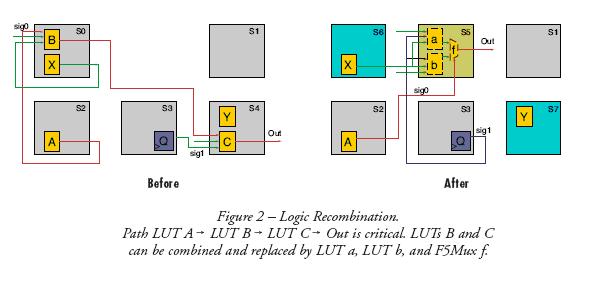

·逻辑重组:如果关键路径跨越多个切片中的多个LUT,可利用较少的切片对该逻辑进行重新组织,采用时序上更高效的LUT与多路转换器组合来降低该路径所需的布线资源(图2)。

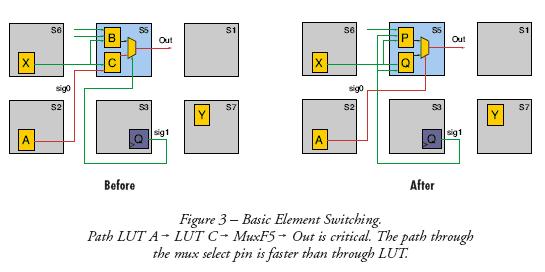

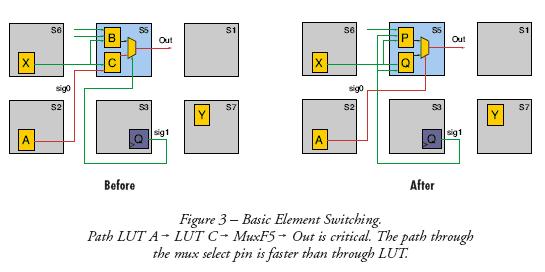

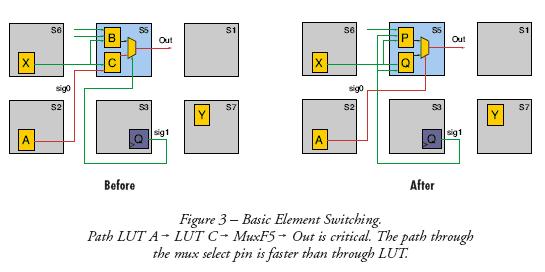

·基本单元切换:如果一个功能使用LUT和多路转换器构成,物理综合与优化可对该功能进行重新安排,将最快的路径(一般通过多路转换器选择引脚)分配给最关键的信号(图3)。

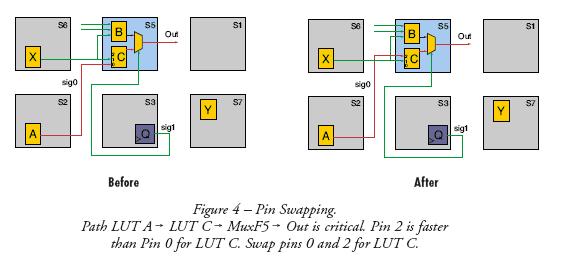

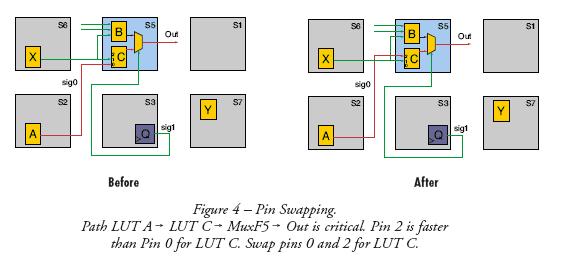

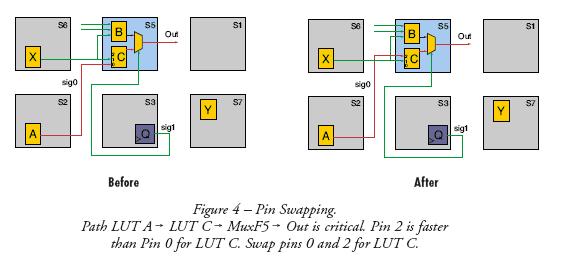

·引脚交换:LUT的每个输入引脚可能有不同的延迟,所有Map拥有交换引脚(以及关联的LUT等式)的能力,以便将最关键的信号放置在最快的引脚上(图4)。

结论

赛灵思工具集中的物理综合与优化功能将进一步走向成熟并随着每个软件版本的发布进行扩展。伴随效果质量的改进,您可以期待着对优化类型的更多控制。其他计划中的强化措施还包括在再优化阶段考虑更多设计单元(例如允许将寄存器移入和移出I/O块或块RAM和DSP块等专门功能),以及将布线阶段包含进物理综合迭代过程,以及优化系统。

赛灵思ISE软件中的物理综合与优化工具是为在实现的打包和布局阶段对您的FPGA设计的结构进行重新检查而创建的。给定时序约束和物理版图信息,在映射和布局布线阶段优化综合决策可极大地改进结果。

工艺技术的发展极大地提高了FPGA器件的密度。多个赛灵思Virtex系列中都包含了超过1百万系统门的器件。这种器件密度的提高和300mm晶圆片的使用,为FPGA批量生产创造了条件。

曾经只能使用ASIC来实现的设计现在可以在可编程器件中实现了。最新的90nm Virtex-4器件提供了超过200,000个逻辑单元、6MB的块RAM和接近100个DSP块。创建能够有效利用这些器件中的可用资源并满足性能要求的设计是极具挑战性的工作。幸运的是,今天的EDA软件工具已经发展到能够应对这些挑战了。

逻辑优化、逻辑布局和最小化互连延迟都是实现最大性能的重要工作。时序驱动综合技术对设计性能提供了重大改进。影响时序驱动综合的限制因素是估计布线延迟的精度。

物理综合——基于物理布局和布线信息进行综合——是有效解决这些问题的最前沿技术。物理综合与优化把综合引入到网表生成后的实现决策中,从而进一步扩展了这一技术。这将允许在实现时根据实际的布局布线信息对综合映射与打包决策进行动态复查。

物理综合与优化的优点

逻辑层次之间的互连延迟受逻辑单元布局的接近性、布线拥塞和网络之间对快速布线资源的局部竞争的影响。解决这一问题的方法是在映射、布局和布线期间重新审查综合决策。在映射阶段,可以根据每个时序路径的紧急程度对网表进行重新优化、打包和布局。这一方法减少了达到时序收敛所需的实现次数。

物理综合与优化流程

赛灵思ISE软件提供了多个实现物理综合与优化的软件选项。您可以根据您的设计的具体需求单独或合并使用这些选项。

——定义时序要求

进行有效物理综合的最重要一步是建立准确全面的时序约束。有了这些约束,实现工具就基于可靠信息做出决策,从而改善总体效果。对那些具有严格要求的时钟和I/O引脚进行约束,以减轻剩余设计部分的工作。

定义这些时序约束的最轻松途径是使用ConstraintsEditor。这一图形工具允许您输入时钟频率、多周期与虚假路径(falsepath)约束、I/O时序要求,以及大量其他澄清性要求。约束被写入一个用户约束文件(UCF)中,可在任何文本编辑器中进行编辑。

如果未提供用户定义的时序约束,ISE.8.1i软件提供了一个新功能,将自动为每个内部时钟生成时序约束。在“性能评估模式(PEM)”中,您可以在不必提供时序目标的情况下获得高性能的物理综合与优化效果。

——运行全局优化

对于包含IP核或其他网表的设计,实现的转换(NGDBuild)阶段后生成的NGD文件表示整个设计第一次被完整编译。全局优化是在7.1.01i版本Map中增加的一项新功能,将进行完整设计的组装,并尝试通过重新优化组合与寄存器逻辑来提高设计性能。全局优化(命令行键入map–global_opt)显示可提高设计时钟频率平均7%。

还有两个选项可以让您在此阶段进一步控制优化的完成:时序调整(retiming)(map-retiming)将前后移动寄存器以平衡组合逻辑延迟,和等效寄存器删除(map-equivalent_register_removal)将通过冗余功能性删除寄存器。

——允许时序驱动打包与布局

时序驱动打包与布局是物理综合实现流程的核心。当您采用这个选项(map-timing),布局布线的布局阶段将在Map中完成,允许在初始结果未达最优时对打包决策进行重新审查。时序驱动打包迭代流程替换了无关逻辑打包(unrelatedlogicpacking)。

赛灵思物理综合与优化中包含不同级别的优化。第一级优化是在ISE6.1i软件中引入的,从进行逻辑变换开始,其中包括扇出控制、逻辑复制、拥塞控制,以及改进的延迟估计。这些例程使设计实现了更高效的打包和布局,达到了更快的时钟频率和更高密度的逻辑利用率。

下一级增加了逻辑与寄存器优化;Map可重新安排单元以改进关键路径延迟。这些变换为满足设计时序要求提供了极大的灵活性。使用了大量不同技术(包括内部引脚交换、基本单元切换,以及逻辑重组)将物理单元转换成逻辑上等效的不同结构,以满足设计要求。

ISE8.1i软件引入了另外一级物理综合:组合逻辑优化。该-logic_opt开关将开启一个流程,对设计中的所有组合逻辑进行检查。给定布局和时序信息,您可以对优化LUT结构做出更可靠的决策,以改进总体设计。

物理综合与优化示例

·逻辑复制:如果一个LUT或触发器驱动多个负载,而这些负载中有一个或多个负载的放置位置离驱动源的距离太远因而无法满足时序要求时,可以复制该LUT或触发器并放置在靠近该组负载的地方,从而减小布线延迟(图1)。

·逻辑重组:如果关键路径跨越多个切片中的多个LUT,可利用较少的切片对该逻辑进行重新组织,采用时序上更高效的LUT与多路转换器组合来降低该路径所需的布线资源(图2)。

·基本单元切换:如果一个功能使用LUT和多路转换器构成,物理综合与优化可对该功能进行重新安排,将最快的路径(一般通过多路转换器选择引脚)分配给最关键的信号(图3)。

·引脚交换:LUT的每个输入引脚可能有不同的延迟,所有Map拥有交换引脚(以及关联的LUT等式)的能力,以便将最关键的信号放置在最快的引脚上(图4)。

结论

赛灵思工具集中的物理综合与优化功能将进一步走向成熟并随着每个软件版本的发布进行扩展。伴随效果质量的改进,您可以期待着对优化类型的更多控制。其他计划中的强化措施还包括在再优化阶段考虑更多设计单元(例如允许将寄存器移入和移出I/O块或块RAM和DSP块等专门功能),以及将布线阶段包含进物理综合迭代过程,以及优化系统。

赛灵思ISE软件中的物理综合与优化工具是为在实现的打包和布局阶段对您的FPGA设计的结构进行重新检查而创建的。给定时序约束和物理版图信息,在映射和布局布线阶段优化综合决策可极大地改进结果。

举报

举报

举报

举报