1 前言

目前示波器的种类繁多,其频带由0.1 Hz到几十MHz,甚至上百MHz,还具有存储显示和打印功能。而频带越宽,A/D和D/A转换器的速度越高,价格也越贵,所以现在的示波器价格昂贵,功能单一。这里提出的数字示波器输入频率范围为10 Hz~10 MHz,幅度范围为16 mV~8 V;而垂直灵敏度有3档,水平灵敏度有8档;且信号幅度和周期测量误差都小于1%;能对波形上下,左右移动,拉宽和缩窄;并能掉电存储波形和显示两通道的相位差。该数字示波器的价格低廉,功能强大,精度较高,应用于多种场合,产品携带方便。

2 方案设计

2.1 采样方案

由于系统需要以小于1 MHz的实时采样率来采样频率为10 Hz~10 MHz的信号,且一个周期至少采集20个样本点,因此对于频率小于50 kHz的信号进行实时采样,而对于频率高于此的信号则需等效采样,最高等效采样率为200 MHz。

2.2 触发方案

由于该系统要求采用内部触发方式,即以输入信号本身为系统提供触发。因此采用数字电路触发方案,在FPGA内设触发电平,用A/D转换器实时采集输入信号,当采集到的电压等于触发电平时,产生触发。但由于A/D转换器的采样率和位数有限,不可能每次都采集到等于触发电平的点。若将触发电平设置为一段合适的电压范围,这样可以保证输出信号波形稳定。

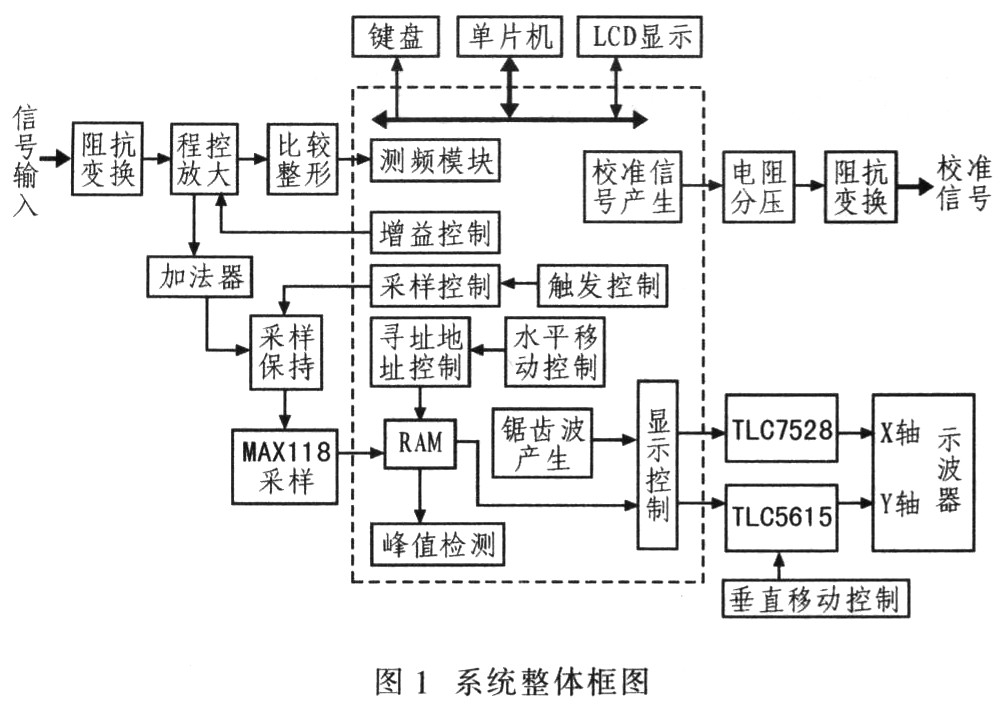

3 系统整体设计

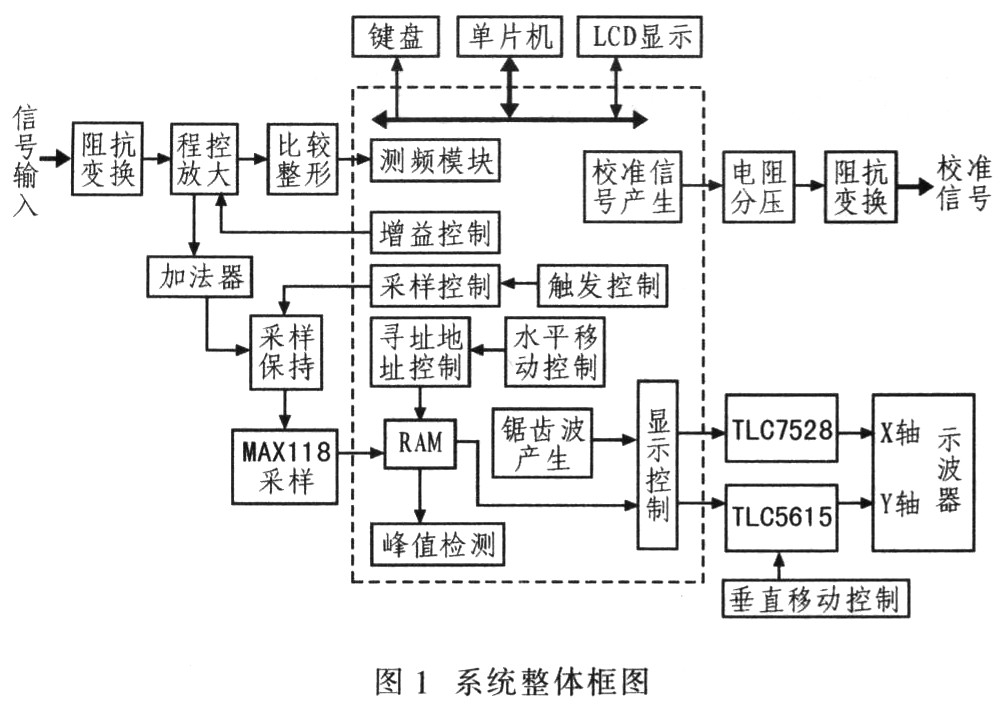

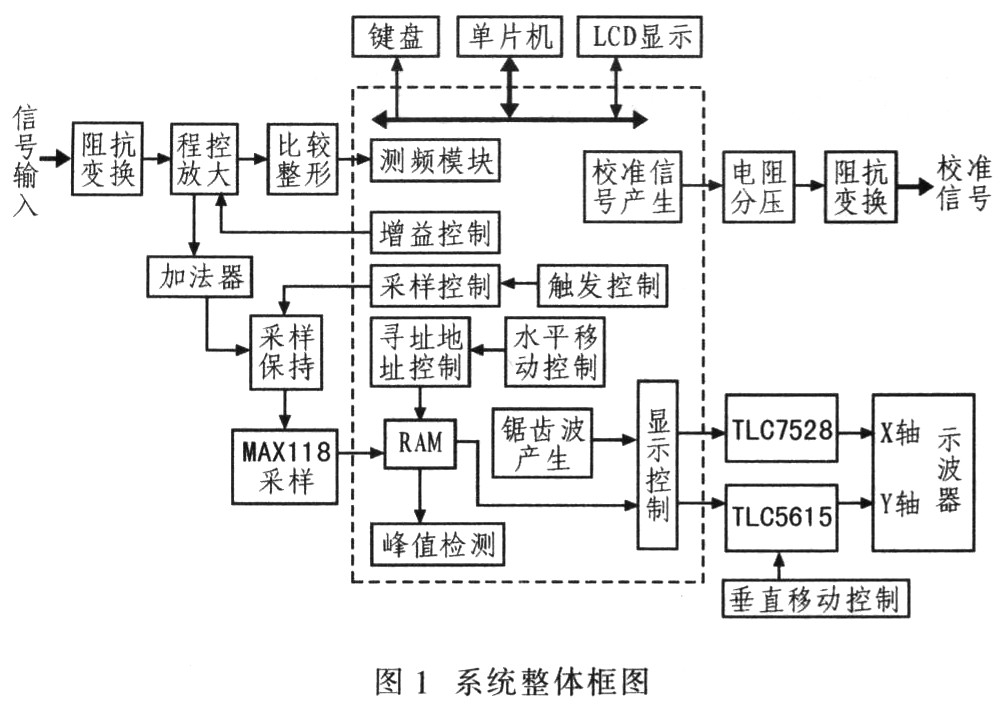

信号经过阻抗变换网络和程控放大环节,幅度被调理到一定的范围内。调理后的信号输入到比较整形模块,将输出的等频率的方波信号送进FPGA内的测频模块进行频率测量;同时,调理后的信号经采样保持电路送入采样模块,用MAX118对频率小于和大于50 kHz的信号分别进行实时采样和等效采样。采集的信号存储在FPGA内部的双端口RAM中,并能在通用示波器中显示信号波形,并具有单次触发和连续触发、存储波形、波形水平移动、垂直移动、产生100 kHz校准信号等功能。系统整体框图如图1所示。

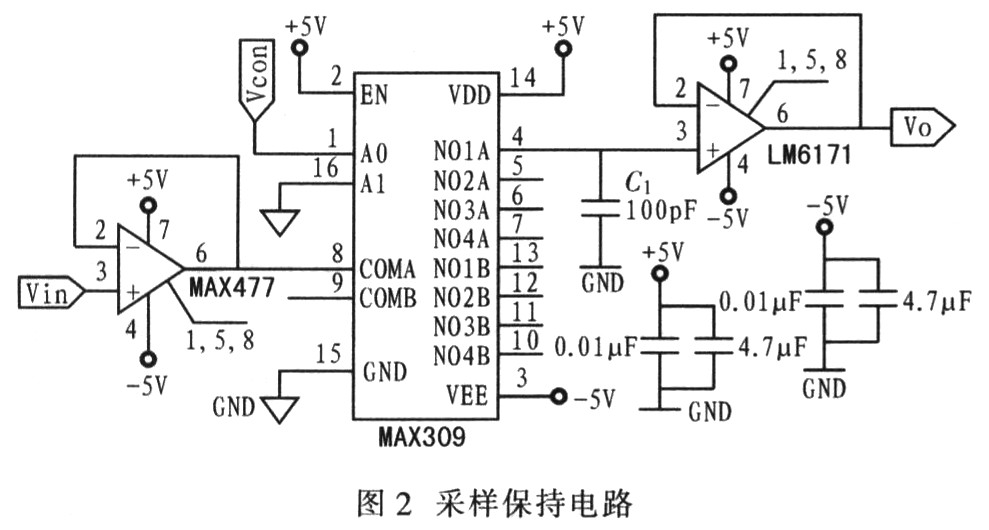

3.1 采样保持电路

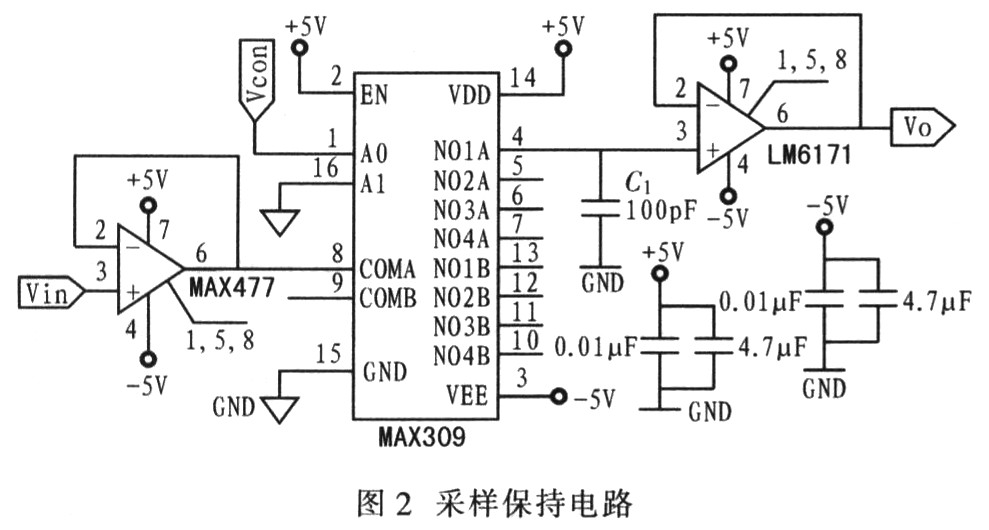

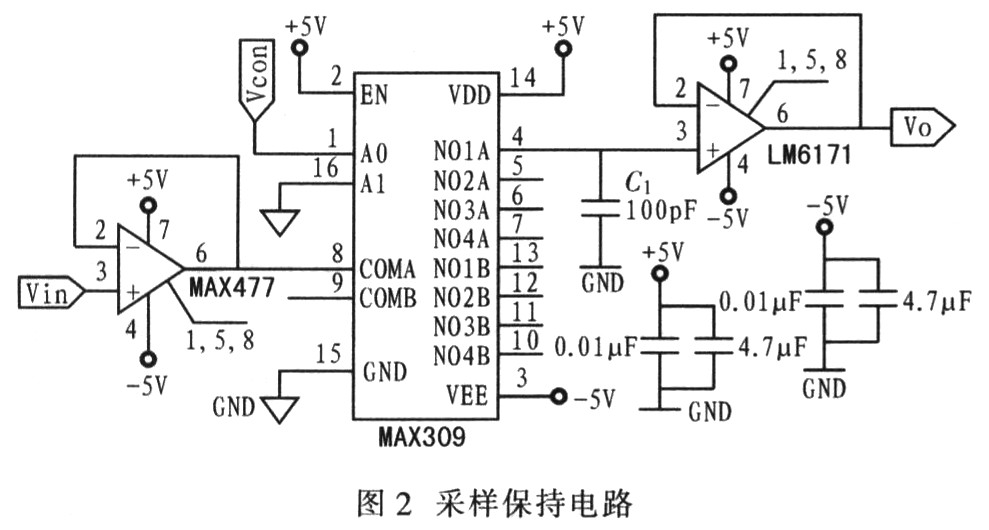

采样保持电路如图2所示。当模拟开关导通时,输入信号Vin经过模拟开关对电容C1充电,充电结束后,Vc1=Vin。当模拟开关断开时,电容C1上的电压在一段时间内保持不变,电容的漏电越小,运放的输入阻抗越大,Vcl保持的时间越长。选择合适的保持时间。可保证采样时的A/D转换输入端信号稳定。

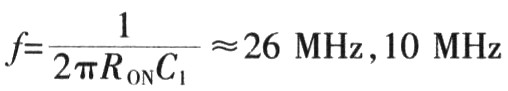

采用MAX309作为模拟开关,引脚A0和A1控制通道选择。使用模拟开关的NO1通道输出,将引脚A1接地,通过控制引脚A0的电平可控制信号是否能传输到后级LM6171的输入端。C1采用低漏独石电容,取100 pF;MAX309的导通电阻RON为60 Ω,RON与C1构成了一个一阶低通滤波器,截止频率

,10MHz的信号输入到采样保持电路,幅度不变。

前级的MAX477和后级LM6171接成高输入阻抗的射级跟随器,实现信号隔离。

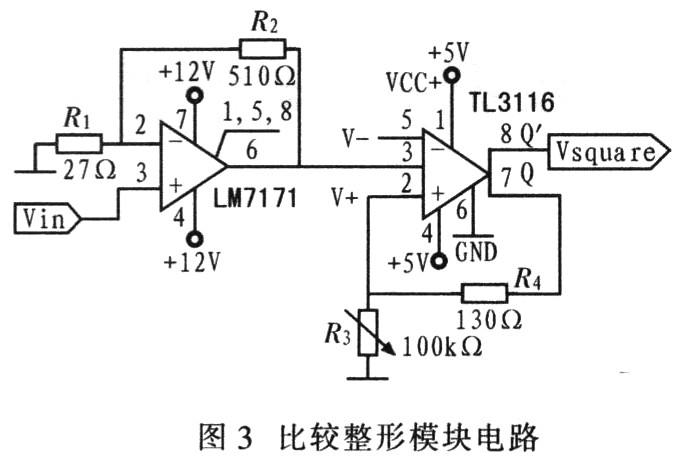

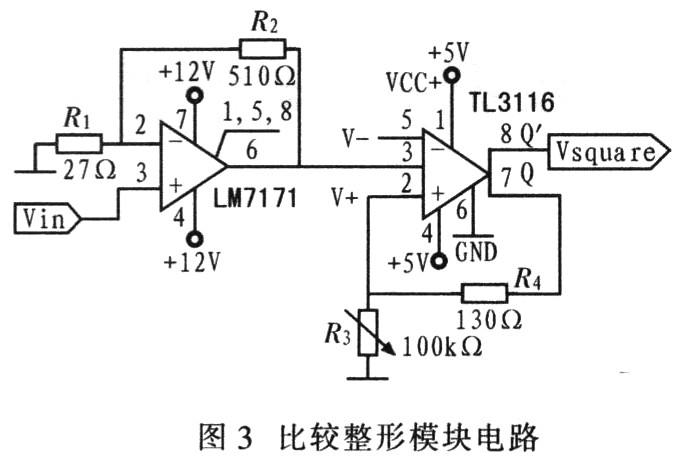

3.2 比较整形电路

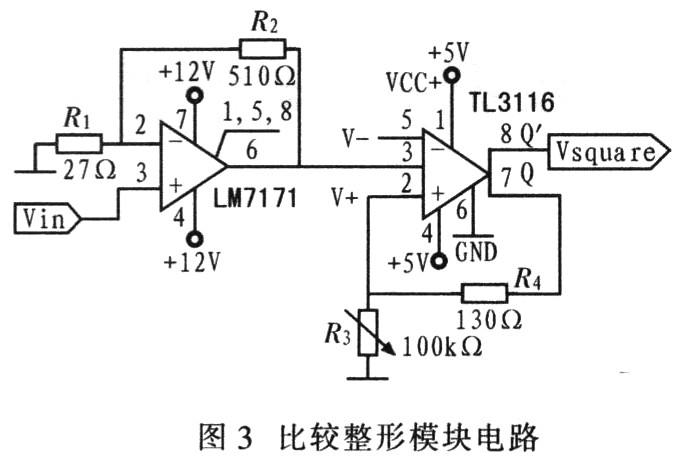

采用TI公司的TL3116,典型传输延迟时间为10 ns。将其接为滞回模式,可以抑制噪声引起的误翻转。在比较器输入前级接一级增益为20的放大器。图3为该系统的比较整形电路。

4 软件程序设计

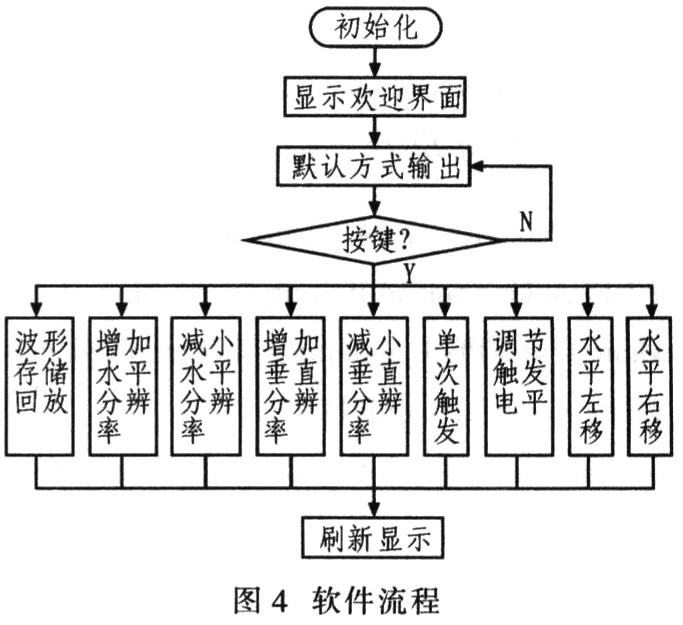

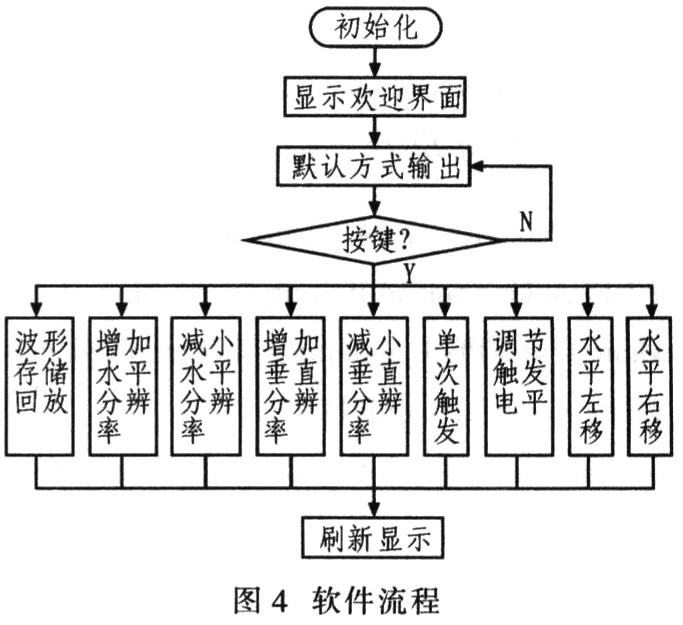

该系统的软件设计充分利用模块化设计思想。该系统是单片机结合FPGA的控制系统,软件设计充分利用FPGA的强大逻辑和计算功能,完成采样时序的控制、数据存储、数据处理、幅度测量、频率测量、触发控制、水平移动控制等。单片机控制键盘、显示,并通过与FPGA的接口来实现不同功能。软件流程如图4所示。

5 结束语

该系统输入信号频率范围为10 Hz~100 MHz.幅度范围为16 mV~8 V,以低于1 MHz的实时采样率实现等效采样率为200 MHz的等效采样。输出波形稳定,垂直灵敏度有1 V/div、0.1 V/div、2 mV/div共3档,水平灵敏度有20 ms/div、2 ms/div、1 ms/div、40 μs/div、20μs/div、2μs/div、200 ns/div、100 ns/div共8档。信号幅度测和周期测量误差都小于1%,并实现单次触发、连续触发,触发电平可调,波形存储与回放,波形水平、垂直移动等功能,且人机界面友好。

1 前言

目前示波器的种类繁多,其频带由0.1 Hz到几十MHz,甚至上百MHz,还具有存储显示和打印功能。而频带越宽,A/D和D/A转换器的速度越高,价格也越贵,所以现在的示波器价格昂贵,功能单一。这里提出的数字示波器输入频率范围为10 Hz~10 MHz,幅度范围为16 mV~8 V;而垂直灵敏度有3档,水平灵敏度有8档;且信号幅度和周期测量误差都小于1%;能对波形上下,左右移动,拉宽和缩窄;并能掉电存储波形和显示两通道的相位差。该数字示波器的价格低廉,功能强大,精度较高,应用于多种场合,产品携带方便。

2 方案设计

2.1 采样方案

由于系统需要以小于1 MHz的实时采样率来采样频率为10 Hz~10 MHz的信号,且一个周期至少采集20个样本点,因此对于频率小于50 kHz的信号进行实时采样,而对于频率高于此的信号则需等效采样,最高等效采样率为200 MHz。

2.2 触发方案

由于该系统要求采用内部触发方式,即以输入信号本身为系统提供触发。因此采用数字电路触发方案,在FPGA内设触发电平,用A/D转换器实时采集输入信号,当采集到的电压等于触发电平时,产生触发。但由于A/D转换器的采样率和位数有限,不可能每次都采集到等于触发电平的点。若将触发电平设置为一段合适的电压范围,这样可以保证输出信号波形稳定。

3 系统整体设计

信号经过阻抗变换网络和程控放大环节,幅度被调理到一定的范围内。调理后的信号输入到比较整形模块,将输出的等频率的方波信号送进FPGA内的测频模块进行频率测量;同时,调理后的信号经采样保持电路送入采样模块,用MAX118对频率小于和大于50 kHz的信号分别进行实时采样和等效采样。采集的信号存储在FPGA内部的双端口RAM中,并能在通用示波器中显示信号波形,并具有单次触发和连续触发、存储波形、波形水平移动、垂直移动、产生100 kHz校准信号等功能。系统整体框图如图1所示。

3.1 采样保持电路

采样保持电路如图2所示。当模拟开关导通时,输入信号Vin经过模拟开关对电容C1充电,充电结束后,Vc1=Vin。当模拟开关断开时,电容C1上的电压在一段时间内保持不变,电容的漏电越小,运放的输入阻抗越大,Vcl保持的时间越长。选择合适的保持时间。可保证采样时的A/D转换输入端信号稳定。

采用MAX309作为模拟开关,引脚A0和A1控制通道选择。使用模拟开关的NO1通道输出,将引脚A1接地,通过控制引脚A0的电平可控制信号是否能传输到后级LM6171的输入端。C1采用低漏独石电容,取100 pF;MAX309的导通电阻RON为60 Ω,RON与C1构成了一个一阶低通滤波器,截止频率

,10MHz的信号输入到采样保持电路,幅度不变。

前级的MAX477和后级LM6171接成高输入阻抗的射级跟随器,实现信号隔离。

3.2 比较整形电路

采用TI公司的TL3116,典型传输延迟时间为10 ns。将其接为滞回模式,可以抑制噪声引起的误翻转。在比较器输入前级接一级增益为20的放大器。图3为该系统的比较整形电路。

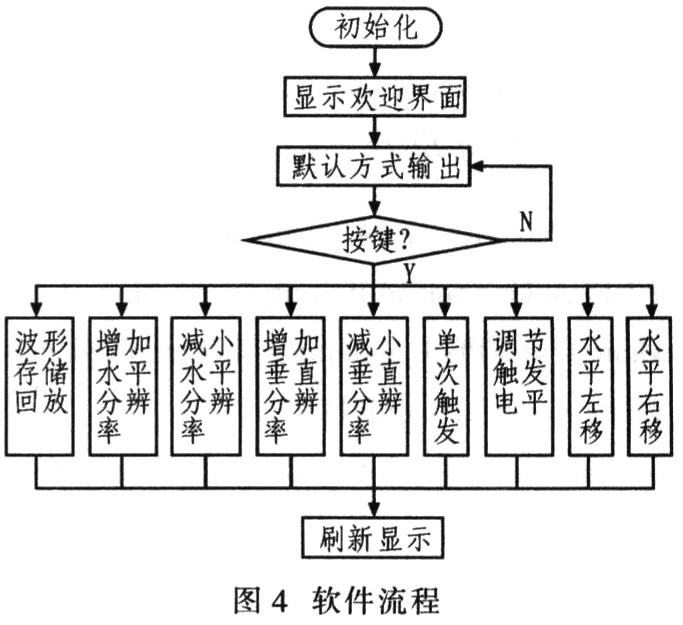

4 软件程序设计

该系统的软件设计充分利用模块化设计思想。该系统是单片机结合FPGA的控制系统,软件设计充分利用FPGA的强大逻辑和计算功能,完成采样时序的控制、数据存储、数据处理、幅度测量、频率测量、触发控制、水平移动控制等。单片机控制键盘、显示,并通过与FPGA的接口来实现不同功能。软件流程如图4所示。

5 结束语

该系统输入信号频率范围为10 Hz~100 MHz.幅度范围为16 mV~8 V,以低于1 MHz的实时采样率实现等效采样率为200 MHz的等效采样。输出波形稳定,垂直灵敏度有1 V/div、0.1 V/div、2 mV/div共3档,水平灵敏度有20 ms/div、2 ms/div、1 ms/div、40 μs/div、20μs/div、2μs/div、200 ns/div、100 ns/div共8档。信号幅度测和周期测量误差都小于1%,并实现单次触发、连续触发,触发电平可调,波形存储与回放,波形水平、垂直移动等功能,且人机界面友好。

举报

举报

举报

举报