在任何一个设计人员的工具箱里,集成电路放大器都是最基本的构件模块之一,它也是目前市面上最全能的产品之一。放大器具有多项功能,比如驱动ADC,驱动多个视频负载,作为视频或其他类型滤波器而工作,驱动高速仪器信号等等。它们还可以作为振荡器。不过,实际中这种方案存在一些问题。因为放大器应该只在设计人员需要的时候才振荡,而如果电路板设计不正确,放大器却会自行其是,随意振荡。那么,设计人员应该如何避免这种有害的振荡呢?试回忆一下我们以前在电子课程里学过的知识,即振荡与电容、电感和反馈相关。因此,关键在于精心设计电路板,减少或消除任何无关的电容性和电感性反馈路径。对于较高速的放大器(大于50MHz)而言,这尤其重要。

电路板、负载(尤其是电容性负载)和/或版图设计,都会引入无形的电容和电感。此外,流入电路板各处旁路电容的电流可能产生不同的路径,从而导致失真。因此,有些号称减少失真的技术其实是适得其反,与避免振荡的设计规则背道而驰。那么,在进行放大器或视频滤波器的版图设计时,为了保持全局平衡,减少失真和振荡,需要考虑到哪些事项呢?

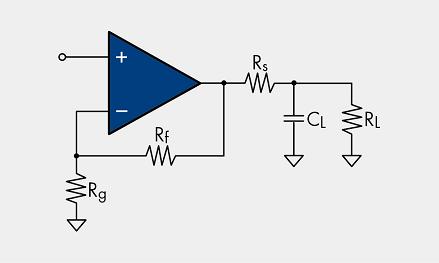

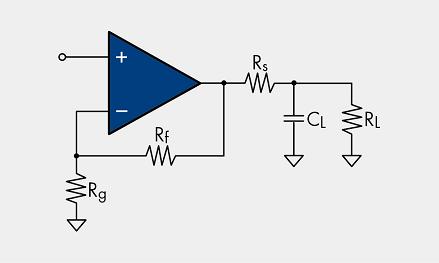

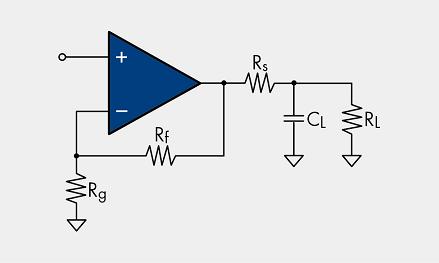

首先我们来看看振荡器,在利用放大器直接驱动电容性负载时,负载会与放大器的输出阻抗会产生相位滞后,而相位滞后将导致脉冲尖峰或振荡。有些放大器能够直接驱动电容性负载,但有些放大器则需要在放大器的输出端增加一个小串联电阻(Rs)来提高放大器的稳定性和建立时间(settling time)性能。

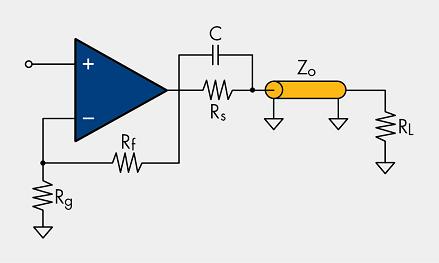

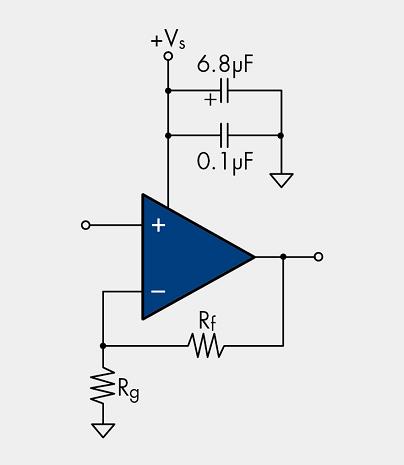

图1:在输出端增加Rs提高稳定性。

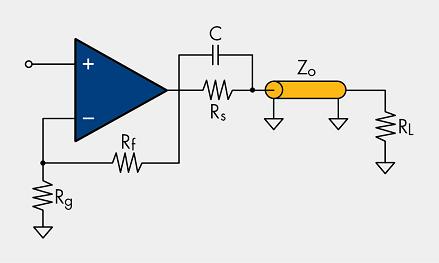

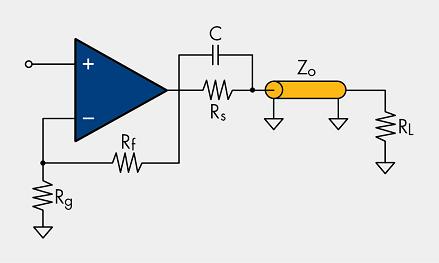

图2给出了驱动传输电缆(如同轴电缆)的典型电路配置图。电阻Rs和RL应该等于电缆的特征阻抗(Zo),而电容C应该可被用来在更大的频率范围对电缆进行匹配,以对随频率提高而增加的放大器输出阻抗进行补偿。

图2:驱动电缆或传输线的典型电路图。

高频放大器很容易受电路布局所致失真的影响,即使是低频放大器(比如音频放大器),也具有非常严格的失真要求。总谐波失真(THD)是音频质量的主要指标,因此,减少版图引起的失真十分关键。

失真的一个重要原因是PCB中的接地电流效应。这种效应来自于流入每个电源和各电源旁路电容的电流,该电流与路径的电导率成比例。各个路径都存在不同的传导性,从而导致失真。因为即使PCB本身的材料是线性的,电路板的行为也会表现出“空间非线性”特性。这是因为旁路电容分布在电路板的不同位置,导致接地电流沿不同的路径流入各个旁路电容。路径不同导致接地电流流经的接地电阻输入一端的电压受到影响,而另一端则不会。结果是输入信号电压被不均衡地调整,导致非线性的产生。在这种情况下,如果一个极性被调节,而另一个却没有,就会造成二次谐波失真。换一句话说,如果只有正弦波的一个极性被调节,结果将不再是正弦波,这种失真的影响是显而易见的。为了避免失真,设计人员可以使用共有接地点并在输出端采用接地旁路电容。

高频电路板版图设计的主要规则是使高频旁路电容尽可能靠近封装的电源引脚。不过,经验证明,稍微延长高频旁路电容的连接走线可以提高平坦度和差分增益,从而减少失真。设计规则当然有益,而设计人员的实践经验也十分有用,可以确保规则与实际的一致性。

在电路板上设计视频滤波驱动器时,很重要的一点是,应该把输入耦合电容和端接电阻靠近输入引脚放置,以获得最佳信号完整性。图3所示为视频滤波器/驱动器的一种典型AC耦合输入配置。在这种配置中,采用0.1uF陶瓷电容来对输入信号进行AC耦合。如果输入信号不低于接地电位,钳位电路不激活;但若输入信号低于接地电位,则钳位电路会把同步端最低电压设置为恰好低于接地电位。钳位电路设置的输入电平,结合内部DC偏移量,将使输出信号保持在可接受的范围之内,大约在250mV左右。这种钳位特性还允许参考电平为地的DAC输出直接驱动直流耦合输入。

。

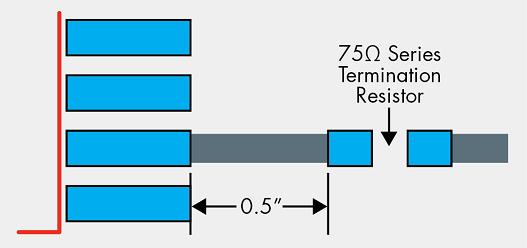

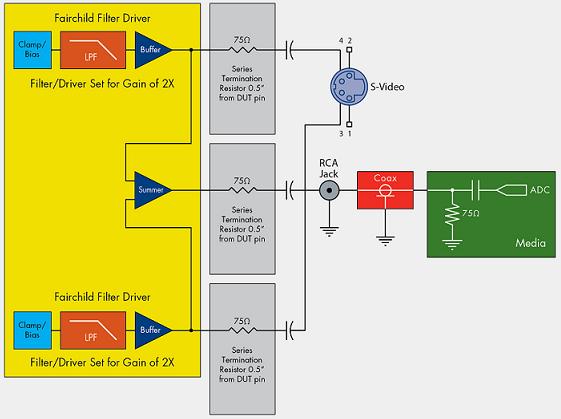

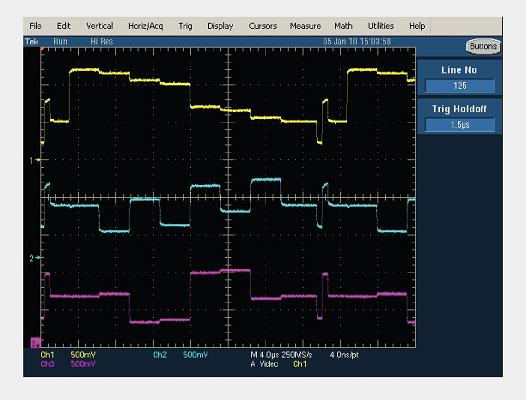

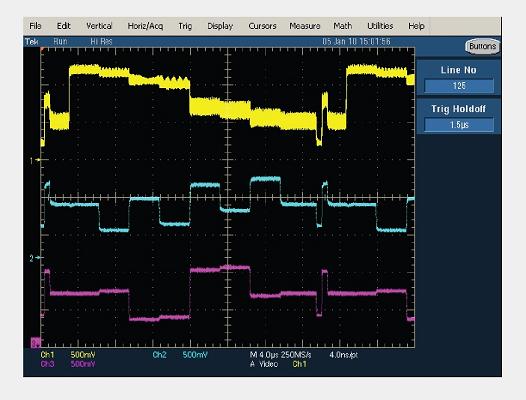

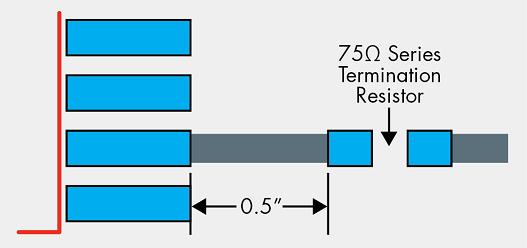

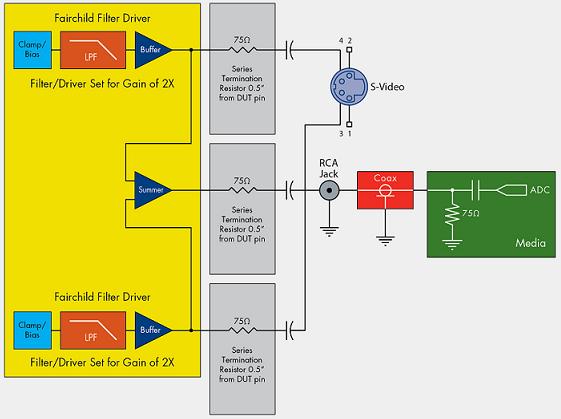

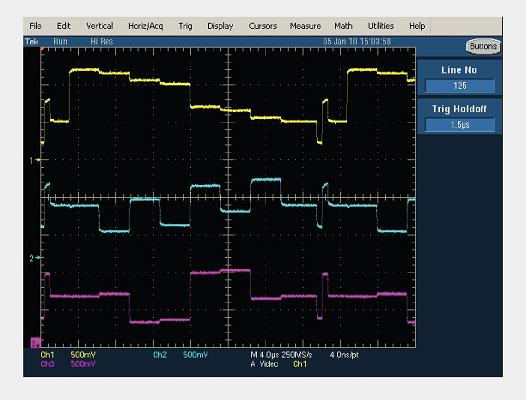

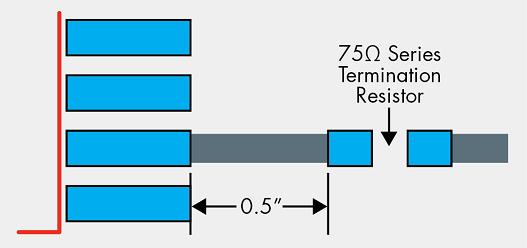

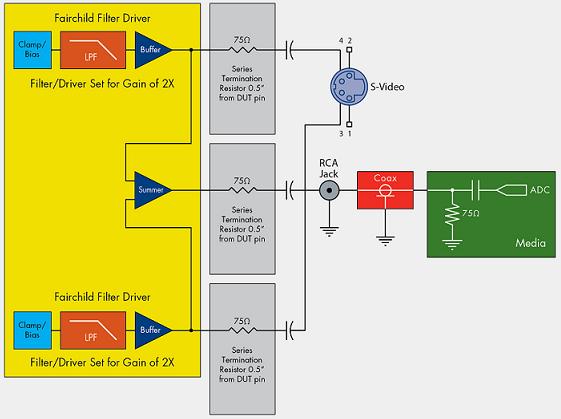

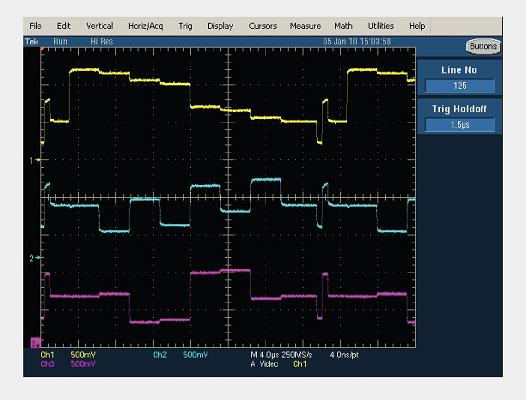

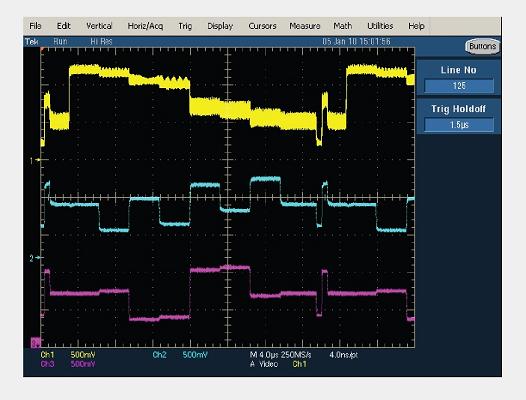

为了获得最高的输出信号质量,串联端接电阻必须尽可能靠近器件的输出引脚放置。这将大大减少寄生电容和寄生电感对驱动器输出的影响。从器件引脚到串联端接电阻的距离不应该超过0.5英寸(见图4)。图5是作为多媒体设备中作为输出驱动器的视频滤波器/驱动器的典型原理示意图。在图5所示的情况下,多媒体设备的复合视频信号端子接多媒体设备,S视频输出端子开通。在这时,让串联端接电阻靠近器件的输出引脚非常关键,可以把寄生电容对滤波器输出驱动器的影响降至最小,从而避免输出端出现振荡。图6所示为飞兆半导体的FMS6346A视频滤波驱动器驱动25pF 的负载,图7所示为FMS6346A驱动47pF的电容性负载。这表明,电容越小,性能越好。

图4:器件引脚到串联端接电阻的距离不应该超过0.5英寸。

图5:FMS6346A 视频滤波器输出到 S-视频。

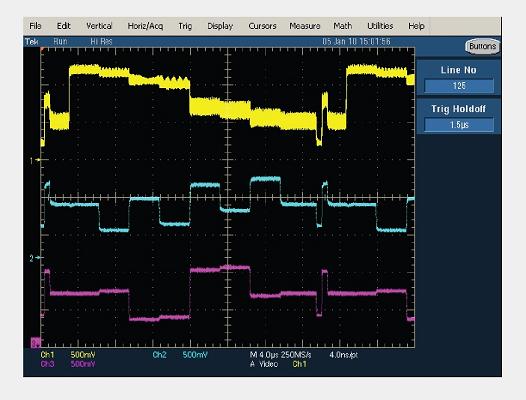

图6:FMS6346A 视频滤波驱动器驱动25pF 的负载。

图7:FMS6346A 驱动 47pF 的电容性负载。

那么,考虑到了电路布局对性能的所有可能的影响,设计人员可以做些什么来确保版图避免振荡、失真和总体信号质量低下呢?下面的基本版图和旁路电容设计指南“设计规则13条”可能颇有裨益:

1) RTM (仔细阅读产品手册)。放大器的数据手册一般都会给出它的最小稳定增益要求。该指标至关重要,如果放大器的工作增益小于推荐的最小稳定增益,就可能产生振荡。

2)采用一个接地平面。这是为元件提供低感性接地连接的最好方法。

3) 去掉放大器下面和周围的接地平面,去掉敏感引脚附近的接地平面。去掉高速放大器输入输出引脚附近的接地平面,可以减少杂散电容。同样,去掉放大器下面和周围的接地平面也很有帮助。

4) 采用表面贴装元件。这类元件的引脚电感很小。

5) 尽可能缩短引脚长度。 缩短引脚长度可以减少放大器反相输入端的串联电感。

6) 避免使用插槽。避免使用插槽,或者最多使用嵌入式插槽 (flush-mount),以减少电感。

7采用推荐的反馈电阻值。在使用电流反馈放大器时,这一点十分重要。

8) 不要在放大器的直接反馈回路中使用非线性元件 (如电容器) 。

9) 采用一个反馈电阻来实现单位增益配置。而不要使用标准的电压跟随(voltage-follower)电路。

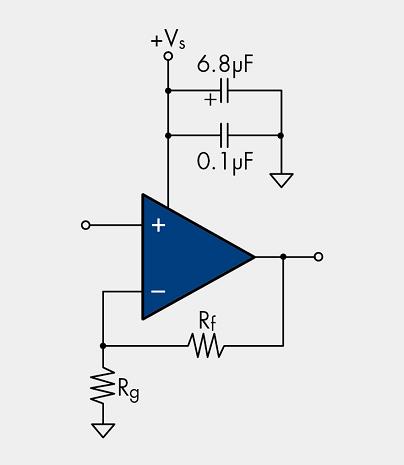

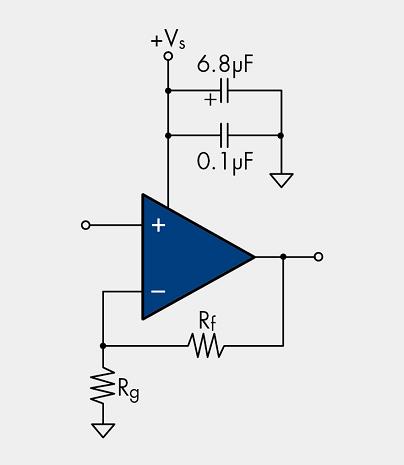

10) 使用旁路电容。在每个电源上增加一个旁路电容有助于降低电源引脚处的回流电流路径阻抗,提高电源噪声抑制能力,并对电源走线进行高频过滤。大多数厂商都推荐使用6.8uF钽电容和0.1uF陶瓷电容。为获得最佳性能,应该按照以下规则放置电容:6.8uF电容距电源引脚不超过0.75英寸,0.1uF电容距电源引脚不超过0.1英寸。当两者的距离增加时,由于走线电感增加,电容的滤波效果下降。不过,这也需要与失真考虑事项进行权衡,因为实验结果显示,该距离延长一点点会改善失真性能。

11) 调整旁路电容,减小失真。当单个运算放大器因接地电流路径而产生失真时,可调整旁路元件,对接地电流进行调节,使其远离输入元件。这十分简单,只需调整旁路电容,使它的接地连接远离输入即可。

12)对于视频滤波器,使串联端接电阻靠近输出引脚放置。这样做可以把寄生电容对滤波器输出驱动器的影响减至最小,从而避免输出端出现振荡。

13) 输入耦合电容和端接电阻靠近输入引脚放置,以获得最佳信号完整性。电路板布局对系统性能的影响非常大,因此,在版图设计阶段,应该谨慎监测,避免失误。

图8:一个单电源放大器示例 (如果使用双电源放大器,则只需在其它电源上增加相同的旁路电容即可) 。

在任何一个设计人员的工具箱里,集成电路放大器都是最基本的构件模块之一,它也是目前市面上最全能的产品之一。放大器具有多项功能,比如驱动ADC,驱动多个视频负载,作为视频或其他类型滤波器而工作,驱动高速仪器信号等等。它们还可以作为振荡器。不过,实际中这种方案存在一些问题。因为放大器应该只在设计人员需要的时候才振荡,而如果电路板设计不正确,放大器却会自行其是,随意振荡。那么,设计人员应该如何避免这种有害的振荡呢?试回忆一下我们以前在电子课程里学过的知识,即振荡与电容、电感和反馈相关。因此,关键在于精心设计电路板,减少或消除任何无关的电容性和电感性反馈路径。对于较高速的放大器(大于50MHz)而言,这尤其重要。

电路板、负载(尤其是电容性负载)和/或版图设计,都会引入无形的电容和电感。此外,流入电路板各处旁路电容的电流可能产生不同的路径,从而导致失真。因此,有些号称减少失真的技术其实是适得其反,与避免振荡的设计规则背道而驰。那么,在进行放大器或视频滤波器的版图设计时,为了保持全局平衡,减少失真和振荡,需要考虑到哪些事项呢?

首先我们来看看振荡器,在利用放大器直接驱动电容性负载时,负载会与放大器的输出阻抗会产生相位滞后,而相位滞后将导致脉冲尖峰或振荡。有些放大器能够直接驱动电容性负载,但有些放大器则需要在放大器的输出端增加一个小串联电阻(Rs)来提高放大器的稳定性和建立时间(settling time)性能。

图1:在输出端增加Rs提高稳定性。

图2给出了驱动传输电缆(如同轴电缆)的典型电路配置图。电阻Rs和RL应该等于电缆的特征阻抗(Zo),而电容C应该可被用来在更大的频率范围对电缆进行匹配,以对随频率提高而增加的放大器输出阻抗进行补偿。

图2:驱动电缆或传输线的典型电路图。

高频放大器很容易受电路布局所致失真的影响,即使是低频放大器(比如音频放大器),也具有非常严格的失真要求。总谐波失真(THD)是音频质量的主要指标,因此,减少版图引起的失真十分关键。

失真的一个重要原因是PCB中的接地电流效应。这种效应来自于流入每个电源和各电源旁路电容的电流,该电流与路径的电导率成比例。各个路径都存在不同的传导性,从而导致失真。因为即使PCB本身的材料是线性的,电路板的行为也会表现出“空间非线性”特性。这是因为旁路电容分布在电路板的不同位置,导致接地电流沿不同的路径流入各个旁路电容。路径不同导致接地电流流经的接地电阻输入一端的电压受到影响,而另一端则不会。结果是输入信号电压被不均衡地调整,导致非线性的产生。在这种情况下,如果一个极性被调节,而另一个却没有,就会造成二次谐波失真。换一句话说,如果只有正弦波的一个极性被调节,结果将不再是正弦波,这种失真的影响是显而易见的。为了避免失真,设计人员可以使用共有接地点并在输出端采用接地旁路电容。

高频电路板版图设计的主要规则是使高频旁路电容尽可能靠近封装的电源引脚。不过,经验证明,稍微延长高频旁路电容的连接走线可以提高平坦度和差分增益,从而减少失真。设计规则当然有益,而设计人员的实践经验也十分有用,可以确保规则与实际的一致性。

在电路板上设计视频滤波驱动器时,很重要的一点是,应该把输入耦合电容和端接电阻靠近输入引脚放置,以获得最佳信号完整性。图3所示为视频滤波器/驱动器的一种典型AC耦合输入配置。在这种配置中,采用0.1uF陶瓷电容来对输入信号进行AC耦合。如果输入信号不低于接地电位,钳位电路不激活;但若输入信号低于接地电位,则钳位电路会把同步端最低电压设置为恰好低于接地电位。钳位电路设置的输入电平,结合内部DC偏移量,将使输出信号保持在可接受的范围之内,大约在250mV左右。这种钳位特性还允许参考电平为地的DAC输出直接驱动直流耦合输入。

。

为了获得最高的输出信号质量,串联端接电阻必须尽可能靠近器件的输出引脚放置。这将大大减少寄生电容和寄生电感对驱动器输出的影响。从器件引脚到串联端接电阻的距离不应该超过0.5英寸(见图4)。图5是作为多媒体设备中作为输出驱动器的视频滤波器/驱动器的典型原理示意图。在图5所示的情况下,多媒体设备的复合视频信号端子接多媒体设备,S视频输出端子开通。在这时,让串联端接电阻靠近器件的输出引脚非常关键,可以把寄生电容对滤波器输出驱动器的影响降至最小,从而避免输出端出现振荡。图6所示为飞兆半导体的FMS6346A视频滤波驱动器驱动25pF 的负载,图7所示为FMS6346A驱动47pF的电容性负载。这表明,电容越小,性能越好。

图4:器件引脚到串联端接电阻的距离不应该超过0.5英寸。

图5:FMS6346A 视频滤波器输出到 S-视频。

图6:FMS6346A 视频滤波驱动器驱动25pF 的负载。

图7:FMS6346A 驱动 47pF 的电容性负载。

那么,考虑到了电路布局对性能的所有可能的影响,设计人员可以做些什么来确保版图避免振荡、失真和总体信号质量低下呢?下面的基本版图和旁路电容设计指南“设计规则13条”可能颇有裨益:

1) RTM (仔细阅读产品手册)。放大器的数据手册一般都会给出它的最小稳定增益要求。该指标至关重要,如果放大器的工作增益小于推荐的最小稳定增益,就可能产生振荡。

2)采用一个接地平面。这是为元件提供低感性接地连接的最好方法。

3) 去掉放大器下面和周围的接地平面,去掉敏感引脚附近的接地平面。去掉高速放大器输入输出引脚附近的接地平面,可以减少杂散电容。同样,去掉放大器下面和周围的接地平面也很有帮助。

4) 采用表面贴装元件。这类元件的引脚电感很小。

5) 尽可能缩短引脚长度。 缩短引脚长度可以减少放大器反相输入端的串联电感。

6) 避免使用插槽。避免使用插槽,或者最多使用嵌入式插槽 (flush-mount),以减少电感。

7采用推荐的反馈电阻值。在使用电流反馈放大器时,这一点十分重要。

8) 不要在放大器的直接反馈回路中使用非线性元件 (如电容器) 。

9) 采用一个反馈电阻来实现单位增益配置。而不要使用标准的电压跟随(voltage-follower)电路。

10) 使用旁路电容。在每个电源上增加一个旁路电容有助于降低电源引脚处的回流电流路径阻抗,提高电源噪声抑制能力,并对电源走线进行高频过滤。大多数厂商都推荐使用6.8uF钽电容和0.1uF陶瓷电容。为获得最佳性能,应该按照以下规则放置电容:6.8uF电容距电源引脚不超过0.75英寸,0.1uF电容距电源引脚不超过0.1英寸。当两者的距离增加时,由于走线电感增加,电容的滤波效果下降。不过,这也需要与失真考虑事项进行权衡,因为实验结果显示,该距离延长一点点会改善失真性能。

11) 调整旁路电容,减小失真。当单个运算放大器因接地电流路径而产生失真时,可调整旁路元件,对接地电流进行调节,使其远离输入元件。这十分简单,只需调整旁路电容,使它的接地连接远离输入即可。

12)对于视频滤波器,使串联端接电阻靠近输出引脚放置。这样做可以把寄生电容对滤波器输出驱动器的影响减至最小,从而避免输出端出现振荡。

13) 输入耦合电容和端接电阻靠近输入引脚放置,以获得最佳信号完整性。电路板布局对系统性能的影响非常大,因此,在版图设计阶段,应该谨慎监测,避免失误。

图8:一个单电源放大器示例 (如果使用双电源放大器,则只需在其它电源上增加相同的旁路电容即可) 。

举报

举报

举报

举报