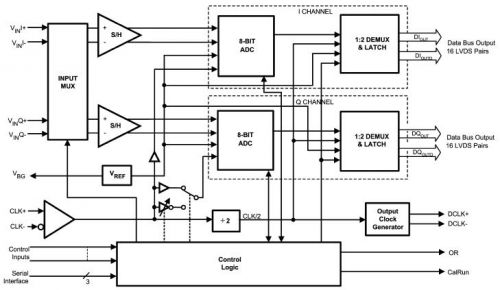

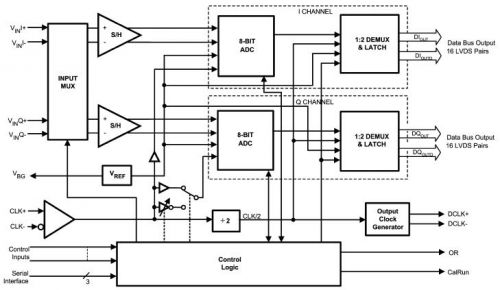

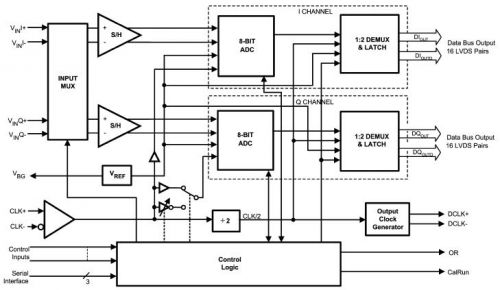

这次有幸调试了国半公司一款双通道,8位,1.5G(单通道最高3G)采样率的超高速ADC,芯片型号ADC08D1500。与普通高速芯片不同的是这款芯片的输出拥有DDR模式。结构框图如下

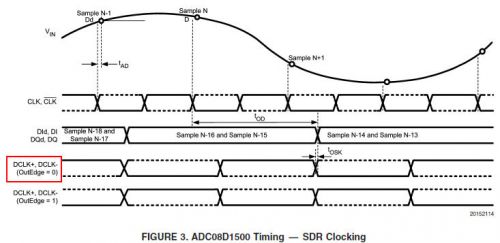

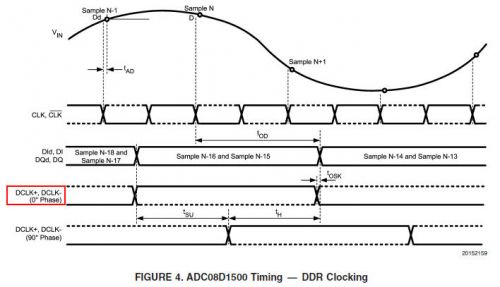

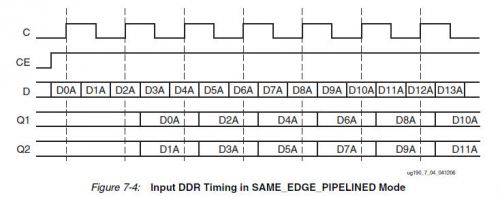

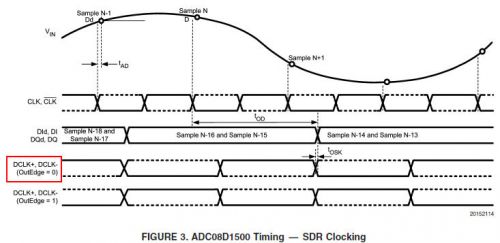

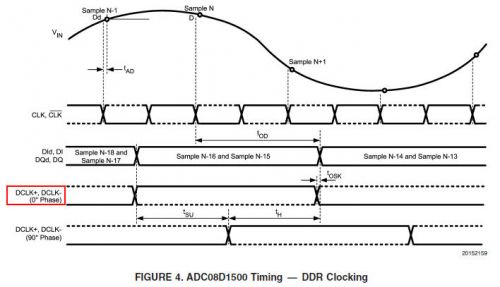

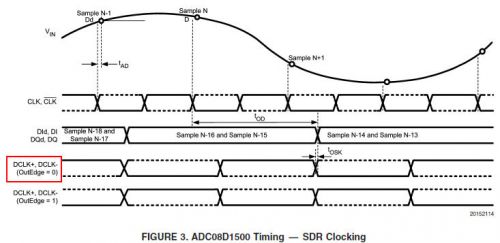

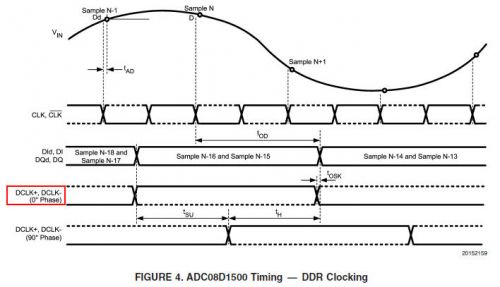

两个1:2DEMUX分别用于I、Q两路。按采样时钟2分频的速率,每个通道分2路按Dx、DxD输出,共4路输出。SDR模式和DDR模式唯一的区别在于上图的Output Clock Generator模块,SDR工作在时钟单边沿采样输出模式,DDR则是时钟双边采样输出模式。因此,DDR的输出时钟是采样时钟的4分频,这个时钟在FPGA内部可使用IDDR逻辑资源匹配接收。SDR和DDR模式的时序图如下

至于该芯片的配置,模拟输入的处理以及其他走线相关注意,这在datasheet里都有相当详细的描述,这里就不多说了。我主要想总结下调试这种AD的几点经验。这些经验对高速,高精度AD的调试一样适用。

一个项目中,尤其是涉及到信号处理的项目,AD的调试都是一个关键环节。如何对AD进行测试,如何确定AD调试完成,在FPGA中如何对不同输出模式的数据进行处理等。这一些系列的问题不光是写写代码这么简单,更重要的是要会分析数据。硬件设计上还要充分考虑到AD内外时钟的设计,以及LVPECL、LVDS等差分线耦合方式的设计等。这其中任何一项内容都可以拿来大书特书。我想这也是为什么在研究生电子设计中,专家最关心的是AD部分。针对这款AD芯片在调试过程中遇到的问题,总结下我的解决方法,以及数据分析时用到的一些方法。

经验1:分析AD输出数据准确与非,最简单的方式就是无信号输入时的噪声数据是否准确,这可以确定AD有效位数据的准确性。采用二进制反码观察最方便,例如8位输出,噪声数据只会在127-128之间变化。

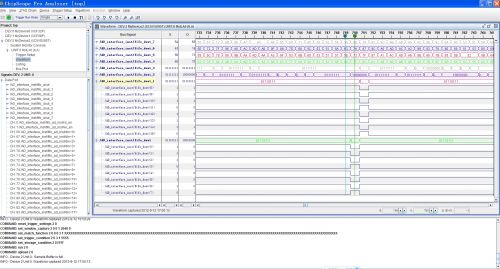

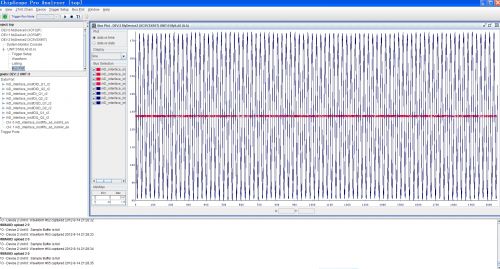

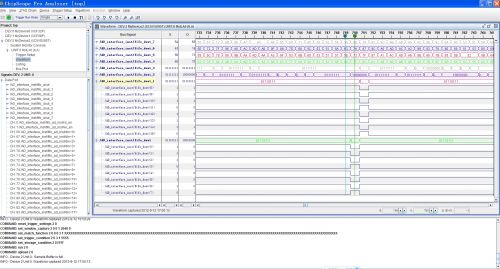

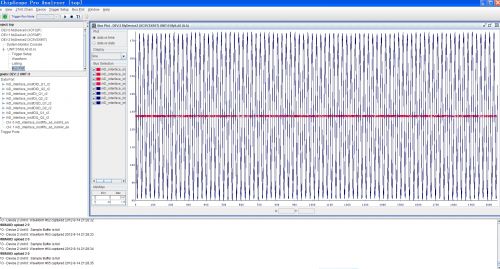

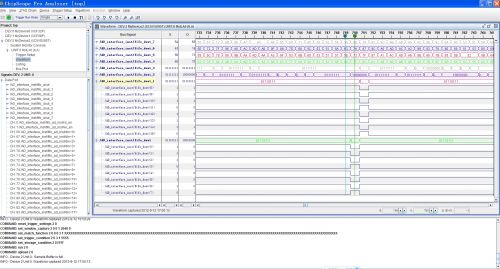

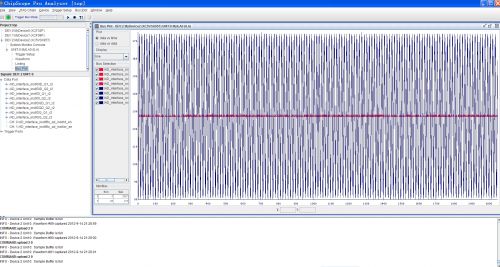

错误例子:如下图(看不清点击网页查看图片)

上4路是FPGA的IDDR逻辑同步DDR时钟输出的4路I通道数据,下4路则是Q路数据。因为我只保存了查找错误时的数据图片,实际中只要看噪声的Bus波形就可以确认噪声电平正确与否。该图中I路输出为正弦信号采样值,Q路则是噪声值。容易看到,Q路中灰蓝两路的噪声值正确均为127-128,而红绿两路噪声的低4位有误码。

错误排查:因为这里已经确定错误通路和通路的位数,按照数据流的反方向检查,首先检查FPGA接收代码,从涉及到该位的FIFO → IDDR → IBUFDS ,确定无误后再到硬件连接,主要是检查该路的差分对是否接反,以及AD并行数据差分对的走线长度是否出现较大误差。实时也是如此,底板和采集板DQ[3]差分对的连接P/N接反了,才造成该路的逻辑与正确值反向。

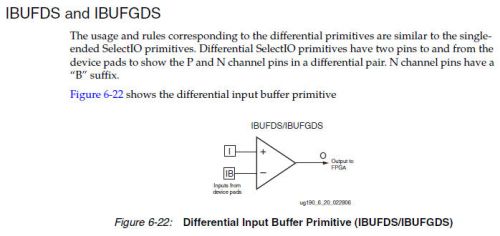

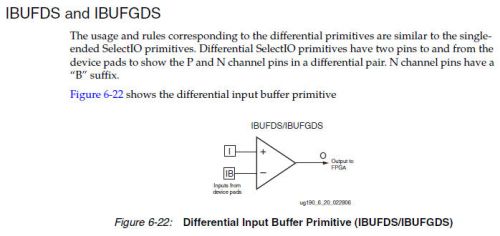

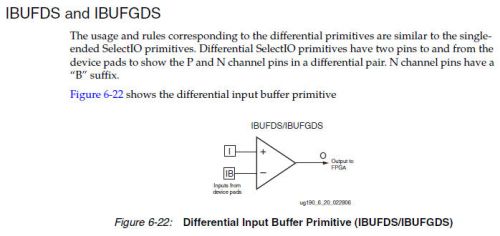

错误修改:这种硬件错误修改ucf是不行的,map不过。因为FPGA管脚和硬件是一一对应的,修改ucf无济于事。在IBUFDS中将差分对对调,这也是不行的,因为IBUFDS的输入又是与FPGA管脚的P/N一一对应。官方说明截图如下。因此,迫于无奈,只能在后级缓存总将逻辑取反再送进fifo。

经验2:输入信号频率比AD采样频率小100倍以上的信号,观察AD输出数据频率的稳定性,也即正弦信号疏密的变化,这可以确定AD采样时钟的稳定性。针对高速差分时钟,在电路板中如果时钟信号线处理不当或者时钟驱动器与接收器之间的耦合方式不对,很容易造成终端接收的时钟不稳定。耦合方式一定要看选用哪个公司时钟驱动芯片的datasheet,以及该公司提供的时钟耦合方式专用说明文档。

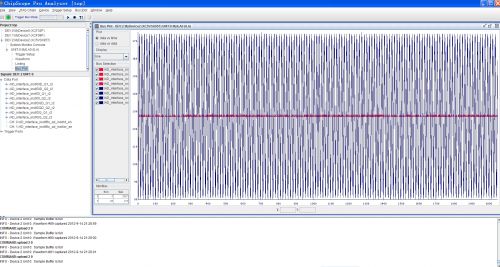

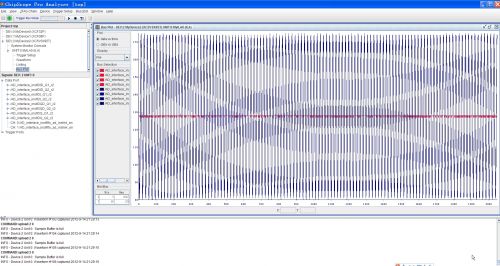

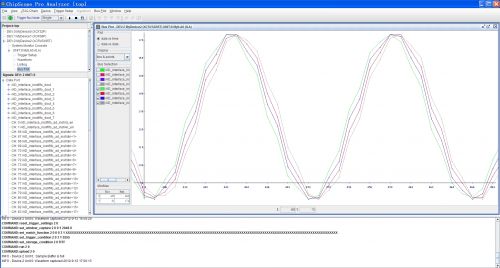

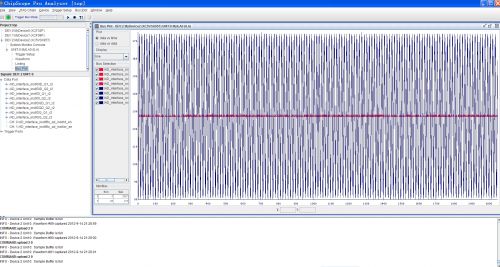

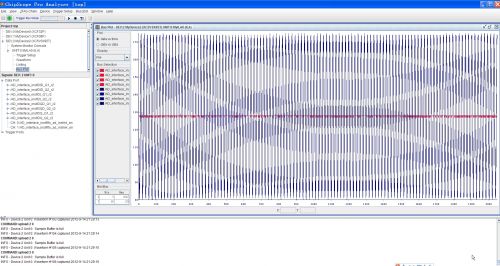

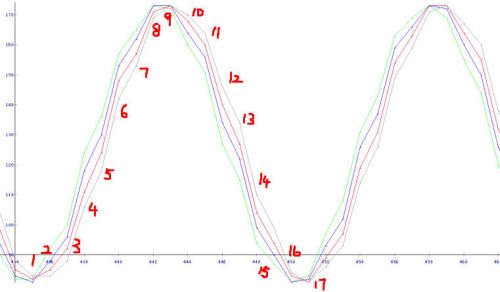

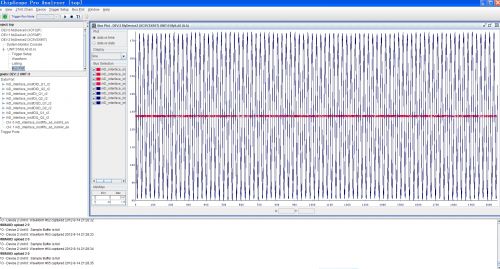

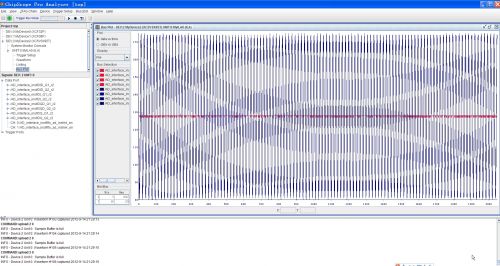

错误例子:解决了误码问题后,输入频率为10M的单频信号,频率为1G的采样时钟由FPGA控制的MAX3674-PLL芯片提供,该时钟经过时钟选择驱动器MC100LVEP14到采集板,连续观察FPGA内部采集到的数据信息。如下图

可见,连续抓出的三幅图片中,正弦信号的频率在变化。正常情况应该是波形基本不变,或者变化非常细小。这主要是因为给AD的采样时钟不稳定造成的,原因如下:1.PLL时钟配置不正确使其无法锁定频率;2.PLL到Clock Driver的时钟耦合不当;3.Clock Driver到AD的耦合不当;这个问题以后积累到一定程度再展开讨论,现在暂且不谈。主要是硬件设计之初就要充分考虑到各种耦合方式的兼容,不然后续调试将非常困难。

经验3:通过正弦信号的递增、递减以及缓存通道的先后顺序判别信号的先后,进而利用FPGA在线逻辑分析计算出信号的周期,以及单周期内的采样点数,进一步验证AD对输入信号采样率的准确性。

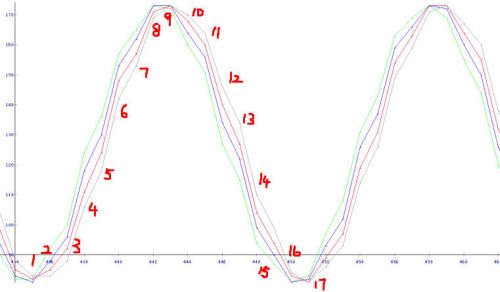

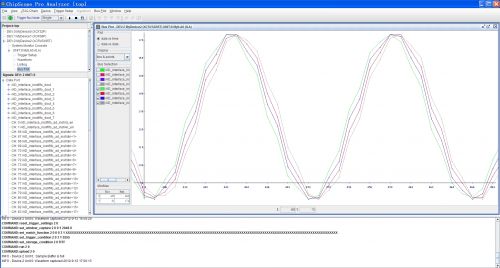

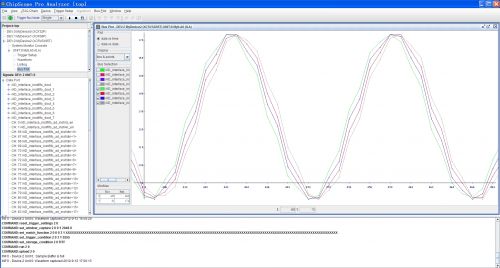

实例计算分析:频率为10M的单频信号,采样时钟设置为700M。以Chipscope为例,采用单窗口,2048存储深度采集AD的I路DDR输出的正弦信号单周期放大图如下。(绿、红、篮、灰→DI_Q2、DI_Q1、DId_Q2、DId_Q1,其中Q1表示时钟上边沿,Q2表示时钟下边沿)

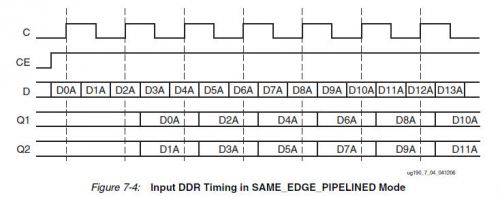

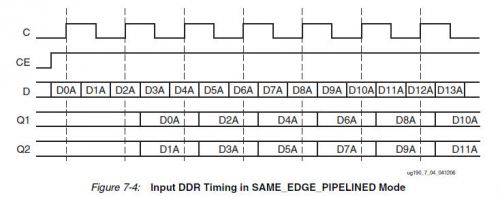

在FPGA中,利用IDDR逻辑采样时钟4分频同步4通道输出数据。简单的解释就是AD在采样频率为F条件下,将I路输入的模拟信号转成频率为F/2,两路DI,DId交替输出的数字信号,进入FPGA后,再将DI,DId转成频率为F/4,四路DI_Q1(红),DId_Q1(灰),DI_Q2(篮),DId_Q2(绿)SAME_EDGE_PIPELINED输出数据。IDDR同边沿流水输出的时序同如下:

根据波形图正弦波形的先后顺序,I通道的先后顺序依次是灰(DId_Q1)-》红(DI_Q1)-》蓝(DI_Q2)-》绿(DId_Q2),该4通道的时间间隔即为AD采样间隔。如下图所示,记录单周期的采样点数:17×4=68约等于70这便是与输入的10M模拟信号在700M采样时钟的数字信号。

至于内部PLL+DCM的配置主要是注意PLL和DCM中一些开关特性,别让内部信号超过了设定范围就行了。

高速信号的处理更多的还是利用FPGA的固有资源去做,归根到底就是看官方资料,一字一句理清楚接口上就不会有太大的问题。并不喜欢像很多人把例如PCIe、RapidI/O这些高速传输协议说的那么悬乎,其实就是复杂一点,砸钱砸的多一点而已。更喜欢FPGA在信号处理上的应用,可以很直接的把自己设计的算法在上面实现,仿真也很准确实用。至于FPGA的另一大应用领域片上系统,外界吹的多么有优势,真正用起来还是不容易的,感觉还是不够完善。在FPGA的三大应用领域中,还是信号处理发展前景最大,真正做到理论与实践并重的一个领域,一点小小感悟。

这次有幸调试了国半公司一款双通道,8位,1.5G(单通道最高3G)采样率的超高速ADC,芯片型号ADC08D1500。与普通高速芯片不同的是这款芯片的输出拥有DDR模式。结构框图如下

两个1:2DEMUX分别用于I、Q两路。按采样时钟2分频的速率,每个通道分2路按Dx、DxD输出,共4路输出。SDR模式和DDR模式唯一的区别在于上图的Output Clock Generator模块,SDR工作在时钟单边沿采样输出模式,DDR则是时钟双边采样输出模式。因此,DDR的输出时钟是采样时钟的4分频,这个时钟在FPGA内部可使用IDDR逻辑资源匹配接收。SDR和DDR模式的时序图如下

至于该芯片的配置,模拟输入的处理以及其他走线相关注意,这在datasheet里都有相当详细的描述,这里就不多说了。我主要想总结下调试这种AD的几点经验。这些经验对高速,高精度AD的调试一样适用。

一个项目中,尤其是涉及到信号处理的项目,AD的调试都是一个关键环节。如何对AD进行测试,如何确定AD调试完成,在FPGA中如何对不同输出模式的数据进行处理等。这一些系列的问题不光是写写代码这么简单,更重要的是要会分析数据。硬件设计上还要充分考虑到AD内外时钟的设计,以及LVPECL、LVDS等差分线耦合方式的设计等。这其中任何一项内容都可以拿来大书特书。我想这也是为什么在研究生电子设计中,专家最关心的是AD部分。针对这款AD芯片在调试过程中遇到的问题,总结下我的解决方法,以及数据分析时用到的一些方法。

经验1:分析AD输出数据准确与非,最简单的方式就是无信号输入时的噪声数据是否准确,这可以确定AD有效位数据的准确性。采用二进制反码观察最方便,例如8位输出,噪声数据只会在127-128之间变化。

错误例子:如下图(看不清点击网页查看图片)

上4路是FPGA的IDDR逻辑同步DDR时钟输出的4路I通道数据,下4路则是Q路数据。因为我只保存了查找错误时的数据图片,实际中只要看噪声的Bus波形就可以确认噪声电平正确与否。该图中I路输出为正弦信号采样值,Q路则是噪声值。容易看到,Q路中灰蓝两路的噪声值正确均为127-128,而红绿两路噪声的低4位有误码。

错误排查:因为这里已经确定错误通路和通路的位数,按照数据流的反方向检查,首先检查FPGA接收代码,从涉及到该位的FIFO → IDDR → IBUFDS ,确定无误后再到硬件连接,主要是检查该路的差分对是否接反,以及AD并行数据差分对的走线长度是否出现较大误差。实时也是如此,底板和采集板DQ[3]差分对的连接P/N接反了,才造成该路的逻辑与正确值反向。

错误修改:这种硬件错误修改ucf是不行的,map不过。因为FPGA管脚和硬件是一一对应的,修改ucf无济于事。在IBUFDS中将差分对对调,这也是不行的,因为IBUFDS的输入又是与FPGA管脚的P/N一一对应。官方说明截图如下。因此,迫于无奈,只能在后级缓存总将逻辑取反再送进fifo。

经验2:输入信号频率比AD采样频率小100倍以上的信号,观察AD输出数据频率的稳定性,也即正弦信号疏密的变化,这可以确定AD采样时钟的稳定性。针对高速差分时钟,在电路板中如果时钟信号线处理不当或者时钟驱动器与接收器之间的耦合方式不对,很容易造成终端接收的时钟不稳定。耦合方式一定要看选用哪个公司时钟驱动芯片的datasheet,以及该公司提供的时钟耦合方式专用说明文档。

错误例子:解决了误码问题后,输入频率为10M的单频信号,频率为1G的采样时钟由FPGA控制的MAX3674-PLL芯片提供,该时钟经过时钟选择驱动器MC100LVEP14到采集板,连续观察FPGA内部采集到的数据信息。如下图

可见,连续抓出的三幅图片中,正弦信号的频率在变化。正常情况应该是波形基本不变,或者变化非常细小。这主要是因为给AD的采样时钟不稳定造成的,原因如下:1.PLL时钟配置不正确使其无法锁定频率;2.PLL到Clock Driver的时钟耦合不当;3.Clock Driver到AD的耦合不当;这个问题以后积累到一定程度再展开讨论,现在暂且不谈。主要是硬件设计之初就要充分考虑到各种耦合方式的兼容,不然后续调试将非常困难。

经验3:通过正弦信号的递增、递减以及缓存通道的先后顺序判别信号的先后,进而利用FPGA在线逻辑分析计算出信号的周期,以及单周期内的采样点数,进一步验证AD对输入信号采样率的准确性。

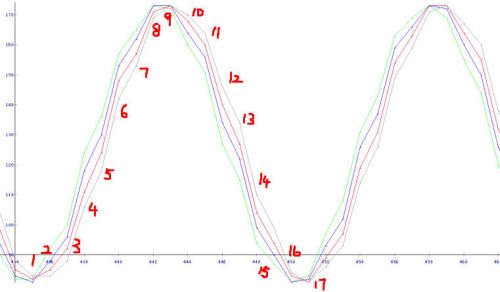

实例计算分析:频率为10M的单频信号,采样时钟设置为700M。以Chipscope为例,采用单窗口,2048存储深度采集AD的I路DDR输出的正弦信号单周期放大图如下。(绿、红、篮、灰→DI_Q2、DI_Q1、DId_Q2、DId_Q1,其中Q1表示时钟上边沿,Q2表示时钟下边沿)

在FPGA中,利用IDDR逻辑采样时钟4分频同步4通道输出数据。简单的解释就是AD在采样频率为F条件下,将I路输入的模拟信号转成频率为F/2,两路DI,DId交替输出的数字信号,进入FPGA后,再将DI,DId转成频率为F/4,四路DI_Q1(红),DId_Q1(灰),DI_Q2(篮),DId_Q2(绿)SAME_EDGE_PIPELINED输出数据。IDDR同边沿流水输出的时序同如下:

根据波形图正弦波形的先后顺序,I通道的先后顺序依次是灰(DId_Q1)-》红(DI_Q1)-》蓝(DI_Q2)-》绿(DId_Q2),该4通道的时间间隔即为AD采样间隔。如下图所示,记录单周期的采样点数:17×4=68约等于70这便是与输入的10M模拟信号在700M采样时钟的数字信号。

至于内部PLL+DCM的配置主要是注意PLL和DCM中一些开关特性,别让内部信号超过了设定范围就行了。

高速信号的处理更多的还是利用FPGA的固有资源去做,归根到底就是看官方资料,一字一句理清楚接口上就不会有太大的问题。并不喜欢像很多人把例如PCIe、RapidI/O这些高速传输协议说的那么悬乎,其实就是复杂一点,砸钱砸的多一点而已。更喜欢FPGA在信号处理上的应用,可以很直接的把自己设计的算法在上面实现,仿真也很准确实用。至于FPGA的另一大应用领域片上系统,外界吹的多么有优势,真正用起来还是不容易的,感觉还是不够完善。在FPGA的三大应用领域中,还是信号处理发展前景最大,真正做到理论与实践并重的一个领域,一点小小感悟。

举报

举报

举报

举报