1 引言

随着微电子技术的迅速发展,DDS技术得到了广泛的应用,市场上有很多高性能多功能的DDS专用器件,但其工作方式和控制方式固定,一般用户很难按自己的要求获得相应的波形。同时任意波的输入方式目前都只限于时域,无法实现电子、通信等领域的科研与教学中所需频域参数定义的波形。本文介绍一种基于DDS的可视化信号发生器,它高精度地生成双通道±8 V、0.01 Hz~10 MHz正弦波等常规波形。还可产生数码流、调制信号、随机噪声、扫频信号及时域或频域自定义波等信号,信号参数均步进在线可调,由USB1.1与Delphi7.0完成与PC连机时的接口及图形操作界面设计,TFT实现单机工作时的图形操作界面,实验表明该设计是行之有效的。

2 系统设计

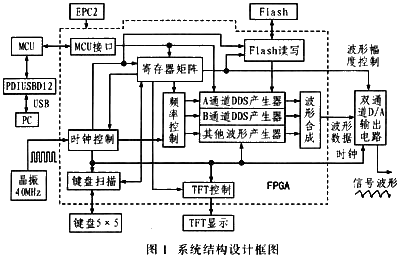

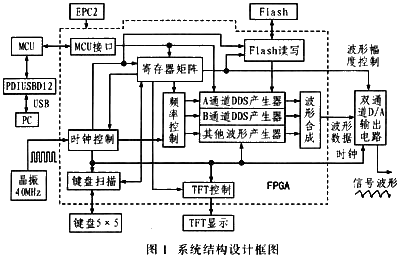

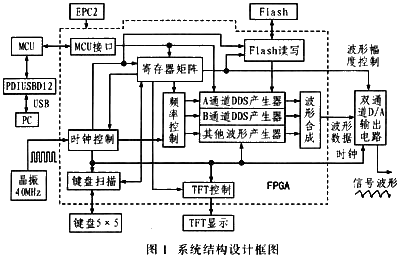

系统结构框图如图1所示,其中用Delphi来开发图形上位机软件;PDIUSBD12为USB控制器,MCU实现系统智能控制和数值运算,FPGA为系统数字载体,内建DDS、MCU接口、时钟控制、Flash读写、键盘扫描和TFT控制等模块。设计双路D/A输出通道,通过调节DAC参考电压提高小信号幅度分辨率,系统既可由上位机软件控制实现信号源功能,也可通过触摸按键和TFT图形液晶显示器智能实现便携式任意源功能。

[/table]

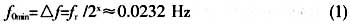

设计中取系统时标信号频率为fr=100 MHz,输出信号每一周期由N个取样点构成,取样周期为Tr=(1/fr),则输出信号的频率为fo=fr/N,设合成信号初相为ψ0,相位累加器位数为x=32,存储器位数为y=10,则

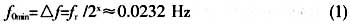

其中,f0min为合成器最低输出频率,△f为频率分辨率,设输出频率控制字为k,则:

nψ=ψ02x/2πk为初相量化值,最小相移、占空比的最小值和分辨率分别为:

当x-y>4时,正弦输出相位截断噪声的信噪比SNRP=6.02y-3.992=68.24dB[1,3],可见相位截断后仍有较高的信躁比,幅度噪声的信噪比SNRE=6.02y+20lgr,其中r为输出波形与满刻度的峰-峰值之比,取r=1,则SNRE=72.2 dB[3,4]。

3 FPGA与分段时标设计

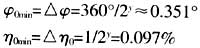

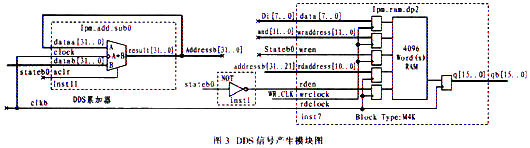

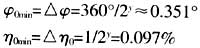

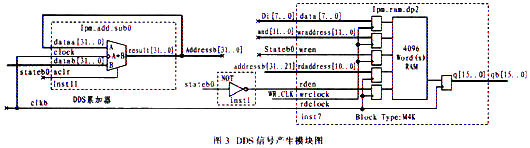

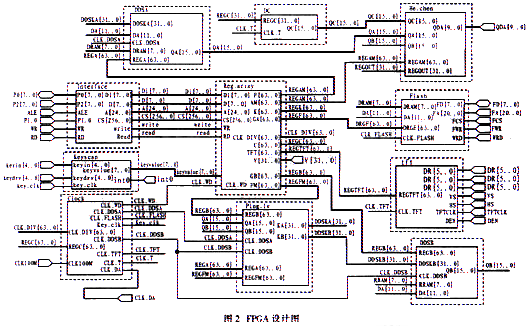

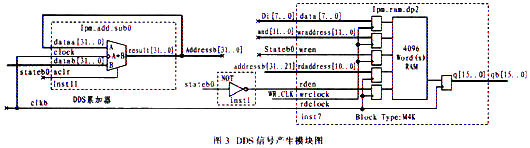

FPGA设计原理如图2所示。DDSA、DDSB均是双通道DDS产生模块,内部由32位累加器和波形存储器RAM组成,累加器在累加时钟的控制下对频率控制字k进行累加,其结果作为波形存储器RAM的地址来读出RAM中波形数值。波形存储器RAM为双口RAM,既可在读信号、读地址的配合下进行RAM的读操作。也可在写信号、写地址和数据输入信号的配合下进行写操作,更换波形数据见图3。双通道设计为互相调制提供了方便。波形存储器RAM为双口RAM,在进行波形切换时,由MCU控制FPGA启动Flash读写单元,以10 MHz的速度从外部的Flash中读取4 096个波形数据到双口RAM中。

[table][tr]

[/tr]

接口模块(interface)主要输出8位DB、24位AB、256个片选信号、读/写控制信号,寻址能力达16 MB。Reg_array是寄存器矩阵,实现MCU对FPGA及系统的控制.主要储存时钟分频系数CLK_DIV[63..0],双通道幅度控制字V[31..0]、Flash的地址、数据和控制信号REGF[63..0]等。Ping_lv是频率控制模块,完成调频、扫频、频率控制功能,输出DDS信号产生单元所需的频率控制字KA[31..0]和KB[31..0],由频率字选择模块、调频模块、扫频模块组成。

任意波形产生时,先将从计算机采集到的波形数据量化编码后通过USB下载到Flash存储器,从Flash中读取数据到双口RAM中。这样既能快速地产生任意波形.又能使任意波形在脱离计算机后还能继续使用。系统Flash容量为2 MB,分为32页,除了存储常规的6种波形外,还能储存26个任意波形。

DC可产生方波、数据流等其他波形,he.chen主要完成信号的合成功能,包括模拟调幅、随机信号、ASK、FSK等。Clcok时钟控制单元在CLK_DIV[63..0]和REGC[63..0]的控制下对外部40 MHz时钟进行倍频和分频,输出系统所需时钟。tft是TFT显示控制单元,采用查找表结构进行单色显示。输出直接接到TFT屏的三原色数据DR[5..0]、DG[5..0]、DB[5..0],和时序控制信号VS、HS、TFTCLK、REN等,实现波形菜单与图形界面显示。Keysan是键盘扫描单元,自建键盘扫描时序,输出行列矩阵式键盘行列扫描信号,能自动进行键值识别、键码锁存keyvalue[7..0],并产生中断信号int0。Flash控制模块采用NOR Flash方式,读操作与普通RAM一样,但写操作时要先擦除并输入命令后才能读写。为此设计给MCU提供与RAM一样的操作接口,同时在系统进行波形切换时.能自动地从外部Flash波形存储器中读取4 096个波形数据到DDS单元中.进行波形数据的改写。

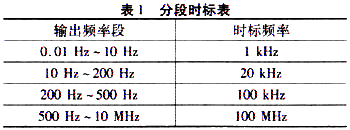

根据DDS原理。在较低的频率段,由式(2)可知频率控制字k减小,在对其进行量化时,势必加大了量化误差,故降低了信号的时域精度,

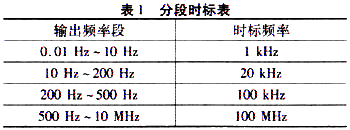

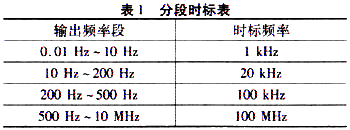

为此,在低频段可由式(1)通过减小fr来降低f0min,提高k以提高信号的时域精度,可以采用分频的方法,即在不同的频率段采用不同的时标时钟fr来解决这个问题,分段时标见表1。

[tr]

[/tr]

4 上位机界面、信号参数定义与接口

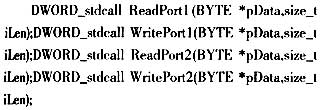

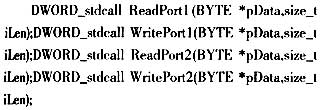

本设计采用USB1.1作为通信接口,针对由PDIUSBD12实现的USB接口,可以利用Philips公司提供的EasyD12库来编写PC机应用程序。EasyD12库包含3个文件,分别是EasyD12.lib、EasyD12.dll和EasyD12.h。库文件提供了4个可以调用的函数,用于完成对PDIUSBD12端点1、端点2的读写操作。这4个函数分别为:

采用上述4个函数可以简单地完成对PDIUS-BD12的读写操作。由于本设计中通用USB数据传输模块的主要作用是由控制界面向接口模块发送各种命令及波形数据,PC机对发送的时机是十分清楚的(通常在按键或菜单选项的响应函数中出现),所以命令及数据的可靠性及实时性能得到充分的保障。

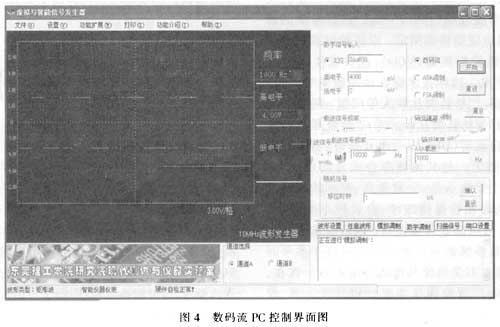

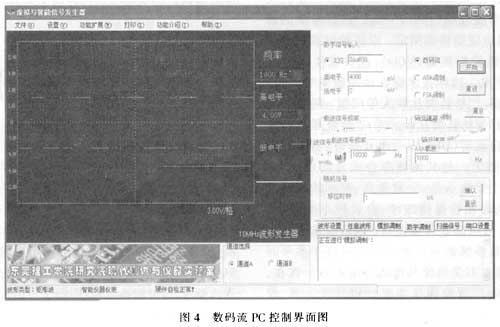

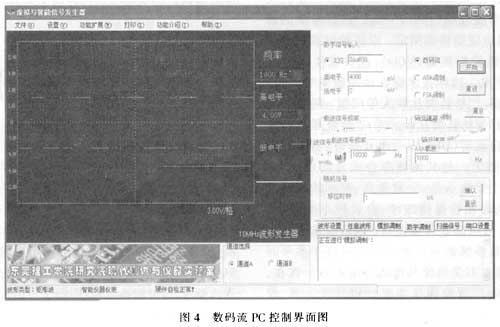

主控制界面由波形设置、任意波形、模拟调制、数字调制、扫描信号、端口设置等部分组成,利用Delphi7.0提供的强大控件对信号幅度、频率、占空比等参数实现实时控制,还有任意信号的手动制作和特殊波形(如抽样波形、正弦的谐波合成、可控数码流等)的采样。图4为数码流PC控制界面。

[tr]

[/tr]任意波形产生是用户在画图区用鼠标绘制任意形状的单值波形.把PixelFormat属性设置为pf8bit,信号幅度采集分辨率为10位,通过对画板上的波形扫描把黑色的像素点用数组记录该处坐标值,扫描后得到所需波形数据。

时域信号叠加产生是依据各种实际需要,对常规波形进行叠加。软件主要由波形构造、数据计算分析及控制组成。通过用户输入的公式及各常规波形的参数计算得出新的波形数据,然后根据数据进行描图。计算定义为时域波形数据的加、减、乘、除。

频域还原时域信号产生是采用谐波输入法。依据幅度谱和相位谱信息。利用反傅立叶变换实偶对称级数,还原为时域波形,经4 096个点数据采集,10位量化编码后得到所需波形数据。

5 研制结果与展望

研制的双通道“便携式DDS高精度信号发生器”样机采用40 MHz外部晶振,TFT选用彩色PT035TNO1,FPGA选用Altera-Cyclone系列EP1C6 T114-8。DAC选用10位ADI-AD9763,运算放大器选用ADI-AD8014,MCU 选用Philips-P89LV51RD2,Flash选用AM19LV160D。主要性能如下:

(1)主波形有正弦波、方波等,100μHz~10MHz,储存波形为100 Hz~100 kHz。分辨率为100μHz。幅度分辨率10 bit,(≤10 MHz)10 mV~18Vp-p(高阻),1 mV~10 Vp-p(50 Ω)。

(2)任意波形由计算机界面输入,具有时域与频域三种输入方式。

(3)调制特性:内调制,调制信号频率范围为100μHz~1 MHz,调制深度范围为1%~100%,数码流、码元速率可编程,调频时最大频偏为载波频率的50%。

(4)扫描特性:频率扫描扫描起终点及步进100μHz≤f≤10 MHz,幅度扫描扫描起终点及步进10mV≤V≤10 V,步进时间均为1 ms~20 s,线性扫描。向上或向下或来回扫描,自动控制方式。

(5)伪随机噪声:随机码元移位速率可调,可编程数码流:码元32位可编程输入,波特率1 kb/s~1000 kb/s,电平10mV~10 V。

实验表明:研制的样机功能多、操作方便、TFT与PC屏幕显示直观、具有独特的任意信号输入方式、性价比高,仪器还可设计对外部输入信号实时调制,直流分量应可控,由矢量分析仪产生的频谱图存储后转入信号发生器来重现时域波形的工作正在研究之中。

1 引言

随着微电子技术的迅速发展,DDS技术得到了广泛的应用,市场上有很多高性能多功能的DDS专用器件,但其工作方式和控制方式固定,一般用户很难按自己的要求获得相应的波形。同时任意波的输入方式目前都只限于时域,无法实现电子、通信等领域的科研与教学中所需频域参数定义的波形。本文介绍一种基于DDS的可视化信号发生器,它高精度地生成双通道±8 V、0.01 Hz~10 MHz正弦波等常规波形。还可产生数码流、调制信号、随机噪声、扫频信号及时域或频域自定义波等信号,信号参数均步进在线可调,由USB1.1与Delphi7.0完成与PC连机时的接口及图形操作界面设计,TFT实现单机工作时的图形操作界面,实验表明该设计是行之有效的。

2 系统设计

系统结构框图如图1所示,其中用Delphi来开发图形上位机软件;PDIUSBD12为USB控制器,MCU实现系统智能控制和数值运算,FPGA为系统数字载体,内建DDS、MCU接口、时钟控制、Flash读写、键盘扫描和TFT控制等模块。设计双路D/A输出通道,通过调节DAC参考电压提高小信号幅度分辨率,系统既可由上位机软件控制实现信号源功能,也可通过触摸按键和TFT图形液晶显示器智能实现便携式任意源功能。

[/table]

设计中取系统时标信号频率为fr=100 MHz,输出信号每一周期由N个取样点构成,取样周期为Tr=(1/fr),则输出信号的频率为fo=fr/N,设合成信号初相为ψ0,相位累加器位数为x=32,存储器位数为y=10,则

其中,f0min为合成器最低输出频率,△f为频率分辨率,设输出频率控制字为k,则:

nψ=ψ02x/2πk为初相量化值,最小相移、占空比的最小值和分辨率分别为:

当x-y>4时,正弦输出相位截断噪声的信噪比SNRP=6.02y-3.992=68.24dB[1,3],可见相位截断后仍有较高的信躁比,幅度噪声的信噪比SNRE=6.02y+20lgr,其中r为输出波形与满刻度的峰-峰值之比,取r=1,则SNRE=72.2 dB[3,4]。

3 FPGA与分段时标设计

FPGA设计原理如图2所示。DDSA、DDSB均是双通道DDS产生模块,内部由32位累加器和波形存储器RAM组成,累加器在累加时钟的控制下对频率控制字k进行累加,其结果作为波形存储器RAM的地址来读出RAM中波形数值。波形存储器RAM为双口RAM,既可在读信号、读地址的配合下进行RAM的读操作。也可在写信号、写地址和数据输入信号的配合下进行写操作,更换波形数据见图3。双通道设计为互相调制提供了方便。波形存储器RAM为双口RAM,在进行波形切换时,由MCU控制FPGA启动Flash读写单元,以10 MHz的速度从外部的Flash中读取4 096个波形数据到双口RAM中。

[table][tr]

[/tr]

接口模块(interface)主要输出8位DB、24位AB、256个片选信号、读/写控制信号,寻址能力达16 MB。Reg_array是寄存器矩阵,实现MCU对FPGA及系统的控制.主要储存时钟分频系数CLK_DIV[63..0],双通道幅度控制字V[31..0]、Flash的地址、数据和控制信号REGF[63..0]等。Ping_lv是频率控制模块,完成调频、扫频、频率控制功能,输出DDS信号产生单元所需的频率控制字KA[31..0]和KB[31..0],由频率字选择模块、调频模块、扫频模块组成。

任意波形产生时,先将从计算机采集到的波形数据量化编码后通过USB下载到Flash存储器,从Flash中读取数据到双口RAM中。这样既能快速地产生任意波形.又能使任意波形在脱离计算机后还能继续使用。系统Flash容量为2 MB,分为32页,除了存储常规的6种波形外,还能储存26个任意波形。

DC可产生方波、数据流等其他波形,he.chen主要完成信号的合成功能,包括模拟调幅、随机信号、ASK、FSK等。Clcok时钟控制单元在CLK_DIV[63..0]和REGC[63..0]的控制下对外部40 MHz时钟进行倍频和分频,输出系统所需时钟。tft是TFT显示控制单元,采用查找表结构进行单色显示。输出直接接到TFT屏的三原色数据DR[5..0]、DG[5..0]、DB[5..0],和时序控制信号VS、HS、TFTCLK、REN等,实现波形菜单与图形界面显示。Keysan是键盘扫描单元,自建键盘扫描时序,输出行列矩阵式键盘行列扫描信号,能自动进行键值识别、键码锁存keyvalue[7..0],并产生中断信号int0。Flash控制模块采用NOR Flash方式,读操作与普通RAM一样,但写操作时要先擦除并输入命令后才能读写。为此设计给MCU提供与RAM一样的操作接口,同时在系统进行波形切换时.能自动地从外部Flash波形存储器中读取4 096个波形数据到DDS单元中.进行波形数据的改写。

根据DDS原理。在较低的频率段,由式(2)可知频率控制字k减小,在对其进行量化时,势必加大了量化误差,故降低了信号的时域精度,

为此,在低频段可由式(1)通过减小fr来降低f0min,提高k以提高信号的时域精度,可以采用分频的方法,即在不同的频率段采用不同的时标时钟fr来解决这个问题,分段时标见表1。

[tr]

[/tr]

4 上位机界面、信号参数定义与接口

本设计采用USB1.1作为通信接口,针对由PDIUSBD12实现的USB接口,可以利用Philips公司提供的EasyD12库来编写PC机应用程序。EasyD12库包含3个文件,分别是EasyD12.lib、EasyD12.dll和EasyD12.h。库文件提供了4个可以调用的函数,用于完成对PDIUSBD12端点1、端点2的读写操作。这4个函数分别为:

采用上述4个函数可以简单地完成对PDIUS-BD12的读写操作。由于本设计中通用USB数据传输模块的主要作用是由控制界面向接口模块发送各种命令及波形数据,PC机对发送的时机是十分清楚的(通常在按键或菜单选项的响应函数中出现),所以命令及数据的可靠性及实时性能得到充分的保障。

主控制界面由波形设置、任意波形、模拟调制、数字调制、扫描信号、端口设置等部分组成,利用Delphi7.0提供的强大控件对信号幅度、频率、占空比等参数实现实时控制,还有任意信号的手动制作和特殊波形(如抽样波形、正弦的谐波合成、可控数码流等)的采样。图4为数码流PC控制界面。

[tr]

[/tr]任意波形产生是用户在画图区用鼠标绘制任意形状的单值波形.把PixelFormat属性设置为pf8bit,信号幅度采集分辨率为10位,通过对画板上的波形扫描把黑色的像素点用数组记录该处坐标值,扫描后得到所需波形数据。

时域信号叠加产生是依据各种实际需要,对常规波形进行叠加。软件主要由波形构造、数据计算分析及控制组成。通过用户输入的公式及各常规波形的参数计算得出新的波形数据,然后根据数据进行描图。计算定义为时域波形数据的加、减、乘、除。

频域还原时域信号产生是采用谐波输入法。依据幅度谱和相位谱信息。利用反傅立叶变换实偶对称级数,还原为时域波形,经4 096个点数据采集,10位量化编码后得到所需波形数据。

5 研制结果与展望

研制的双通道“便携式DDS高精度信号发生器”样机采用40 MHz外部晶振,TFT选用彩色PT035TNO1,FPGA选用Altera-Cyclone系列EP1C6 T114-8。DAC选用10位ADI-AD9763,运算放大器选用ADI-AD8014,MCU 选用Philips-P89LV51RD2,Flash选用AM19LV160D。主要性能如下:

(1)主波形有正弦波、方波等,100μHz~10MHz,储存波形为100 Hz~100 kHz。分辨率为100μHz。幅度分辨率10 bit,(≤10 MHz)10 mV~18Vp-p(高阻),1 mV~10 Vp-p(50 Ω)。

(2)任意波形由计算机界面输入,具有时域与频域三种输入方式。

(3)调制特性:内调制,调制信号频率范围为100μHz~1 MHz,调制深度范围为1%~100%,数码流、码元速率可编程,调频时最大频偏为载波频率的50%。

(4)扫描特性:频率扫描扫描起终点及步进100μHz≤f≤10 MHz,幅度扫描扫描起终点及步进10mV≤V≤10 V,步进时间均为1 ms~20 s,线性扫描。向上或向下或来回扫描,自动控制方式。

(5)伪随机噪声:随机码元移位速率可调,可编程数码流:码元32位可编程输入,波特率1 kb/s~1000 kb/s,电平10mV~10 V。

实验表明:研制的样机功能多、操作方便、TFT与PC屏幕显示直观、具有独特的任意信号输入方式、性价比高,仪器还可设计对外部输入信号实时调制,直流分量应可控,由矢量分析仪产生的频谱图存储后转入信号发生器来重现时域波形的工作正在研究之中。

举报

举报

举报

举报