一、串行数据系统的基本知识

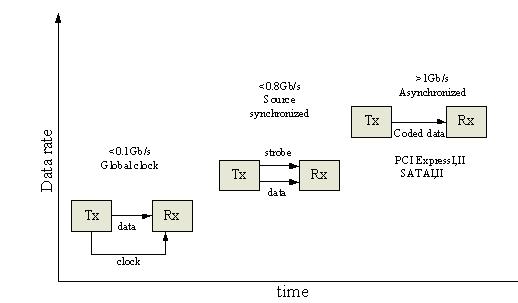

随着串行数据速率的不断提升,串行数据系统的传输结构也不断的发生着变化以适应高速传输的要求:

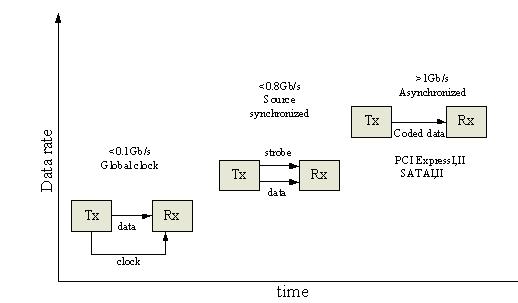

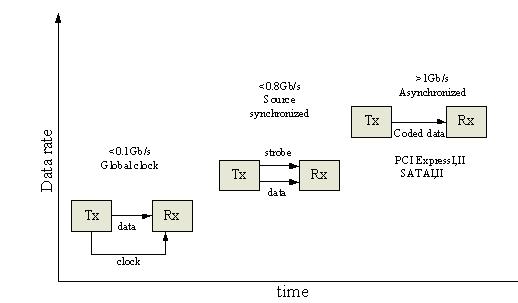

下图1所示为不同的数据速率所对应的系统传输结构:

图1不同数据速率下对应的系统传输结构

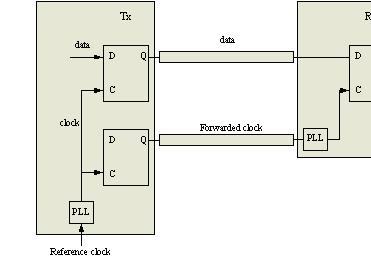

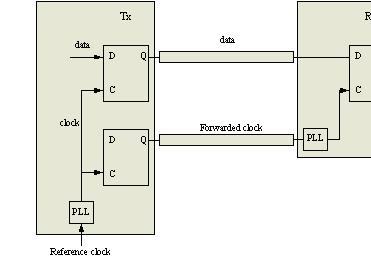

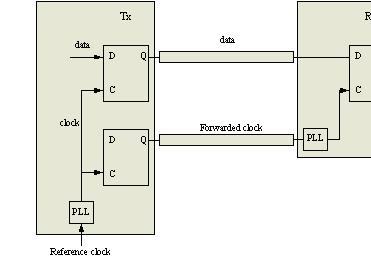

从左到右依次为全局时钟系统结构、源同步时钟系统结构、嵌入式时钟系统结构,随着数据速率的进一步提升,还有可能出现其它多种结构,如下图2的前向时钟系统结构,在10Gbps以上的串行数据传输系统中很可能会使用这种传输结构

图2前向时钟系统结构(ForwardedClockSystem)

从上图1中可以看出:

1、典型串行数据传输系统主要构成因素包括:发送端TX,接收端RX,时钟信号及其传输通道,数据信号及其传输通道

2、随着数据速率的提升,串行数据系统传输结构发生的变化主要集中在时钟信号及其传输通道的变化,在当前新一代的串行数据系统中,如PCIExpress(I,II),SATA(I,II)等,已经没有了专门的时钟信号传输通道,而是将时钟信号嵌入到了数据中进行传输,因此需要在接收端能有效的将时钟恢复出来

那么为何数据速率的提升需要改变时钟信号及其传输结构呢?了解下接收端芯片的基本工作原理会有助于我们理解这些变化。

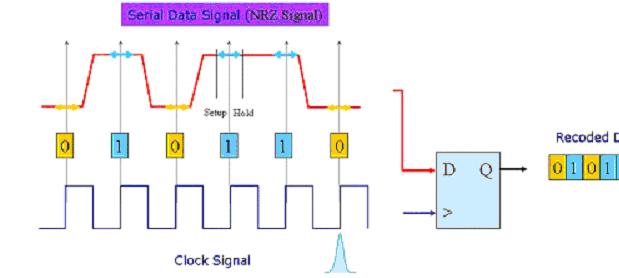

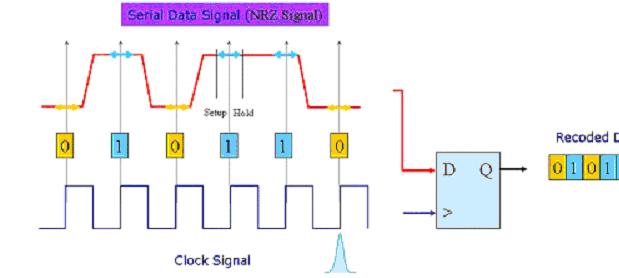

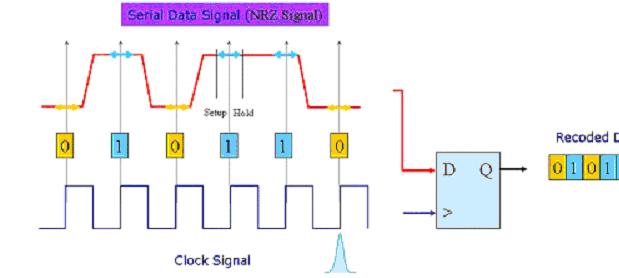

通信系统的实质是通过一段介质发送或者接收数据。发送端TX发出不同编码形式的高速串行数据,经过一段链路传输后到达接收端RX,串行数据在传输过程中会受到各种各样的干扰,引起数据的抖动,串行数据系统工作的目的就是要尽可能的减少这些干扰的影响使得接收端能准确无误的恢复出发送端发送过来的数据。如下图3所示,

图3串行数据系统中接收端接收数据的图示

由于接收端(一般是由D触发器构成)需要使用时钟采样来完成同步接收数据,因此时钟信号和数据信号之间的同步关系是非常重要的,即必须要满足一定的建立时间和保持时间。因此串行数据时钟系统结构的变化最根本上是为了满足时钟与数据之间的时序关系,以便接收端能正确的接收到信号。

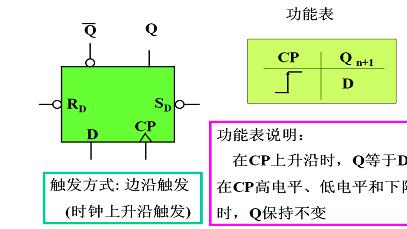

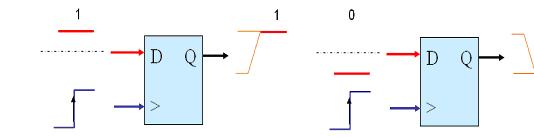

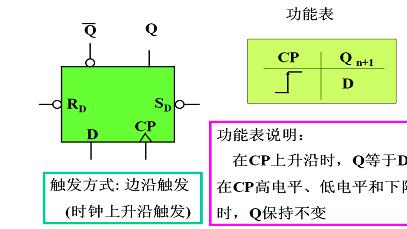

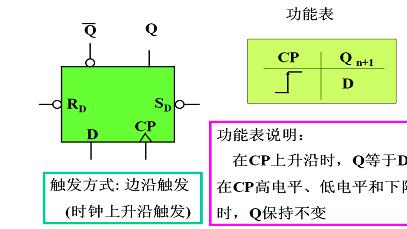

接收端D触发器的工作原理

图4D触发器的基本功能

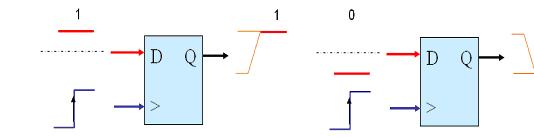

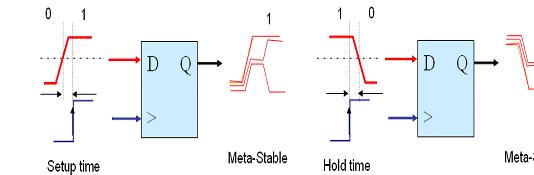

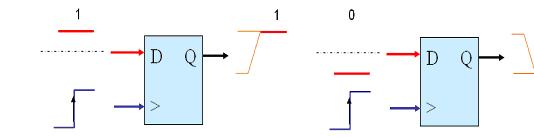

D触发器触发直流电平示例(时钟上升沿触发):

图5D触发器接收无翻转电平信号

可见,当输入触发器的电平没有翻转时,触发器能稳定的恢复出输入信号。

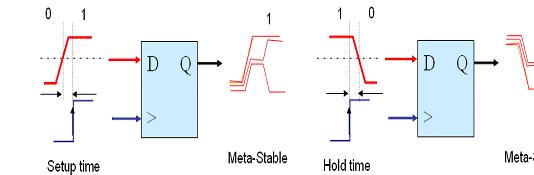

D触发器触发触发脉冲信号示例(时钟上升沿触发):

图6D触发器接收翻转的电平信号

(如果时钟和数据之间的相对抖动偏差太大,将会导致图示D触发器输出信号的逻辑翻转错误或者不稳定)

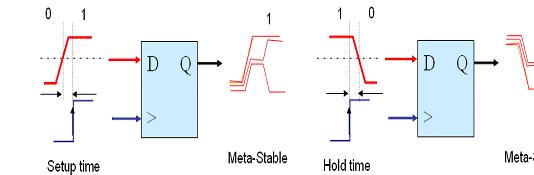

当数据信号的电平发生翻转后,时钟边沿与数据边沿需要一定的建立时间来锁存数据;同时,数据信号的电平需要一定的保持时间让时钟能稳定的锁存数据。为了让建立时间和保持时间最大化,时钟最好能出现在数据比特位的中央。但是由于数据或者时钟存在抖动,抖动较大时,无法满足建立时间和保持时间的要求,D触发器可能输出错误的数据,产生误码。特别是在高速数字电路中,速率的增加导致建立时间和保持时间的余量越来越小,由于抖动产生误码的概率越来越高,所以,时钟和数据的抖动测试非常重要。

二、抖动的基本概念

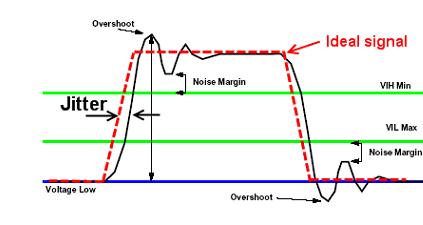

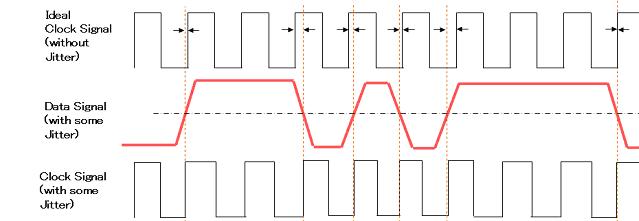

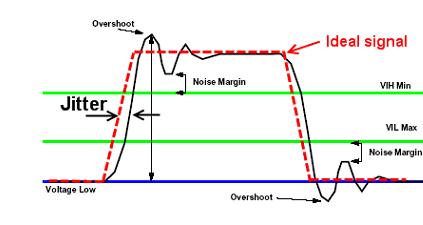

抖动的定义为信号在电平转换时,其边沿与理想时间位置的偏移量。抖动比较大时可能出现:并行总线的建立保持时间余量不够、时钟稳定度差、串行信号接收端误码率高等现象。

图7理想数字信号和实际数字信号的差别

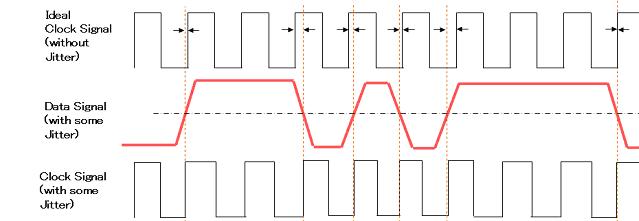

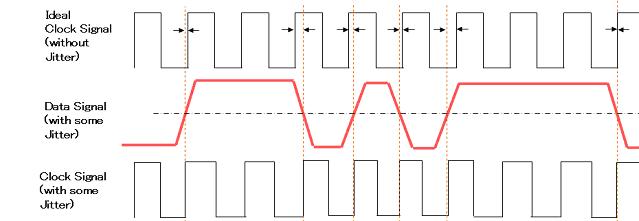

研究串行数据系统的抖动主要是研究时钟与串行数据的相对抖动,而不是单纯的指时钟抖动或者数据抖动。也就是说即使时钟有很大的抖动,但是只要数据也存在同样大的抖动,则两者之间的相对抖动仍旧很小,时钟和数据之间的建立时间和保持时间也仍旧能够得到保证。如下图所示:

图8串行数据系统中研究数据和时钟之间的相对抖动才是最重要的,目标是使得数据信号和时钟信号同相位

当带有抖动的数据信号与带有抖动的时钟信号出现较大的相位偏差时,系统即有可能出现建立时间、保持时间不够,出现误码等情况;这个偏差叫做串行数据的时间间隔误差(TIE,timeintervalerror)。每一个时钟边沿和数据边沿都会有一个时间间隔误差,那么我们需要关注哪一个边沿的TIE呢?还是关注一段时间内(一定的波形数量)所有波形边沿的TIE的累积效果呢?需要多少波形数据统计运算得到的TIE才符合要求呢?搞清楚这几个问题需要了解下串行数据系统中经常用到的另外一个概念:误码率(BER,biterrorrate)

三、串行数据系统中误码率的概念

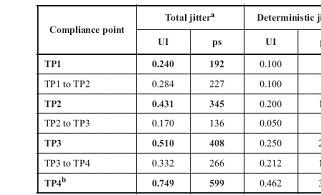

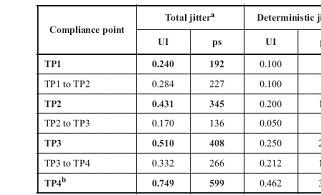

由于串行数据系统需要在一给定的时间内发送或者传输许多位的数据,因此衡量系统的整体性能通常由在一段时间内或者一定数量的数据进行衡量,即发送端发送一定量的数据,在接收端接收到的数据中出现错误位的比率,也叫做误码率。大部分的串行数据标准要求,发送端发送10e+12个误码,在接收端出现误码的比率不能多于一个,也就是误码率为10e-12,相对应的要求在此误码率下抖动不能超过一定的值。而示波器累积10e+12个误码,可能需要数天的时间,因此示波器在分析误码率抖动时通常需要用到统计分析、外推等抖动算法。

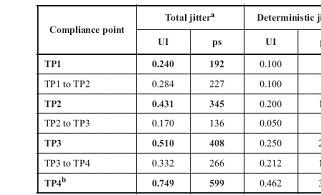

图91000M以太网标准对抖动的要求

四、抖动的来源

产生抖动的原因有多种,从元器件来看分为intrinsic抖动与nonintrinsic抖动两种,前者是与电子器件和半导体器件的电子和空穴特性有关,后者与电路的设计有关,可以通过优化设计来改善。前者产生的抖动称为随机抖动(RandomJitter,简称Rj),后者产生的抖动称为固有抖动(Deterministicjitter)。随机抖动的来源为热噪声、ShotNoise和FlickNoise。固定抖动的来源为:开关电源噪声、反射、串扰、电磁干扰等等。在后续专门介绍随机抖动和固有抖动的文章中将详细介绍。

一、串行数据系统的基本知识

随着串行数据速率的不断提升,串行数据系统的传输结构也不断的发生着变化以适应高速传输的要求:

下图1所示为不同的数据速率所对应的系统传输结构:

图1不同数据速率下对应的系统传输结构

从左到右依次为全局时钟系统结构、源同步时钟系统结构、嵌入式时钟系统结构,随着数据速率的进一步提升,还有可能出现其它多种结构,如下图2的前向时钟系统结构,在10Gbps以上的串行数据传输系统中很可能会使用这种传输结构

图2前向时钟系统结构(ForwardedClockSystem)

从上图1中可以看出:

1、典型串行数据传输系统主要构成因素包括:发送端TX,接收端RX,时钟信号及其传输通道,数据信号及其传输通道

2、随着数据速率的提升,串行数据系统传输结构发生的变化主要集中在时钟信号及其传输通道的变化,在当前新一代的串行数据系统中,如PCIExpress(I,II),SATA(I,II)等,已经没有了专门的时钟信号传输通道,而是将时钟信号嵌入到了数据中进行传输,因此需要在接收端能有效的将时钟恢复出来

那么为何数据速率的提升需要改变时钟信号及其传输结构呢?了解下接收端芯片的基本工作原理会有助于我们理解这些变化。

通信系统的实质是通过一段介质发送或者接收数据。发送端TX发出不同编码形式的高速串行数据,经过一段链路传输后到达接收端RX,串行数据在传输过程中会受到各种各样的干扰,引起数据的抖动,串行数据系统工作的目的就是要尽可能的减少这些干扰的影响使得接收端能准确无误的恢复出发送端发送过来的数据。如下图3所示,

图3串行数据系统中接收端接收数据的图示

由于接收端(一般是由D触发器构成)需要使用时钟采样来完成同步接收数据,因此时钟信号和数据信号之间的同步关系是非常重要的,即必须要满足一定的建立时间和保持时间。因此串行数据时钟系统结构的变化最根本上是为了满足时钟与数据之间的时序关系,以便接收端能正确的接收到信号。

接收端D触发器的工作原理

图4D触发器的基本功能

D触发器触发直流电平示例(时钟上升沿触发):

图5D触发器接收无翻转电平信号

可见,当输入触发器的电平没有翻转时,触发器能稳定的恢复出输入信号。

D触发器触发触发脉冲信号示例(时钟上升沿触发):

图6D触发器接收翻转的电平信号

(如果时钟和数据之间的相对抖动偏差太大,将会导致图示D触发器输出信号的逻辑翻转错误或者不稳定)

当数据信号的电平发生翻转后,时钟边沿与数据边沿需要一定的建立时间来锁存数据;同时,数据信号的电平需要一定的保持时间让时钟能稳定的锁存数据。为了让建立时间和保持时间最大化,时钟最好能出现在数据比特位的中央。但是由于数据或者时钟存在抖动,抖动较大时,无法满足建立时间和保持时间的要求,D触发器可能输出错误的数据,产生误码。特别是在高速数字电路中,速率的增加导致建立时间和保持时间的余量越来越小,由于抖动产生误码的概率越来越高,所以,时钟和数据的抖动测试非常重要。

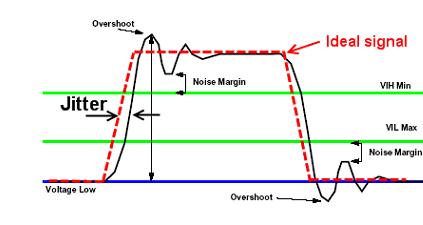

二、抖动的基本概念

抖动的定义为信号在电平转换时,其边沿与理想时间位置的偏移量。抖动比较大时可能出现:并行总线的建立保持时间余量不够、时钟稳定度差、串行信号接收端误码率高等现象。

图7理想数字信号和实际数字信号的差别

研究串行数据系统的抖动主要是研究时钟与串行数据的相对抖动,而不是单纯的指时钟抖动或者数据抖动。也就是说即使时钟有很大的抖动,但是只要数据也存在同样大的抖动,则两者之间的相对抖动仍旧很小,时钟和数据之间的建立时间和保持时间也仍旧能够得到保证。如下图所示:

图8串行数据系统中研究数据和时钟之间的相对抖动才是最重要的,目标是使得数据信号和时钟信号同相位

当带有抖动的数据信号与带有抖动的时钟信号出现较大的相位偏差时,系统即有可能出现建立时间、保持时间不够,出现误码等情况;这个偏差叫做串行数据的时间间隔误差(TIE,timeintervalerror)。每一个时钟边沿和数据边沿都会有一个时间间隔误差,那么我们需要关注哪一个边沿的TIE呢?还是关注一段时间内(一定的波形数量)所有波形边沿的TIE的累积效果呢?需要多少波形数据统计运算得到的TIE才符合要求呢?搞清楚这几个问题需要了解下串行数据系统中经常用到的另外一个概念:误码率(BER,biterrorrate)

三、串行数据系统中误码率的概念

由于串行数据系统需要在一给定的时间内发送或者传输许多位的数据,因此衡量系统的整体性能通常由在一段时间内或者一定数量的数据进行衡量,即发送端发送一定量的数据,在接收端接收到的数据中出现错误位的比率,也叫做误码率。大部分的串行数据标准要求,发送端发送10e+12个误码,在接收端出现误码的比率不能多于一个,也就是误码率为10e-12,相对应的要求在此误码率下抖动不能超过一定的值。而示波器累积10e+12个误码,可能需要数天的时间,因此示波器在分析误码率抖动时通常需要用到统计分析、外推等抖动算法。

图91000M以太网标准对抖动的要求

四、抖动的来源

产生抖动的原因有多种,从元器件来看分为intrinsic抖动与nonintrinsic抖动两种,前者是与电子器件和半导体器件的电子和空穴特性有关,后者与电路的设计有关,可以通过优化设计来改善。前者产生的抖动称为随机抖动(RandomJitter,简称Rj),后者产生的抖动称为固有抖动(Deterministicjitter)。随机抖动的来源为热噪声、ShotNoise和FlickNoise。固定抖动的来源为:开关电源噪声、反射、串扰、电磁干扰等等。在后续专门介绍随机抖动和固有抖动的文章中将详细介绍。

举报

举报

举报

举报