| [td]固定频率应用 [td]GSM1800 应用 [/tr] |

| RF = 1.8 GHz, [td]RF = 1.8 GHz, [/tr] |

| fosc = 13 MHz, [td]fosc = 13 MHz, [/tr] |

| 固定输出频率 [td]fres = 200 kHz [/tr] |

| ADF4106[td]FOM + 10log fpfd + 20log N [td]FOM + 10log fpfd + 20log N [/tr] |

| 整数N 分[td]= –223 + 10log 13 MHz + [td]= –223 + 10log 200 kHz [/tr] |

| 频PLL[td]20log 138 = –109 dBc/Hz [td]+ 20log 9000 = –91 dBc/Hz [/tr] |

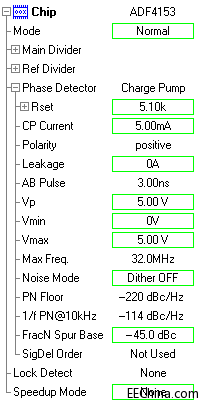

| ADF4153 小数N 分[td]FOM + 10log fpfd + 20log N [td]FOM + 10log fpfd + 20log N [/tr] |

| 频PLL[td]= –220 + 10log 13 MHz [td]= –220 + 10log 13 MHz [/tr] |

| [td]+ 20log 138 = –106 dBc/Hz [td]+ 20log 138 = –106 dBc/Hz [/tr] |

| 结果[td]使用整数N分频更佳 [td]使用小数N分频更佳 [/tr] |

| [td]最小值 [td]典型值 [td]最大值 [td]单位 [/tr] |

| 输入高电压, VINH[td]1.5 [td] [td][td]V [/tr] |

| 输入低电压, VINL[td] [td][td]0.6 [td]V [/tr] |

| 输入电流, IINH/IINL[td] [td][td]±1 [td]μA [/tr] |

| 输入电容, CIN[td] [td]3[td] [td]pF[/tr] |

举报

举报

更多回帖