大多数信号处理系统首先是通过其模拟或RF频率、动态范围和采样速率进行定义,以建立转换器选择标准。然而,当与

FPGA匹配进行数据处理时,无论如何都不能忽视对转换器数字接口的考量。

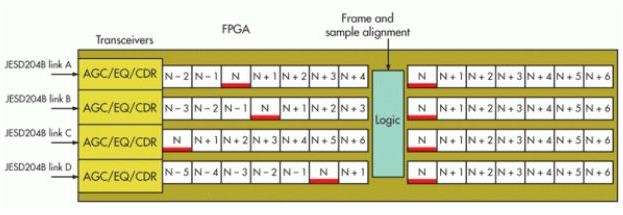

现在随着更多的模数转换器(ADC)和数模转换器(DAC)支持最新的JESD204B串行接口标准,出现了FPGA与这些模拟产品的最佳接口方式问题。

FPGA一直支持千兆串行/解串(SERDES)收发器。然而在过去,大多数ADC和DAC不能通过这些高速串行接口进行配置,就是说FPGA与转换器无法与任何常用标准接口,利用高串行-解串(SERDES)带宽。

新型转换器与JESD204B之类的FPGA接口较为复杂,如何让JESD204B在FPGA上工作?FPGA对于JESD204B需要多少速度?

举报

举报

举报

举报