| ADC[td]工艺 [td]输入结构[td]绝对最大 [td]差分摆幅 [/tr] |

| (nm) [td]输入电压(V) [td](V p-p) [/tr] |

| 14位 105 MSPS[td]350 [td]缓冲 [td]7 [td]9.2 [/tr] |

| 14位 125 MSPS[td]180 [td]未缓冲 [td]2 [td]4.5 [/tr] |

| 16位 250 MSPS[td]180 [td]缓冲 [td]3.6 [td]6 [/tr] |

| 12位 2.5 GSPS[td]65 [td]未缓冲 [td]1.52 [td]4 [/tr] |

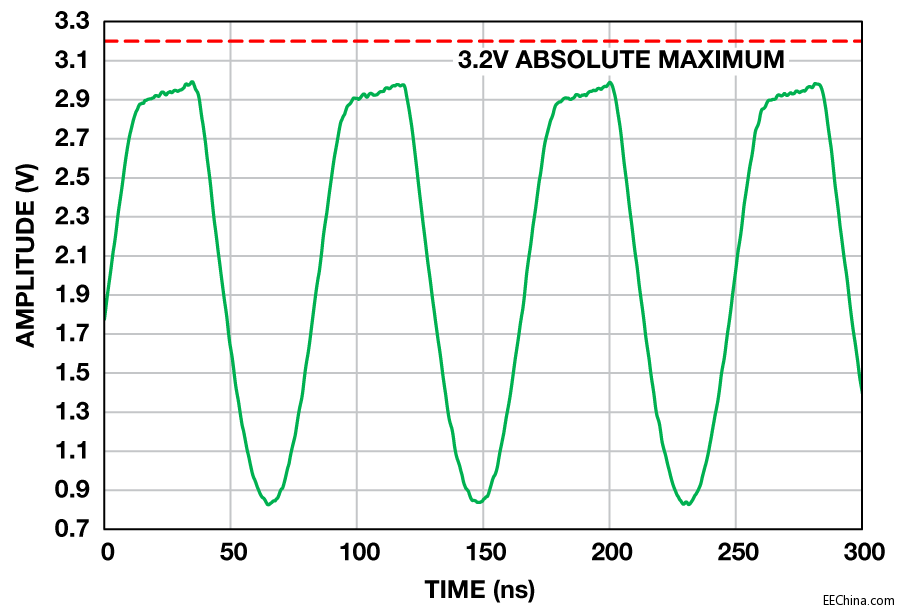

| 14位 1.0 GSPS[td]65 [td]缓冲 [td]3.2 [td]4.6 [/tr] |

| 参数[td]数值 [td]单位 [td]注释 [/tr] |

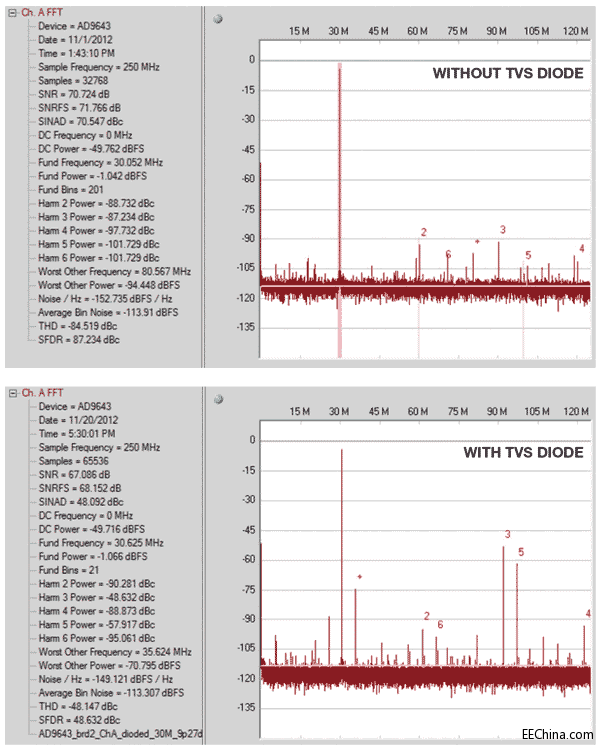

| 反向电压(VR)[td]3 [td]V [td]AD9680数据手册中,绝对最大额定电压值为VIN± = 3.2 V [/tr] |

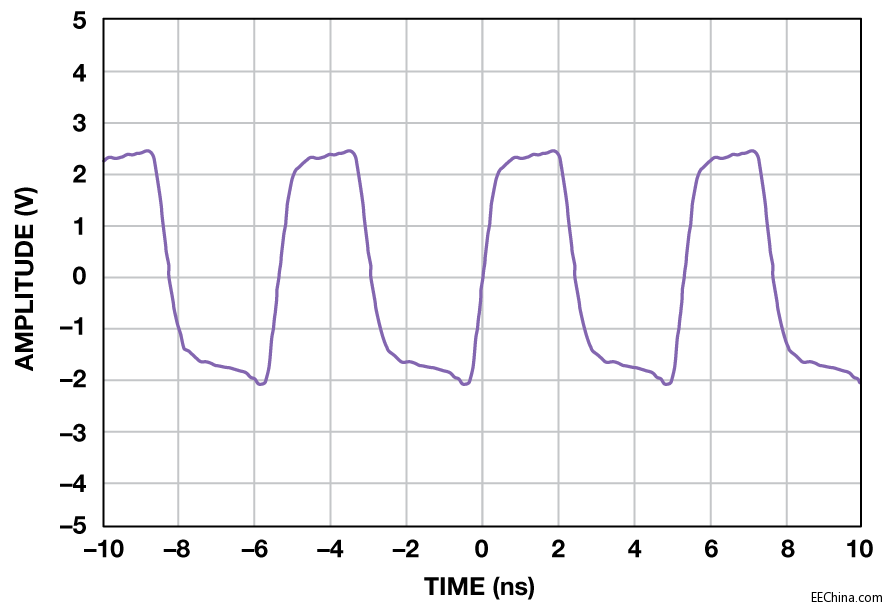

| 端点之间的电容[td]0.8[td]pF[td]正常条件下对ADC性能影响较小[/tr] |

| (CJ0, 或 Ct)[/tr] |

举报

举报

更多回帖