差分信号适合于需要大信噪比、高抗扰度和较低二次谐波失真的电路,例如高性能 ADC 驱动和高保真度音频信号处理等应用。《模拟对话》曾刊载过一篇相关文章——“多功能、低功耗、精密单端差分转换器”1,其中介绍了一种有很大改进的单端转差分电路,它具有很高输入阻抗,最大输入偏置电流为 2 nA,最大失调 (RTI) 为 60 μV,最大失调漂移为 0.7 μV/°C。性能改进是通过在反馈环路中将 OP1177 与差分增益为 1 的 AD8476 级联而实现的。

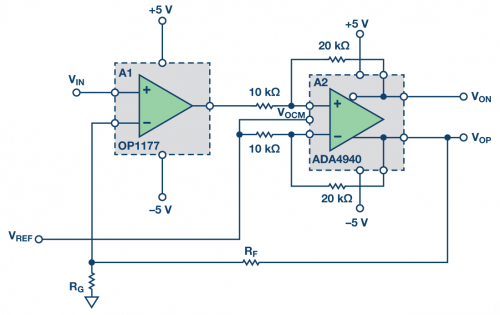

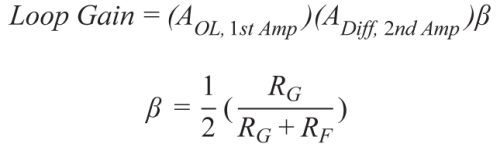

图 1. 改进的单端转差分电路

然而,许多应用需要更大的输出动态范围,例如温度和压力传感器输出的信号调理等。如果还能调节共模,那么该电路将能非常方便地与许多ADC 接口,其基准电压决定满量程范围。

图 2. 具有改进动态范围的单端转差分电路

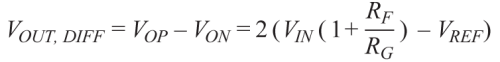

将环路内部差分放大器的增益配置为大于 1 的值,可提高电路的输出动态范围(图 2)。输出通过下式计算:

其中 RG 保持开路,电路的总增益为 2。A1 (OP1177) 的输出通过下式计算:

注意:VREF 始终增加到 OP1177 的输出上,从而会限制其输出裕量。多数应用中,VREF(输出共模)设置在电源的中点,以提供最大输出动态范围。环路内部增益大于 1 的差分放大器,例如 2 中的 ADA4940(增益为 2),可降低 A1 输出电压,降低倍数为 A2 的差分增益,这样便有助于避免图 A1 输出饱和。采用±5 V 电源时,OP1177 的典型输出摆幅为 4.1 V,因此,当 VREF 设置为 0 时,图 2 所示电路的差分输出电压摆幅约为±8 V。将 A2 增益配置为 3 可进一步改善输出动态范围,实现电路的最大输出摆幅。另一个可用增益为 1、2 和 3 的放大器 ADA4950,也适合用作 A2。

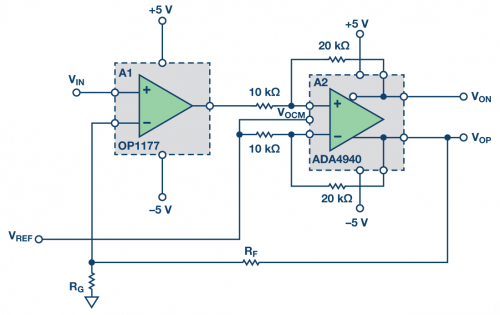

可调输出共模

可以修改电路,使输出共模可调且独立于输入信号的共模。对于输入以地为基准且需要转换为具有高共模的差分信号以与 ADC接口的单电源应用,这样做可带来极大的灵活性和便利。

实现方法是在输入端增加两个电阻 R1 和 R2,R2 连接到 VOCM。若需要,可以使用输入放大器 A1 的双通道版本 OP2177,对于非常低的输入偏置电流,可将第二放大器用作输入缓冲器。

图 3(a) 改进的单端差分转换器,具有可调共模。

图 3(b) 输入和输出图,红线为 VOP,黄线为 VON,蓝线为输入。共模为 0V。

图 3(c) 输入和输出图,红线为 VOP,黄线为 VON,蓝线为输入。共模为 2.5 V。

在图 1 所示电路中,输入以 VREF 为基准。参见图 3 所示电路,输入以地为基准,直接获取后转换为差分输出。现在可以调节 VOCM 以使共模输出偏移,而输入仍然以地为基准。VOCM 可以设为基准电压源的一半或转换器的中间电平。VOCM 基本上像 VIN 一样,用作另一个输入。所选电阻值应满足下式:

通过叠加,当 VIN 为 0 时,输出值与 VOCM 相同。由于 VOCM 是设置输出共模的值,因此差分输出为 0。若 R1 = RG 且 R2 = RF,则输出电压由下式给出:

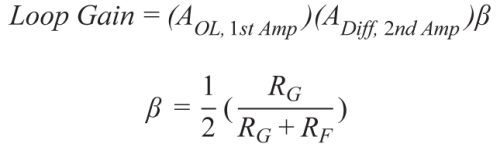

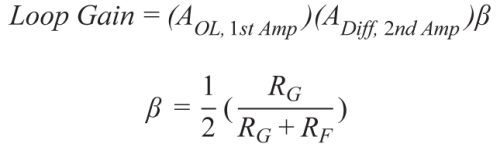

带宽和稳定性

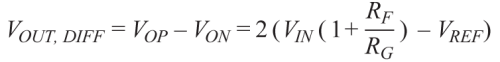

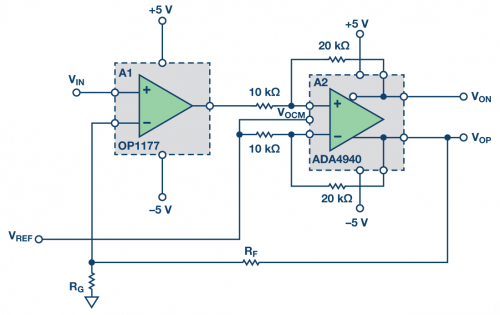

两个放大器构成一个伺服环路配置的复合差分输出运算放大器。OP1177/OP2177 的开环增益和 ADA4940 的差分增益合并,得到电路的总开环增益,其定义电路的总带宽。其极点的合并则使环路的相移增加。A2 使用较高增益时,会降低其带宽,并可能影响电路整体的稳定性。电路设计人员须检查电路整体的频率响应,评估是否需要补偿。为了确保反馈系统的稳定性,经验法则是随频率而变化的合并开环增益必须以–20 dB/ 十倍频程的滚降速率跨过单位增益。这在最小增益(2 倍增益)的应用中更为重要,因为环路增益处于最大值,相位裕量最差。提高总增益,从而减小带宽并增加反馈环路的相位裕量,也能改善稳定性。因为环路增益减小,它会在较低的频率跨过单位增益。环路增益由下式计算:

反馈系数β中有一个 1/2 ,这 是因为输出为差分,而反馈仅从差分输出之一中获得。ADA4940 在 2 倍增益时的带宽为 50 MHz,而 OP1177 的单位增益带宽约为 4 MHz。受限于 OP1177 和闭环增益,图 3 所示电路在带宽约为 1 MHz 时可稳定工作。如之前文章中所指出的,当使用差分放大器无法满足稳定性条件时,可以使用一个限带电容,如图 3(a)所示。该电容与反馈环路内部的 RF 形成一个积分器,将电路整体的带宽限制为:

可以适当选择电容和反馈电阻,使总带宽受上式限制。

差分信号适合于需要大信噪比、高抗扰度和较低二次谐波失真的电路,例如高性能 ADC 驱动和高保真度音频信号处理等应用。《模拟对话》曾刊载过一篇相关文章——“多功能、低功耗、精密单端差分转换器”1,其中介绍了一种有很大改进的单端转差分电路,它具有很高输入阻抗,最大输入偏置电流为 2 nA,最大失调 (RTI) 为 60 μV,最大失调漂移为 0.7 μV/°C。性能改进是通过在反馈环路中将 OP1177 与差分增益为 1 的 AD8476 级联而实现的。

图 1. 改进的单端转差分电路

然而,许多应用需要更大的输出动态范围,例如温度和压力传感器输出的信号调理等。如果还能调节共模,那么该电路将能非常方便地与许多ADC 接口,其基准电压决定满量程范围。

图 2. 具有改进动态范围的单端转差分电路

将环路内部差分放大器的增益配置为大于 1 的值,可提高电路的输出动态范围(图 2)。输出通过下式计算:

其中 RG 保持开路,电路的总增益为 2。A1 (OP1177) 的输出通过下式计算:

注意:VREF 始终增加到 OP1177 的输出上,从而会限制其输出裕量。多数应用中,VREF(输出共模)设置在电源的中点,以提供最大输出动态范围。环路内部增益大于 1 的差分放大器,例如 2 中的 ADA4940(增益为 2),可降低 A1 输出电压,降低倍数为 A2 的差分增益,这样便有助于避免图 A1 输出饱和。采用±5 V 电源时,OP1177 的典型输出摆幅为 4.1 V,因此,当 VREF 设置为 0 时,图 2 所示电路的差分输出电压摆幅约为±8 V。将 A2 增益配置为 3 可进一步改善输出动态范围,实现电路的最大输出摆幅。另一个可用增益为 1、2 和 3 的放大器 ADA4950,也适合用作 A2。

可调输出共模

可以修改电路,使输出共模可调且独立于输入信号的共模。对于输入以地为基准且需要转换为具有高共模的差分信号以与 ADC接口的单电源应用,这样做可带来极大的灵活性和便利。

实现方法是在输入端增加两个电阻 R1 和 R2,R2 连接到 VOCM。若需要,可以使用输入放大器 A1 的双通道版本 OP2177,对于非常低的输入偏置电流,可将第二放大器用作输入缓冲器。

图 3(a) 改进的单端差分转换器,具有可调共模。

图 3(b) 输入和输出图,红线为 VOP,黄线为 VON,蓝线为输入。共模为 0V。

图 3(c) 输入和输出图,红线为 VOP,黄线为 VON,蓝线为输入。共模为 2.5 V。

在图 1 所示电路中,输入以 VREF 为基准。参见图 3 所示电路,输入以地为基准,直接获取后转换为差分输出。现在可以调节 VOCM 以使共模输出偏移,而输入仍然以地为基准。VOCM 可以设为基准电压源的一半或转换器的中间电平。VOCM 基本上像 VIN 一样,用作另一个输入。所选电阻值应满足下式:

通过叠加,当 VIN 为 0 时,输出值与 VOCM 相同。由于 VOCM 是设置输出共模的值,因此差分输出为 0。若 R1 = RG 且 R2 = RF,则输出电压由下式给出:

带宽和稳定性

两个放大器构成一个伺服环路配置的复合差分输出运算放大器。OP1177/OP2177 的开环增益和 ADA4940 的差分增益合并,得到电路的总开环增益,其定义电路的总带宽。其极点的合并则使环路的相移增加。A2 使用较高增益时,会降低其带宽,并可能影响电路整体的稳定性。电路设计人员须检查电路整体的频率响应,评估是否需要补偿。为了确保反馈系统的稳定性,经验法则是随频率而变化的合并开环增益必须以–20 dB/ 十倍频程的滚降速率跨过单位增益。这在最小增益(2 倍增益)的应用中更为重要,因为环路增益处于最大值,相位裕量最差。提高总增益,从而减小带宽并增加反馈环路的相位裕量,也能改善稳定性。因为环路增益减小,它会在较低的频率跨过单位增益。环路增益由下式计算:

反馈系数β中有一个 1/2 ,这 是因为输出为差分,而反馈仅从差分输出之一中获得。ADA4940 在 2 倍增益时的带宽为 50 MHz,而 OP1177 的单位增益带宽约为 4 MHz。受限于 OP1177 和闭环增益,图 3 所示电路在带宽约为 1 MHz 时可稳定工作。如之前文章中所指出的,当使用差分放大器无法满足稳定性条件时,可以使用一个限带电容,如图 3(a)所示。该电容与反馈环路内部的 RF 形成一个积分器,将电路整体的带宽限制为:

可以适当选择电容和反馈电阻,使总带宽受上式限制。

举报

举报

举报

举报