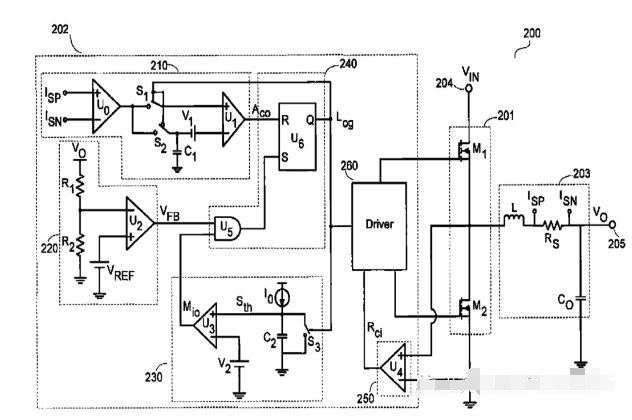

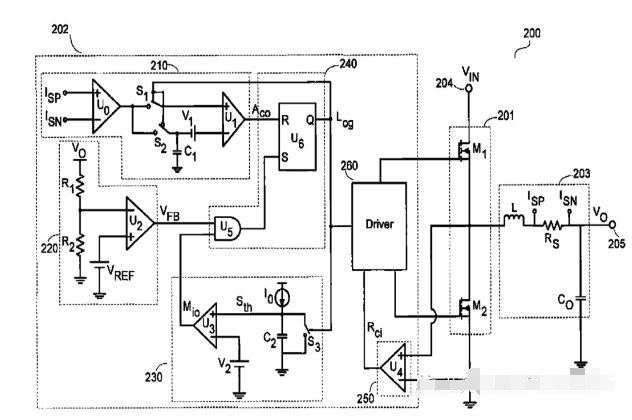

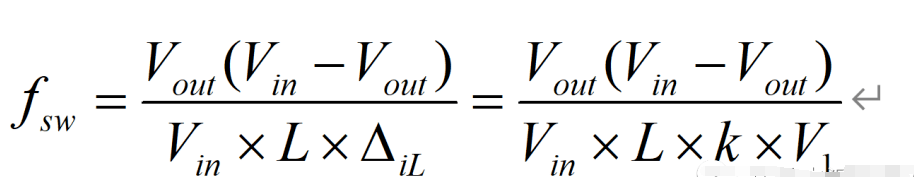

最近还在看COT相关的资料,忽然翻到一篇MPS的专利,我饶有兴致的打印了材料,并饶有兴致的看了起来。基本控制框图如下所示:

图31MPS US8400129B2号专利

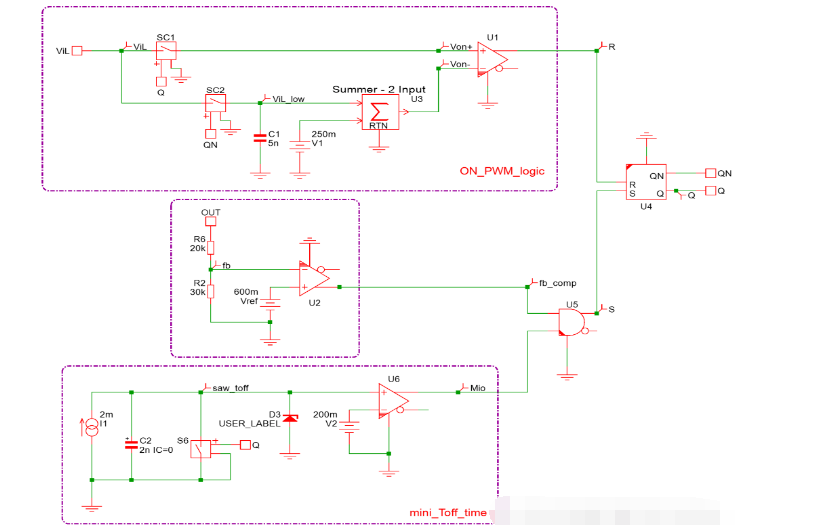

跟我们上一期的控制仿真框图比较,最大的不同在于On Timer处非常不一样。虽然在之前的Part7中,对各个部分做了介绍,但是为了更好地方便大家理解,在这里对上图中的模块在表述一次。

Power Stage部分包含201里面的M1、M2上下两管,以及203中的无源滤波器件,也就是输出电感和输出电容,Rs为电感电流的采样电阻,用于获得电感电流信息。250处是电感电流过零比较器,用于检测电感电流过零点;230为Toff mini timer,和上一期的模型基本一样;220为分压电阻网络的反馈电压和参考电压比较,U2为比较器;240内包含了一个与门和一个RS latch,逻辑思路和上一期的一样;210为触发上管关断的逻辑电路,理解这一部分非常关键。

Rs采样电阻已经将电感电流信号转换为电压信号,在210中经过U0放大,送到S1和S2之前,S1和S2时一对互补开关,当Q拉高时,S1闭合,S2断开;当Q拉低时,S1断开,S2闭合。当S1闭合时,放大的电感电流信号被送入比较器U1的正端。S2之后是一只起电压保持作用的电容C1,V1和电容C1上的电压相加之后送到比较器U1的负端。

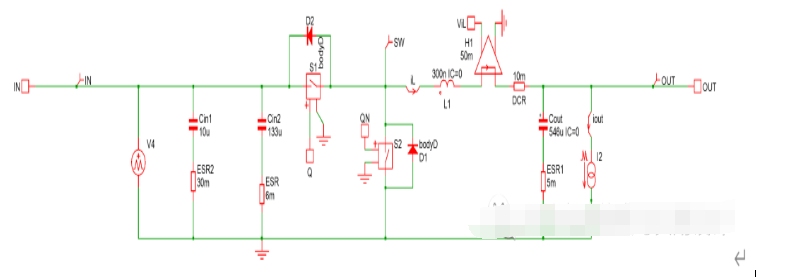

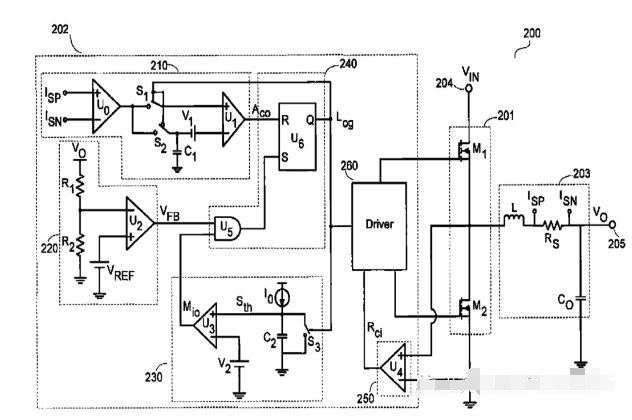

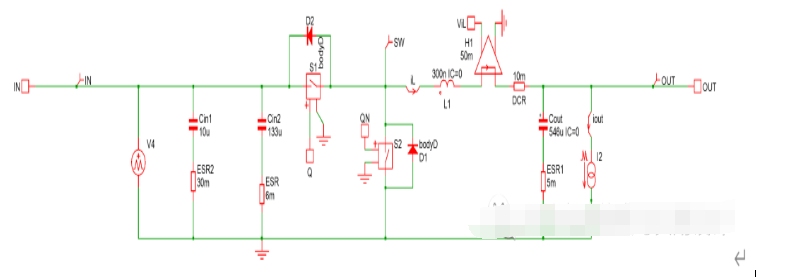

为了更好的说明工作原理,先把仿真图和仿真波形贴出来。

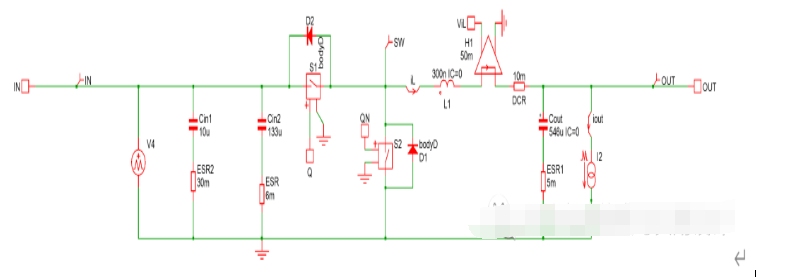

图32 powerstage

PowerStage部分增加了电流采样,比较方便的方法是,利用流控压源模拟电感电流采样转换成电压的效果。这里仅简单的原理性验证,在实际的power IC中,电流采样方法主要是:

先前介绍的DCR采样

利用MOSFET的Rdson采样

电流镜复制采样

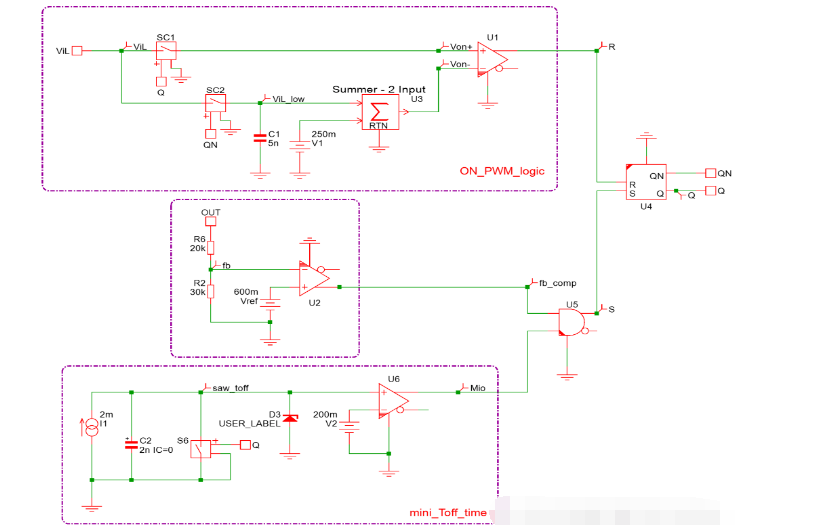

控制框图基本和专利图保持了一致,仅在S1和S2的控制开关信号上,分别用Q和QN替代,逻辑更清晰简洁。另外,Toff mini沿用了之前的模型,增加了钳位二极管,保持住比较器的状态。

以下说明的信号标注皆以仿真图为准,专利图上的信号标注不明确,说明起来比较麻烦。

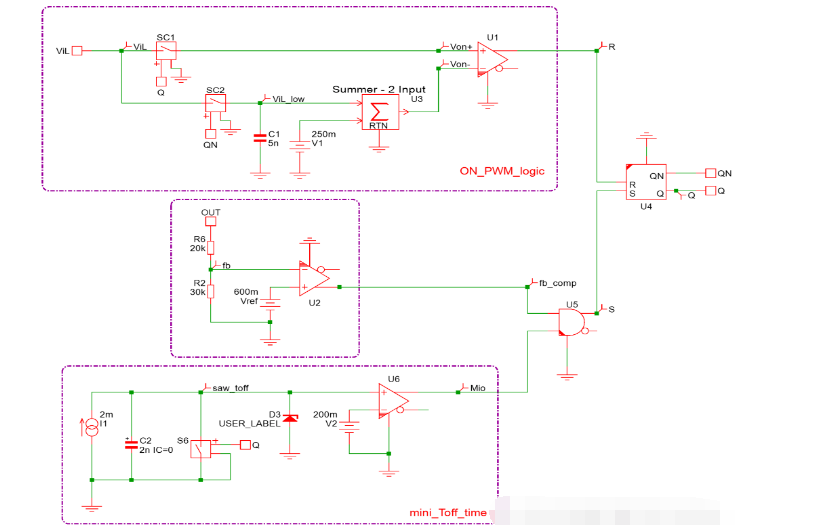

图33 controlblock diagram

当R6、R2的分压网络获得的反馈电压vfb小于参考电压vref时,比较器U2的输出fb_comp信号拉高,假设Toff mini timer的比较器U6的输出信号Mio也拉高(当Toff时间超过Toff_min时,saw_off的电压会大于200mV,因此Mio会保持高信号,等待fb_comp的高电平到来触发下一次Ton)。此时U5的输出拉高,送入RSlatch中的S,置位,则Q输出拉高,上管S1闭合,同时ON_pwm_logic处的SC1开关也会闭合。电感电流线性上升,Von+处的信号此时一直等于ViL,ViL也线性上升。(在此之前,上一周期中,Q拉低、QN拉高的时候,SC2闭合,也就是电感电流下降的时候,ViL_low=ViL)由于SC1和SC2的开关逻辑互补,SC2断开,C1电容上的电压保持为ViL的谷值(也即代表了电感电流的谷值信息)。 因此,此时比较器U1的负端电压等于ViL的谷值ViL_valley+直流偏置电压V1。注意,当Von+超过Von-时,才会输出高电平。细心点,你会发现,直流偏置电压V1就代表了电感电流的纹波值。Von+超过Von-时,输出高电平送入RS latch的R,从而拉低Q,结束上管开通时间,所以在Ton结束时刻,ViL一定是到达了峰值,记为ViL_peak,那么就非常容易看出ViL_peak=ViL_valley+V1。

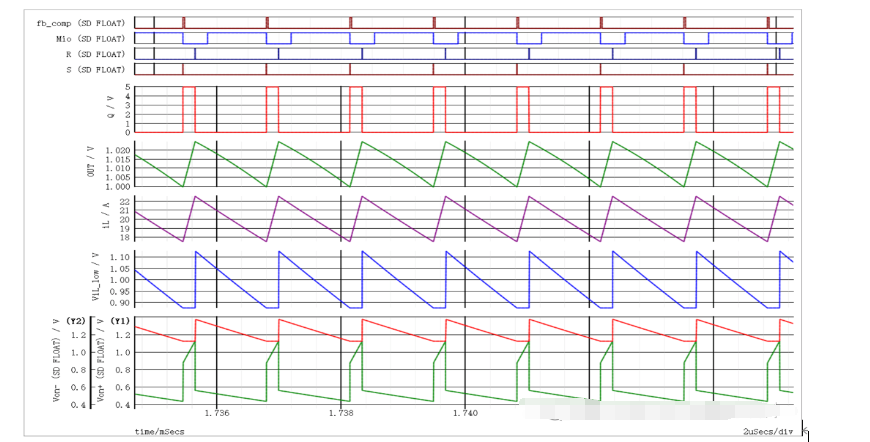

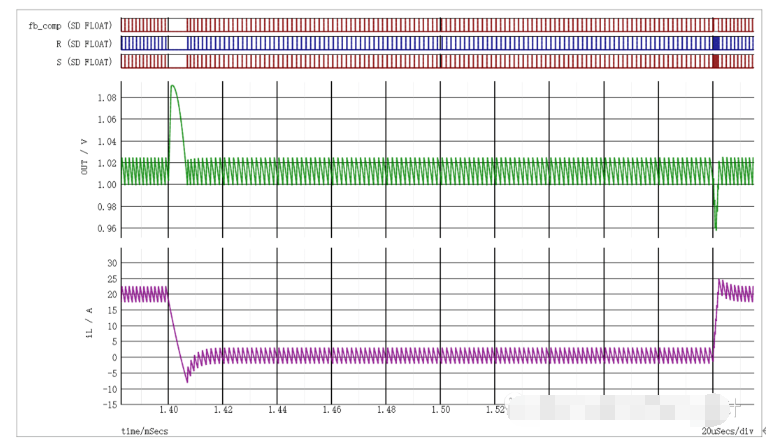

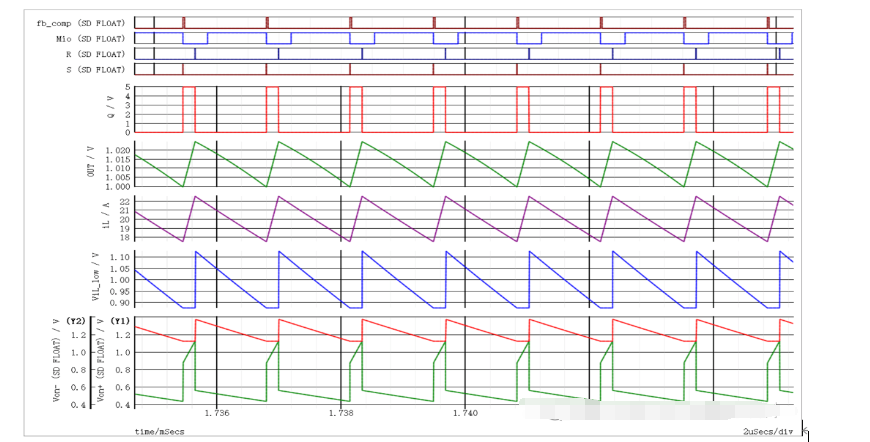

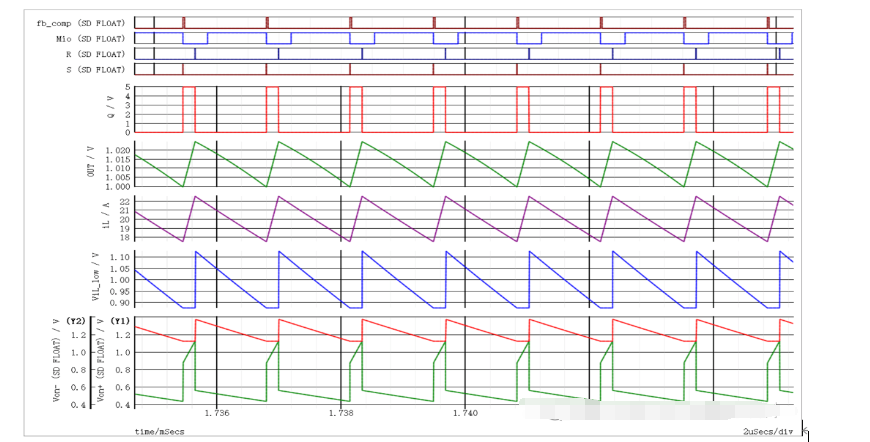

图34 waveof steady situation

当Q拉低之后,Toff timer开始为电容充电,当saw_off超过200mV时,比较器U6输出信号Mio为高。此时SC2闭合,ViL_low=ViL。当off时间段结束时,ViL_low等于ViL的谷值,和上述的情况一致。

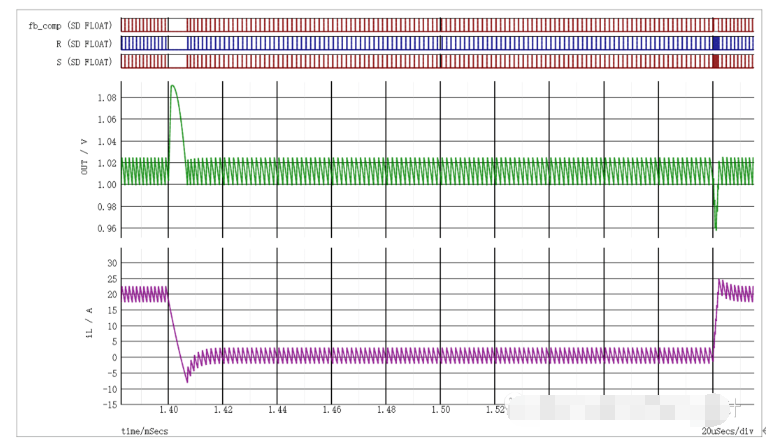

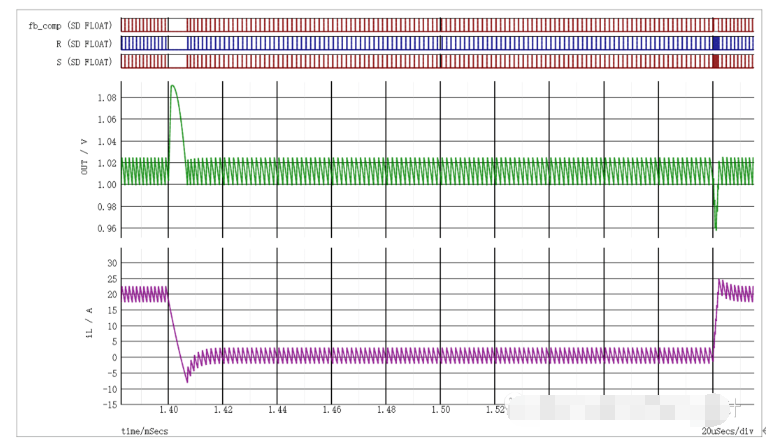

图35 transientresponse

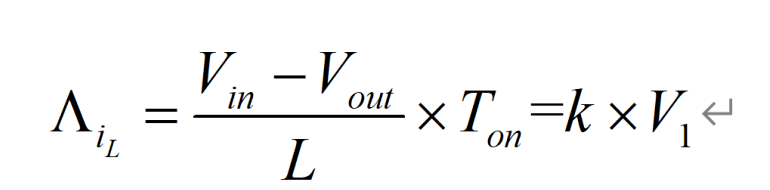

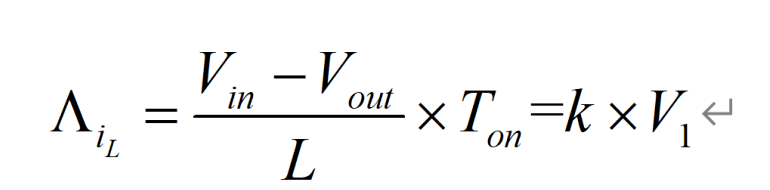

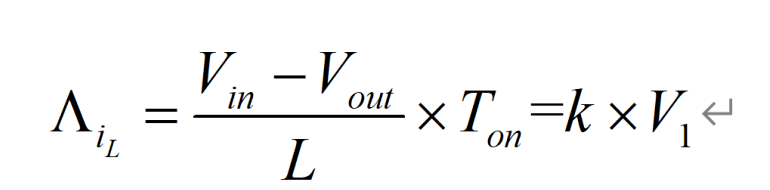

总结一下,这种控制利用一个和电感电流纹波成正比的直流偏置电压作为主要控制手段。在Ton阶段有

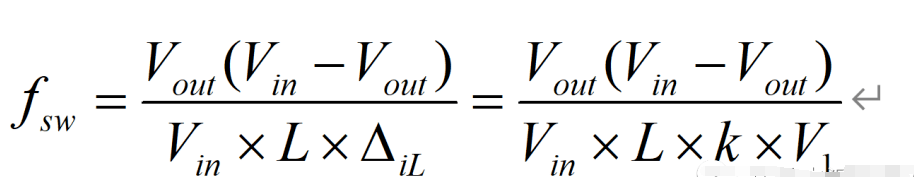

我们姑且称之为恒定电感电流纹波控制法吧。保持电感电流纹波值不变,此时Ton的时间跟会随着Vin增加而减小,随着Vout增加而增大。这种变化关系和之前的ACOT是不是非常像?是的,非常像,但却不一样,其问题在于开关频率。可以推导出开关频率的表达式为

可见其开关频率变化规律却不想Ton时间那么显而易见, 因此它的开关频率的恒定性比不上ACOT的方式,其开关频率变化比较大。可以看出,这种控制方法借鉴了基础的恒定导通时间模式,相当于除了一个L/(Vin-Vout)的系数,改进了一部分的COT模式的性能。

最近还在看COT相关的资料,忽然翻到一篇MPS的专利,我饶有兴致的打印了材料,并饶有兴致的看了起来。基本控制框图如下所示:

图31MPS US8400129B2号专利

跟我们上一期的控制仿真框图比较,最大的不同在于On Timer处非常不一样。虽然在之前的Part7中,对各个部分做了介绍,但是为了更好地方便大家理解,在这里对上图中的模块在表述一次。

Power Stage部分包含201里面的M1、M2上下两管,以及203中的无源滤波器件,也就是输出电感和输出电容,Rs为电感电流的采样电阻,用于获得电感电流信息。250处是电感电流过零比较器,用于检测电感电流过零点;230为Toff mini timer,和上一期的模型基本一样;220为分压电阻网络的反馈电压和参考电压比较,U2为比较器;240内包含了一个与门和一个RS latch,逻辑思路和上一期的一样;210为触发上管关断的逻辑电路,理解这一部分非常关键。

Rs采样电阻已经将电感电流信号转换为电压信号,在210中经过U0放大,送到S1和S2之前,S1和S2时一对互补开关,当Q拉高时,S1闭合,S2断开;当Q拉低时,S1断开,S2闭合。当S1闭合时,放大的电感电流信号被送入比较器U1的正端。S2之后是一只起电压保持作用的电容C1,V1和电容C1上的电压相加之后送到比较器U1的负端。

为了更好的说明工作原理,先把仿真图和仿真波形贴出来。

图32 powerstage

PowerStage部分增加了电流采样,比较方便的方法是,利用流控压源模拟电感电流采样转换成电压的效果。这里仅简单的原理性验证,在实际的power IC中,电流采样方法主要是:

先前介绍的DCR采样

利用MOSFET的Rdson采样

电流镜复制采样

控制框图基本和专利图保持了一致,仅在S1和S2的控制开关信号上,分别用Q和QN替代,逻辑更清晰简洁。另外,Toff mini沿用了之前的模型,增加了钳位二极管,保持住比较器的状态。

以下说明的信号标注皆以仿真图为准,专利图上的信号标注不明确,说明起来比较麻烦。

图33 controlblock diagram

当R6、R2的分压网络获得的反馈电压vfb小于参考电压vref时,比较器U2的输出fb_comp信号拉高,假设Toff mini timer的比较器U6的输出信号Mio也拉高(当Toff时间超过Toff_min时,saw_off的电压会大于200mV,因此Mio会保持高信号,等待fb_comp的高电平到来触发下一次Ton)。此时U5的输出拉高,送入RSlatch中的S,置位,则Q输出拉高,上管S1闭合,同时ON_pwm_logic处的SC1开关也会闭合。电感电流线性上升,Von+处的信号此时一直等于ViL,ViL也线性上升。(在此之前,上一周期中,Q拉低、QN拉高的时候,SC2闭合,也就是电感电流下降的时候,ViL_low=ViL)由于SC1和SC2的开关逻辑互补,SC2断开,C1电容上的电压保持为ViL的谷值(也即代表了电感电流的谷值信息)。 因此,此时比较器U1的负端电压等于ViL的谷值ViL_valley+直流偏置电压V1。注意,当Von+超过Von-时,才会输出高电平。细心点,你会发现,直流偏置电压V1就代表了电感电流的纹波值。Von+超过Von-时,输出高电平送入RS latch的R,从而拉低Q,结束上管开通时间,所以在Ton结束时刻,ViL一定是到达了峰值,记为ViL_peak,那么就非常容易看出ViL_peak=ViL_valley+V1。

图34 waveof steady situation

当Q拉低之后,Toff timer开始为电容充电,当saw_off超过200mV时,比较器U6输出信号Mio为高。此时SC2闭合,ViL_low=ViL。当off时间段结束时,ViL_low等于ViL的谷值,和上述的情况一致。

图35 transientresponse

总结一下,这种控制利用一个和电感电流纹波成正比的直流偏置电压作为主要控制手段。在Ton阶段有

我们姑且称之为恒定电感电流纹波控制法吧。保持电感电流纹波值不变,此时Ton的时间跟会随着Vin增加而减小,随着Vout增加而增大。这种变化关系和之前的ACOT是不是非常像?是的,非常像,但却不一样,其问题在于开关频率。可以推导出开关频率的表达式为

可见其开关频率变化规律却不想Ton时间那么显而易见, 因此它的开关频率的恒定性比不上ACOT的方式,其开关频率变化比较大。可以看出,这种控制方法借鉴了基础的恒定导通时间模式,相当于除了一个L/(Vin-Vout)的系数,改进了一部分的COT模式的性能。

举报

举报

举报

举报

举报

举报