在 Part7 的仿真中,仅仅考虑了 CCM 模式以及 ESR 大大满足稳定性条件的情况。实际工况却更加复杂。我们知道,DCM 下 COT 控制模式可以提供较好的轻载效率,得益于 DCM 模式下,开关频率会降低,开关损耗会降低。跑过模型的朋友应该知道当负载电流降低到 0.5A 的时候,电感电流已经过零反向,进入了强制 CCM 模式(FCCM,Forced Continuous Conduction Mode),而并没有体现 DCM 频率降低时,带来的高轻载效率优势。

在强制 CCM 模式下,电感电流反向将会带来较大的损耗。如何及时地关断同步整流的下管 MOSFET?这就需要用到过零检测电路,当电感电流反向,但负电流还很小的时候关断下管MOSFET,让输出电容提供给负载能量。

先直接利用流控流源采样电感电流,获得过零点,以便说明基础的控制逻辑是怎样的。

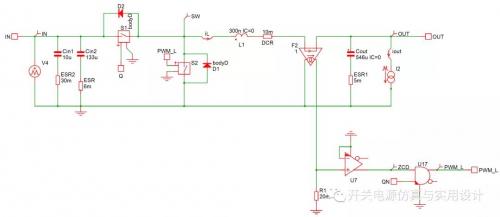

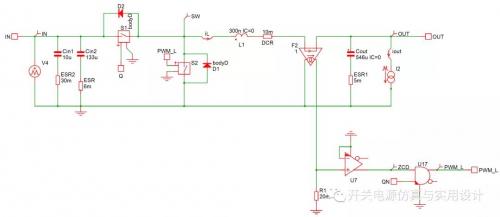

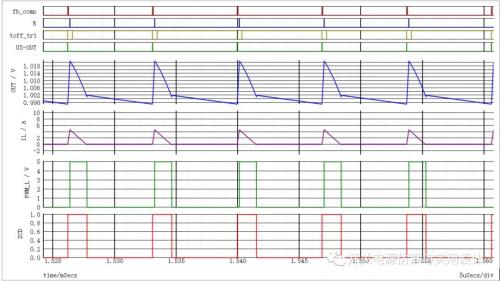

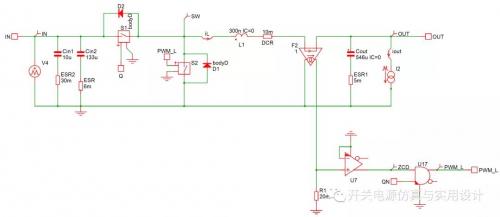

图 36ZCD 的基础模型

如图所示,直接用 CCCS 采样电感电流,输出侧串联一个电阻 R1,以便转换成电压。同样地,也可以直接使用 DCR 的两端电压值来作比较,更加省时省力。比较器 U7 直接将采样电压和 GND 比较,从而获得 ZCD 信号。

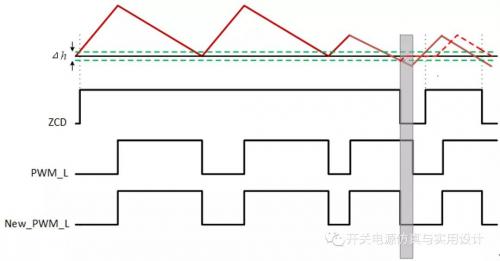

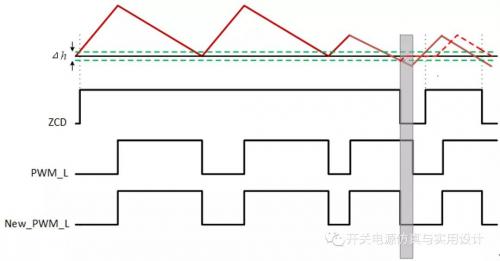

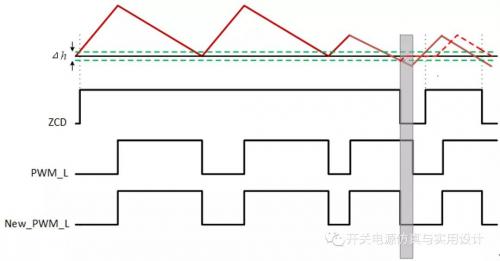

图 37 电感电流的 ZCD 控制逻辑

因为比较器都存在一个滞环值,因此当采样电压值比 GND 小 1/2 倍的滞环环宽时,才会触发 ZCD 拉低。原始的 PWM_L 信号不会在意电感电流过零,所以最直接的逻辑,将 ZCD 信号和原来的同步整流管的 PWM 信号 PWM_L 相与,新的同步整流管 PWM 信号 New_PWM_L 就可以在电感电流过零约 1/2 的滞环环宽时,及时关断同步整流管,电感电流会很快变为 0,进入标准的 DCM 模式。

当进入下一周期时,ZCD 信号会在电感电流大于 1/2 的滞环环宽时,拉高。PWM_L 信号一定是滞后的,不会影响 PWM_L 的上升沿,所以可以保证相与的逻辑正确性。同样地,当处在 CCM 模式下,ZCD 会一直保持高电平,同样对 PWM_L 没有影响。

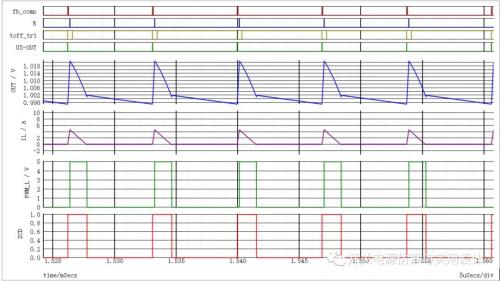

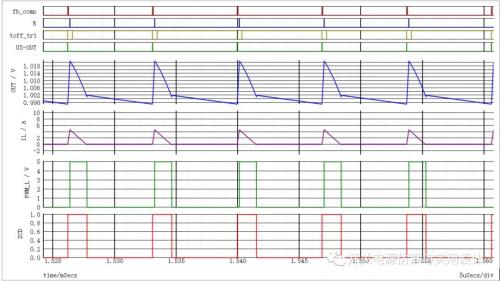

图 38 电感电流采样 ZCD

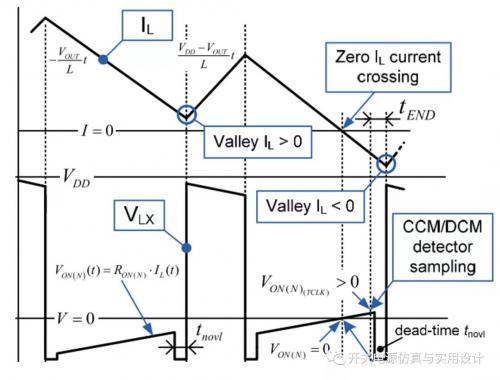

从上面的表述看来,逻辑简单清楚,然而完整电感电流的检测确实是有些难度。当然,也可以考虑之前 Part5 中的 DCR 检测方法,只是采样精度受到温度的影响,RC 时间常数也要很好的匹配,电感电流的过零点要求的精度还蛮高。从 IC 设计者的角度来看,当然是内部做电流采样最合适。在同步整流管开通时,采样同步整流管的管压降 Vdrop=Rdson*iL,当电感电流过零时,管压降也从负电压变为正电压,因此,可以用 Vdrop 跟 GND 比较获得 ZCD 逻辑信号。

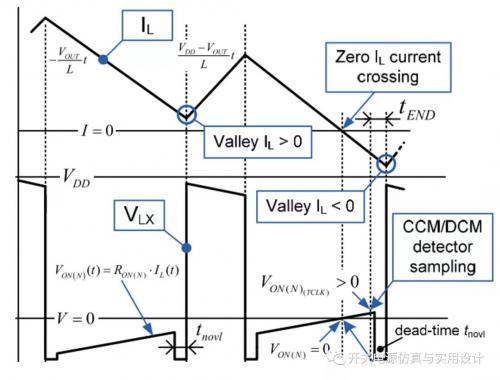

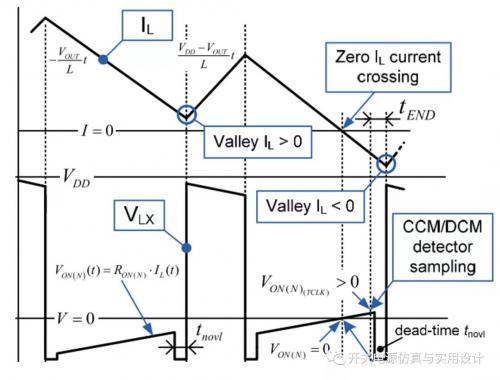

图 39 基于 Rdson 的过零检测

顺着上图的思路,同步整流管的 PWM 信号要在电感电流下降时开始,在 Vdrop 大于 0 时,翻转拉低。依然采用原始的 PWM_L 的信号与 ZCD 信号相与逻辑,此时需要注意,如果将 SW 电压和 GND 比较,在电感电流过零之前,ZCD 信号不可能像之前那样一直保持高。

因为 SW 电压在上管开通时,也会高于 GND,而且会引入高压到比较器中。

合理的方法是,在 PWM_L 的上升沿开始电感电流过零检测,此时 SW 电压刚刚度过死区时间,而死区时间内电压一直被二极管钳位在负电压。这足够保证,SW 电压此时一定是负电压。当 SW 电压大于 0 时,停止电感电流过零检测。

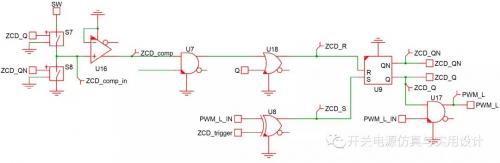

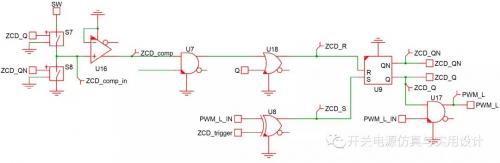

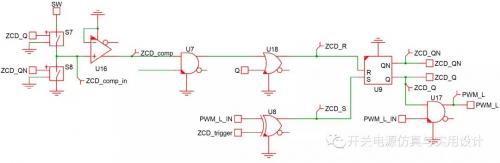

图 40 基于 Rdson 的 ZCD 过零检测逻辑

思路明确之后,利用 PWM_L 的上升沿做触发,ZCD_Q 拉高后,SW 开始被接入检测,当 SW 大于 0 时,ZCD_comp 信号会被拉高。ZCD_comp 拉高后,结束 SW 的检测,GND 被接入比较器 U16 的正端。但是 GND 和 GND 之间没有差值,所以 ZCD_comp 会一直拉高,所以需要在适当的时机由将其拉低,最好的时刻当然是在上管的 PWM 结束时刻。

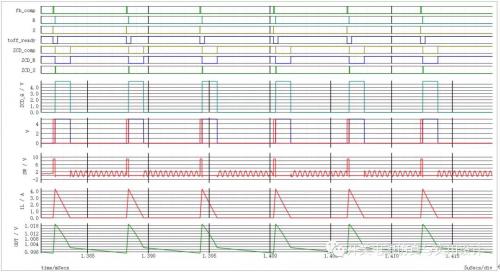

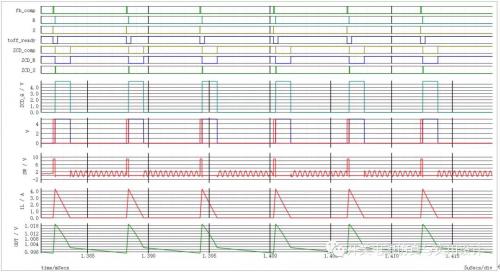

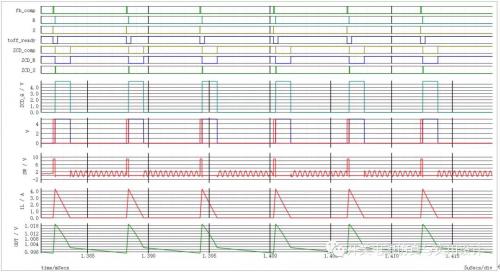

图 41 基于 Rdson 的 ZCD 检测仿真波形

仿真波形验证了上述的思路,根据上面的表述主要思想,应该还有更简洁的逻辑控制思路,无奈笔者除了 RS latch 和门电路用的较为熟练外,其他高级逻辑设计不是很会。因此,如果你有更好的逻辑设计,也可以一起讨论。

在 Part7 的仿真中,仅仅考虑了 CCM 模式以及 ESR 大大满足稳定性条件的情况。实际工况却更加复杂。我们知道,DCM 下 COT 控制模式可以提供较好的轻载效率,得益于 DCM 模式下,开关频率会降低,开关损耗会降低。跑过模型的朋友应该知道当负载电流降低到 0.5A 的时候,电感电流已经过零反向,进入了强制 CCM 模式(FCCM,Forced Continuous Conduction Mode),而并没有体现 DCM 频率降低时,带来的高轻载效率优势。

在强制 CCM 模式下,电感电流反向将会带来较大的损耗。如何及时地关断同步整流的下管 MOSFET?这就需要用到过零检测电路,当电感电流反向,但负电流还很小的时候关断下管MOSFET,让输出电容提供给负载能量。

先直接利用流控流源采样电感电流,获得过零点,以便说明基础的控制逻辑是怎样的。

图 36ZCD 的基础模型

如图所示,直接用 CCCS 采样电感电流,输出侧串联一个电阻 R1,以便转换成电压。同样地,也可以直接使用 DCR 的两端电压值来作比较,更加省时省力。比较器 U7 直接将采样电压和 GND 比较,从而获得 ZCD 信号。

图 37 电感电流的 ZCD 控制逻辑

因为比较器都存在一个滞环值,因此当采样电压值比 GND 小 1/2 倍的滞环环宽时,才会触发 ZCD 拉低。原始的 PWM_L 信号不会在意电感电流过零,所以最直接的逻辑,将 ZCD 信号和原来的同步整流管的 PWM 信号 PWM_L 相与,新的同步整流管 PWM 信号 New_PWM_L 就可以在电感电流过零约 1/2 的滞环环宽时,及时关断同步整流管,电感电流会很快变为 0,进入标准的 DCM 模式。

当进入下一周期时,ZCD 信号会在电感电流大于 1/2 的滞环环宽时,拉高。PWM_L 信号一定是滞后的,不会影响 PWM_L 的上升沿,所以可以保证相与的逻辑正确性。同样地,当处在 CCM 模式下,ZCD 会一直保持高电平,同样对 PWM_L 没有影响。

图 38 电感电流采样 ZCD

从上面的表述看来,逻辑简单清楚,然而完整电感电流的检测确实是有些难度。当然,也可以考虑之前 Part5 中的 DCR 检测方法,只是采样精度受到温度的影响,RC 时间常数也要很好的匹配,电感电流的过零点要求的精度还蛮高。从 IC 设计者的角度来看,当然是内部做电流采样最合适。在同步整流管开通时,采样同步整流管的管压降 Vdrop=Rdson*iL,当电感电流过零时,管压降也从负电压变为正电压,因此,可以用 Vdrop 跟 GND 比较获得 ZCD 逻辑信号。

图 39 基于 Rdson 的过零检测

顺着上图的思路,同步整流管的 PWM 信号要在电感电流下降时开始,在 Vdrop 大于 0 时,翻转拉低。依然采用原始的 PWM_L 的信号与 ZCD 信号相与逻辑,此时需要注意,如果将 SW 电压和 GND 比较,在电感电流过零之前,ZCD 信号不可能像之前那样一直保持高。

因为 SW 电压在上管开通时,也会高于 GND,而且会引入高压到比较器中。

合理的方法是,在 PWM_L 的上升沿开始电感电流过零检测,此时 SW 电压刚刚度过死区时间,而死区时间内电压一直被二极管钳位在负电压。这足够保证,SW 电压此时一定是负电压。当 SW 电压大于 0 时,停止电感电流过零检测。

图 40 基于 Rdson 的 ZCD 过零检测逻辑

思路明确之后,利用 PWM_L 的上升沿做触发,ZCD_Q 拉高后,SW 开始被接入检测,当 SW 大于 0 时,ZCD_comp 信号会被拉高。ZCD_comp 拉高后,结束 SW 的检测,GND 被接入比较器 U16 的正端。但是 GND 和 GND 之间没有差值,所以 ZCD_comp 会一直拉高,所以需要在适当的时机由将其拉低,最好的时刻当然是在上管的 PWM 结束时刻。

图 41 基于 Rdson 的 ZCD 检测仿真波形

仿真波形验证了上述的思路,根据上面的表述主要思想,应该还有更简洁的逻辑控制思路,无奈笔者除了 RS latch 和门电路用的较为熟练外,其他高级逻辑设计不是很会。因此,如果你有更好的逻辑设计,也可以一起讨论。

举报

举报

举报

举报