四、ESD、EOS 与缺陷诱发失效鉴别方法

4.1 失效背景调查

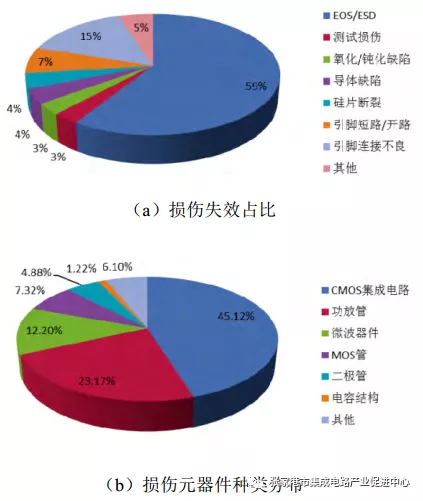

通常静电损伤发生具有一定的随机性和持续性,而 EOS 损伤发生的阶段可能具有一定规律性和可重复性。一般来说,EOS/ESD 不具有失效器件的批次性特征,而缺陷引起的失效通常具有一定的批次性特征,而且在“合格品”中可能同样存在潜在缺陷的迹象或趋势。因此需关注失效发生是否具备批次性特点。另外,需调查失效发生的阶段、周围工作场景等信息,通过失效背景信息区分三种失效是分析的辅助手段。

4.2 参数测试

通常,对失效样品需要进行参数测试,这些包括:端口 I/V 测试、静态电流、功能测试等,同时会利用同批次良品进行对比。对于静电损伤引起的失效,其参数测试结果往往与良品差异性小,而 EOS 损伤的测试结果则往往差异较明显。对于缺陷诱发的失效,则可能在大量良品测试中检测出潜在缺陷的样品。另外,怀疑静电损伤的失效,则应该针对良品开展静电敏感度等级评价测试,评估是否属于静电敏感类型器件,同时通过进一步解剖对比模拟失效的样品与失效样品之间的差异。

4.3 显微形貌观察和分析

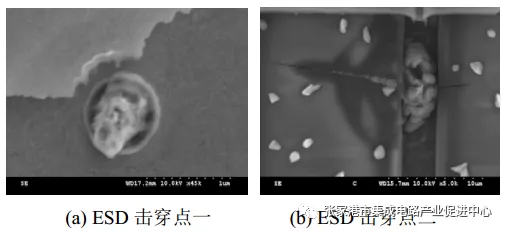

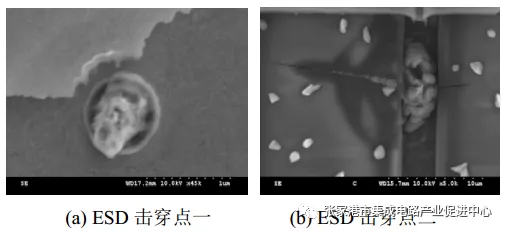

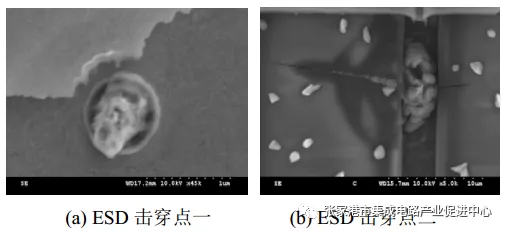

通过解剖样品,并且借助于失效定位手段:如光学显微观察、液晶分析法、光发射显微分析技术(EMMI)以及激光诱导电阻变化技术(OBIRCH)、磁显微分析以及聚焦离子束剖切(FIB)等方法定位到失效点,然后直接观察失效的微观物理形貌特征,是鉴别三种失效类型最直观的方式,也是最需要经验的一个环节。通常,从损伤后的物理微观形貌来看,静电损伤形貌通常比较轻微,损伤区域小,损伤点尺寸通常为微米级,或者仅有轻微损伤痕迹,相对于 EOS 损伤来说要轻微一些。图 3 给出了典型的 ESD 击穿形貌照片。对于 CMOS 集成电路而言,多数发生在电极或扩散区之间,往往有明显的指向性。有时也会伴有金属化损伤,但相对于 EOS 损伤来说,损伤区域及尺寸小,不会像 EOS 损伤那样有较大面积的金属化熔融和烧毁的特征。而缺陷诱发的失效,往往具有失效部位和类型单一,且“合格品”中也可能存在类似缺陷。总的来说,ESD 失效是 EOS 失效的一部分,二者之间没有明显分界,目前在国际上也没有很好的方法将二者完全区分开来。在对失效样品进行判别分析时,要采用上述三种方法进行综合分析,才能得到较为准确的判断。

图 3 静电击穿典型形貌

4.4 典型分析案例

(1)样品描述:样品为某型号双向收发器,陶瓷密封封装,装板后测试发现功能失效。共有 2 只失效样品(F1#、F2#),良品若干。

(2)背景调查:器件在装板后测试发现功能失效(无法收发数据),排查测试过程异常电应力,未发现异常,怀疑静电损伤。

(3)非破坏性分析:失效品外观未见机械损伤、密封区开裂、过电或腐蚀痕迹、引脚残留焊料。进行 X-Ray 观察,均未见明显异常。对失效品进行端口特性测试,发现失效样品的功能引脚 Pin30(2A5)对地呈现漏电特性。

(4)显微形貌观察:将 F1#、F2#样品机械开封,内部芯片表面未见明显机械损伤、过电损伤和脏污腐蚀变色等异常形貌。光发射扫描显微镜定位(OBIRCH 模式)发现失效芯片上 Pin30 键合附近存在异常亮点,该点在激光扫描下,阻值发生变化,光发射显微镜探测到该阻抗变化,并标记颜色。而对正常引脚 Pin33(2A3)用此方法测试则无亮点。将失效品芯片去层并进行扫描电镜观察,可以观察到两只芯片相同位置的保护管处存在击穿熔坑,但击穿点尺寸都较小(约 1μm)。

(5)静电防护能力诊断:对装配生产线进行现场诊断,发现作业过程中大量使用绝缘类包装材料,且无有效的静电防护措施。另一方面,查阅该器件规格书可知该器件的静电敏感电压(HBM 模型)为 1000 V,属于静电敏感器件。

(6)综合分析:失效样品芯片表面无明显异常,光发射定位后发现端口保护网络击穿失效,呈现为小能量击穿,综合背景调查和现场诊断结果综合判断为静电放电损伤引起。图 4 是该失效分析案例的典型照片。

图 4 ESD 损伤失效分析典型形貌

五、结论

在军工、航空航天、通信、智能家电、电力电子、医疗电子以及轨道交通等领域电子产品中大量使用静电敏感器件,静电放电造成的损失不容忽视。

四、ESD、EOS 与缺陷诱发失效鉴别方法

4.1 失效背景调查

通常静电损伤发生具有一定的随机性和持续性,而 EOS 损伤发生的阶段可能具有一定规律性和可重复性。一般来说,EOS/ESD 不具有失效器件的批次性特征,而缺陷引起的失效通常具有一定的批次性特征,而且在“合格品”中可能同样存在潜在缺陷的迹象或趋势。因此需关注失效发生是否具备批次性特点。另外,需调查失效发生的阶段、周围工作场景等信息,通过失效背景信息区分三种失效是分析的辅助手段。

4.2 参数测试

通常,对失效样品需要进行参数测试,这些包括:端口 I/V 测试、静态电流、功能测试等,同时会利用同批次良品进行对比。对于静电损伤引起的失效,其参数测试结果往往与良品差异性小,而 EOS 损伤的测试结果则往往差异较明显。对于缺陷诱发的失效,则可能在大量良品测试中检测出潜在缺陷的样品。另外,怀疑静电损伤的失效,则应该针对良品开展静电敏感度等级评价测试,评估是否属于静电敏感类型器件,同时通过进一步解剖对比模拟失效的样品与失效样品之间的差异。

4.3 显微形貌观察和分析

通过解剖样品,并且借助于失效定位手段:如光学显微观察、液晶分析法、光发射显微分析技术(EMMI)以及激光诱导电阻变化技术(OBIRCH)、磁显微分析以及聚焦离子束剖切(FIB)等方法定位到失效点,然后直接观察失效的微观物理形貌特征,是鉴别三种失效类型最直观的方式,也是最需要经验的一个环节。通常,从损伤后的物理微观形貌来看,静电损伤形貌通常比较轻微,损伤区域小,损伤点尺寸通常为微米级,或者仅有轻微损伤痕迹,相对于 EOS 损伤来说要轻微一些。图 3 给出了典型的 ESD 击穿形貌照片。对于 CMOS 集成电路而言,多数发生在电极或扩散区之间,往往有明显的指向性。有时也会伴有金属化损伤,但相对于 EOS 损伤来说,损伤区域及尺寸小,不会像 EOS 损伤那样有较大面积的金属化熔融和烧毁的特征。而缺陷诱发的失效,往往具有失效部位和类型单一,且“合格品”中也可能存在类似缺陷。总的来说,ESD 失效是 EOS 失效的一部分,二者之间没有明显分界,目前在国际上也没有很好的方法将二者完全区分开来。在对失效样品进行判别分析时,要采用上述三种方法进行综合分析,才能得到较为准确的判断。

图 3 静电击穿典型形貌

4.4 典型分析案例

(1)样品描述:样品为某型号双向收发器,陶瓷密封封装,装板后测试发现功能失效。共有 2 只失效样品(F1#、F2#),良品若干。

(2)背景调查:器件在装板后测试发现功能失效(无法收发数据),排查测试过程异常电应力,未发现异常,怀疑静电损伤。

(3)非破坏性分析:失效品外观未见机械损伤、密封区开裂、过电或腐蚀痕迹、引脚残留焊料。进行 X-Ray 观察,均未见明显异常。对失效品进行端口特性测试,发现失效样品的功能引脚 Pin30(2A5)对地呈现漏电特性。

(4)显微形貌观察:将 F1#、F2#样品机械开封,内部芯片表面未见明显机械损伤、过电损伤和脏污腐蚀变色等异常形貌。光发射扫描显微镜定位(OBIRCH 模式)发现失效芯片上 Pin30 键合附近存在异常亮点,该点在激光扫描下,阻值发生变化,光发射显微镜探测到该阻抗变化,并标记颜色。而对正常引脚 Pin33(2A3)用此方法测试则无亮点。将失效品芯片去层并进行扫描电镜观察,可以观察到两只芯片相同位置的保护管处存在击穿熔坑,但击穿点尺寸都较小(约 1μm)。

(5)静电防护能力诊断:对装配生产线进行现场诊断,发现作业过程中大量使用绝缘类包装材料,且无有效的静电防护措施。另一方面,查阅该器件规格书可知该器件的静电敏感电压(HBM 模型)为 1000 V,属于静电敏感器件。

(6)综合分析:失效样品芯片表面无明显异常,光发射定位后发现端口保护网络击穿失效,呈现为小能量击穿,综合背景调查和现场诊断结果综合判断为静电放电损伤引起。图 4 是该失效分析案例的典型照片。

图 4 ESD 损伤失效分析典型形貌

五、结论

在军工、航空航天、通信、智能家电、电力电子、医疗电子以及轨道交通等领域电子产品中大量使用静电敏感器件,静电放电造成的损失不容忽视。

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报