去耦电容类型

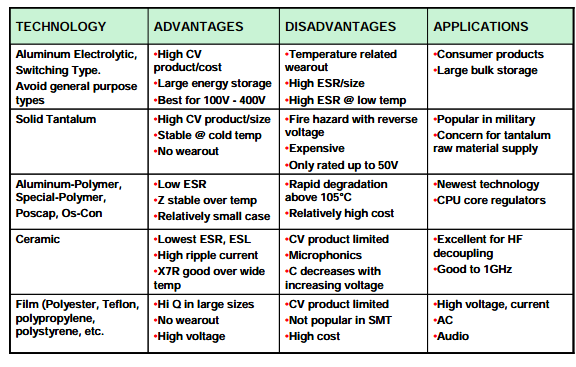

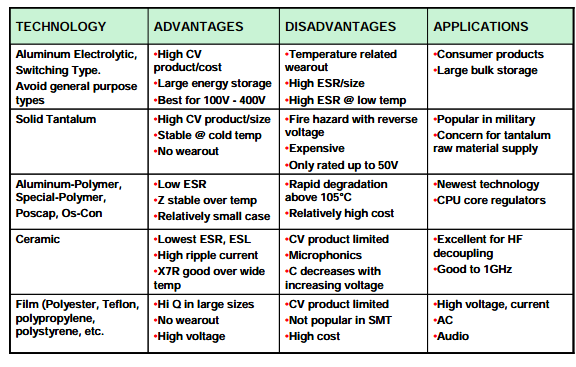

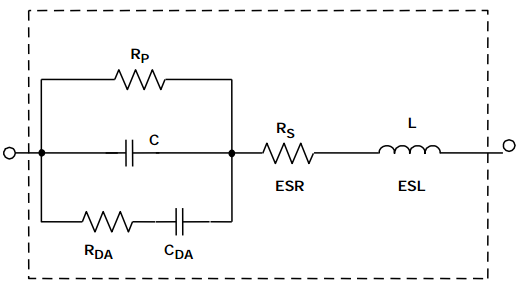

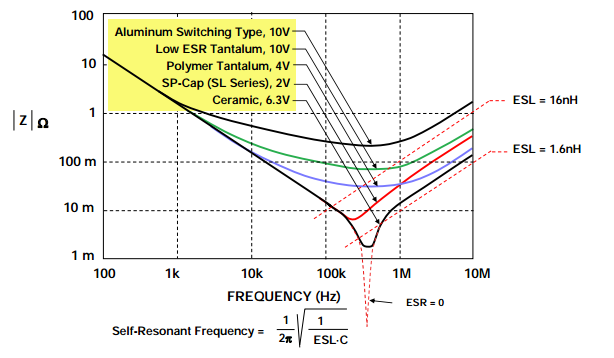

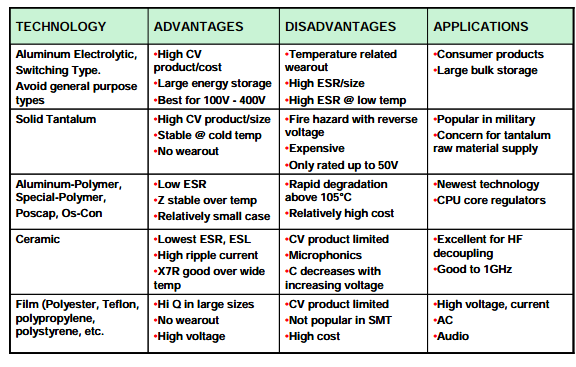

图 5 显示适合去耦的各种常见电容类型。电解系列具有宽值范围、高电容体积比和广泛的工作电压,是极佳的高性价比低频滤波器元件。它包括通用铝电解开关类型,提供 10 V 以下直至约 500 V 的工作电压,尺寸为 1 μF 至数千μF(以及成比例的外形尺寸)。

图 5:常见电容类型

所有电解电容均有极性,因此无法耐受约一伏以上的反向偏置电压而不造成损坏。此类器件具有相对较高的泄漏电流(可能为数十μA),很大程度上取决于特定系列的设计、电气尺寸、额定电压及施加电压。不过,泄漏电流不可能是基本去耦应用的主要因素。

大多数去耦应用不建议使用“通用”铝电解电容。不过,铝电解电容的一个子集是“开关型”,设计并规定用于在最高达数百 kHz 的频率下处理高脉冲电流,且仅具有低损耗。此类电容在高频滤波应用中可直接媲美固态钽电容,且具有更广泛的可用值。

固态钽电解电容一般限于 50 V 或更低的电压,电容为 500 μF 或更低。对于给定尺寸,钽电容比铝开关电解电容呈现出更高的电容体积比,且具有更高的频率范围和更低的 ESR。一般也比铝电解电容更昂贵,对于浪涌和纹波电流,必须谨慎处理应用。

最近,使用有机或聚合物电解质的高性能铝电解电容也已问世。这些电容系列拥有略低于其他电解类型的 ESR 和更高的频率范围,另外低温 ESR 下降也最小。此类器件使用铝聚合物、特殊聚合物、Poscap 和 Os-Con 等标签。

陶瓷或多层陶瓷(MLCC)具有尺寸紧凑和低损耗特性,通常是数 MHz 以上的首选电容材料。不过,陶瓷电介质特性相差很大。对于电源去耦应用,一些类型优于其他类型。在 X7R 的高 K 电介质公式中,陶瓷电介质电容的值最高可达数μF。在高达 200 V 的额定电压下推荐 Z5U 和 Y5V。X7R 型在直流偏置电压下的电容变化小于 Z5U 和 Y5V 型,因此是较佳选择。

NP0(也称为 COG)型使用更低的介电常数公式,通常具有零 TC 和低电压系数(不同于较不稳定的高 K 型)。NP0 型的可用值限于 0.1 μF 或更低,0.01 μF 是更实用的上限值。

多层陶瓷(MLCC)表面贴装电容的极低电感设计可提供近乎最佳的 RF 旁路,因此越来越频繁地用于 10 MHz 或更高频率下的旁路和滤波。更小的陶瓷芯片电容工作频率范围可达 1 GHz。对于高频应用中的这些及其他电容,可通过选择自谐振频率高于最高目标频率的电容,确保有效值。

薄膜型电容一般使用绕线,增加了电感,因此不适合电源去耦应用。此类型更常用于音频应用,此时需要极低电容和电压系数。

局部高频去耦建议

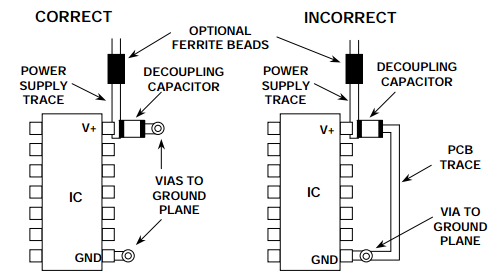

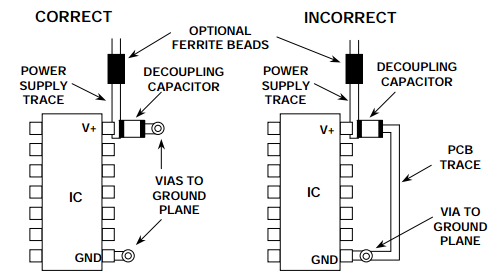

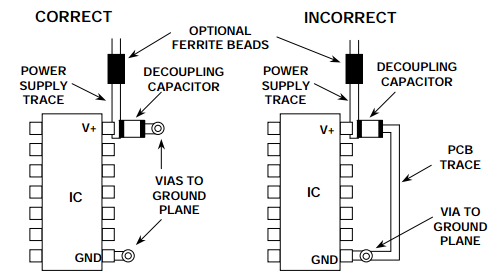

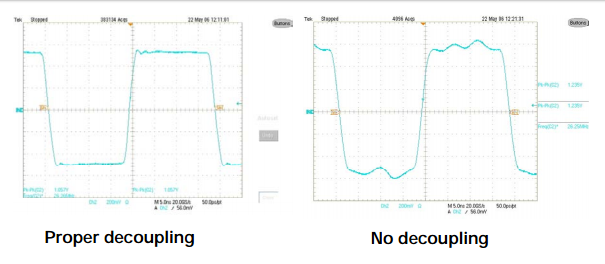

图 6 显示了高频去耦电容必须尽可能靠近芯片的情况。否则,连接走线的电感将对去耦的有效性产生不利影响。

图 6:高频电源滤波器需要通过较短的低电感路径(接地层)去耦

左图中,电源引脚和接地连接尽可能短,所以是最有效的配置。然而右图中,PCB 走线内的额外电感和电阻将造成去耦方案的有效性降低,且增加封闭环路可能造成干扰问题。

由 LC 去耦网络构成的谐振电路

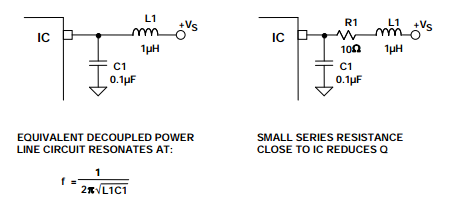

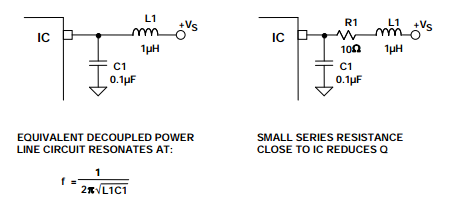

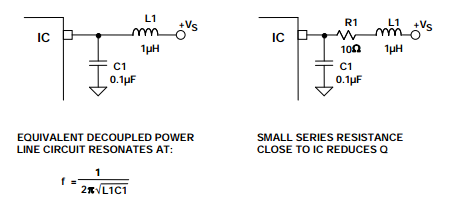

许多去耦应用中,电感或铁氧体磁珠与去耦电容串联,如图 7 所示。电感 L 与去耦电容 C 串联后构成谐振或“调谐”电路,主要特性是显示谐振频率下的显著阻抗变化。谐振频率计算公式如下:

图 7:由电源线路去耦构成的谐振电路

去耦网络的总体阻抗在谐振频率下可表现出峰化现象。峰化程度取决于调谐电路的相对 Q(品质因子)值。谐振电路的 Q 衡量其对电阻的电抗。计算公式如下:

正常走线电感和 0.01 μF 至 0.1 μF 的典型去耦电容将在高于数 MHz 的频率下产生谐振。例如,0.1 μF 和 1 nH 将在 16 MHz 下产生谐振。

不过,由 100 μF 电容和 1 μF 电感组成的去耦网络在 16 kHz 下产生谐振。如果不予检查,一旦此频率出现在电源线路上,可带来谐振问题。该效应可通过降低电路 Q 降至最低。在电源线路内靠近 IC 的地方插入小电阻(~10 Ω)便可轻松完成,如右例所示。电阻应尽可能压低,最大程度地减小电阻两端的 IR 压降。也可用小铁氧体磁珠替代电阻,它在谐振频率下主要表现为阻性。

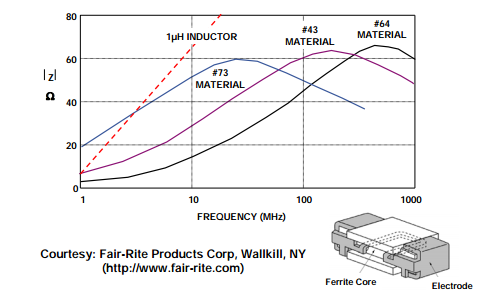

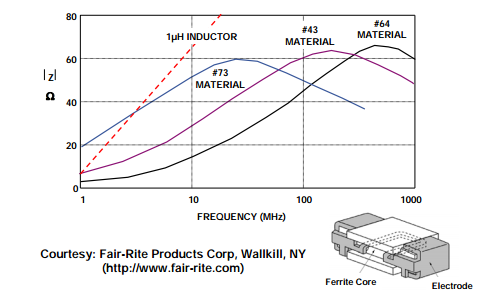

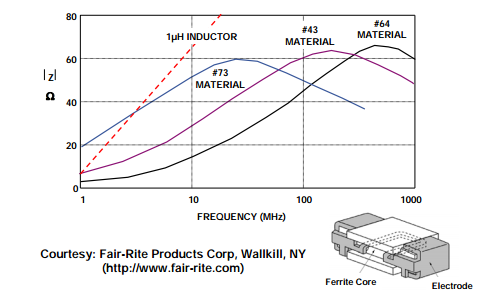

使用铁氧体磁珠代替电感可以减少谐振问题,因为铁氧体磁珠在 100 kHz 以上表现为阻性,所以会降低电路的有效 Q 值。典型铁氧体磁珠阻抗如图 8 所示。

图 8:铁氧体磁珠阻抗与 1μH 电感的比较

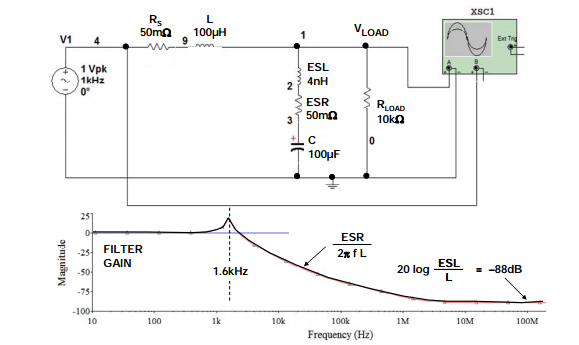

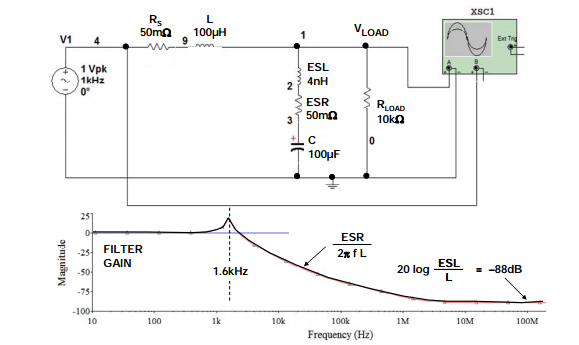

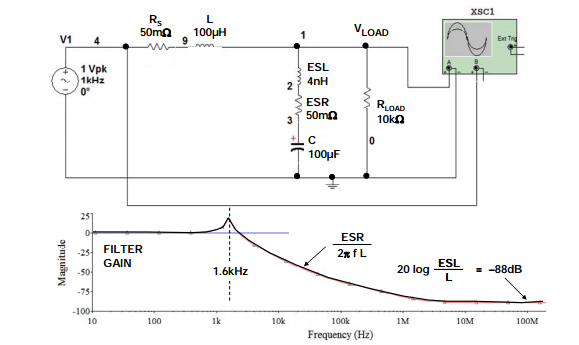

简单 LRC 去耦网络的响应可以使用基于 SPICE 的程序轻松仿真,例如 National InstrumentsMultisim™,ADI 公司版。典型电路模型如图 9 所示,仿真响应如图 10 所示。

图 9:LC 滤波器衰减近似值

图 10:使用 NI Multisim™ Analog Devices®版仿真 LC 网络增益

去耦电容类型

图 5 显示适合去耦的各种常见电容类型。电解系列具有宽值范围、高电容体积比和广泛的工作电压,是极佳的高性价比低频滤波器元件。它包括通用铝电解开关类型,提供 10 V 以下直至约 500 V 的工作电压,尺寸为 1 μF 至数千μF(以及成比例的外形尺寸)。

图 5:常见电容类型

所有电解电容均有极性,因此无法耐受约一伏以上的反向偏置电压而不造成损坏。此类器件具有相对较高的泄漏电流(可能为数十μA),很大程度上取决于特定系列的设计、电气尺寸、额定电压及施加电压。不过,泄漏电流不可能是基本去耦应用的主要因素。

大多数去耦应用不建议使用“通用”铝电解电容。不过,铝电解电容的一个子集是“开关型”,设计并规定用于在最高达数百 kHz 的频率下处理高脉冲电流,且仅具有低损耗。此类电容在高频滤波应用中可直接媲美固态钽电容,且具有更广泛的可用值。

固态钽电解电容一般限于 50 V 或更低的电压,电容为 500 μF 或更低。对于给定尺寸,钽电容比铝开关电解电容呈现出更高的电容体积比,且具有更高的频率范围和更低的 ESR。一般也比铝电解电容更昂贵,对于浪涌和纹波电流,必须谨慎处理应用。

最近,使用有机或聚合物电解质的高性能铝电解电容也已问世。这些电容系列拥有略低于其他电解类型的 ESR 和更高的频率范围,另外低温 ESR 下降也最小。此类器件使用铝聚合物、特殊聚合物、Poscap 和 Os-Con 等标签。

陶瓷或多层陶瓷(MLCC)具有尺寸紧凑和低损耗特性,通常是数 MHz 以上的首选电容材料。不过,陶瓷电介质特性相差很大。对于电源去耦应用,一些类型优于其他类型。在 X7R 的高 K 电介质公式中,陶瓷电介质电容的值最高可达数μF。在高达 200 V 的额定电压下推荐 Z5U 和 Y5V。X7R 型在直流偏置电压下的电容变化小于 Z5U 和 Y5V 型,因此是较佳选择。

NP0(也称为 COG)型使用更低的介电常数公式,通常具有零 TC 和低电压系数(不同于较不稳定的高 K 型)。NP0 型的可用值限于 0.1 μF 或更低,0.01 μF 是更实用的上限值。

多层陶瓷(MLCC)表面贴装电容的极低电感设计可提供近乎最佳的 RF 旁路,因此越来越频繁地用于 10 MHz 或更高频率下的旁路和滤波。更小的陶瓷芯片电容工作频率范围可达 1 GHz。对于高频应用中的这些及其他电容,可通过选择自谐振频率高于最高目标频率的电容,确保有效值。

薄膜型电容一般使用绕线,增加了电感,因此不适合电源去耦应用。此类型更常用于音频应用,此时需要极低电容和电压系数。

局部高频去耦建议

图 6 显示了高频去耦电容必须尽可能靠近芯片的情况。否则,连接走线的电感将对去耦的有效性产生不利影响。

图 6:高频电源滤波器需要通过较短的低电感路径(接地层)去耦

左图中,电源引脚和接地连接尽可能短,所以是最有效的配置。然而右图中,PCB 走线内的额外电感和电阻将造成去耦方案的有效性降低,且增加封闭环路可能造成干扰问题。

由 LC 去耦网络构成的谐振电路

许多去耦应用中,电感或铁氧体磁珠与去耦电容串联,如图 7 所示。电感 L 与去耦电容 C 串联后构成谐振或“调谐”电路,主要特性是显示谐振频率下的显著阻抗变化。谐振频率计算公式如下:

图 7:由电源线路去耦构成的谐振电路

去耦网络的总体阻抗在谐振频率下可表现出峰化现象。峰化程度取决于调谐电路的相对 Q(品质因子)值。谐振电路的 Q 衡量其对电阻的电抗。计算公式如下:

正常走线电感和 0.01 μF 至 0.1 μF 的典型去耦电容将在高于数 MHz 的频率下产生谐振。例如,0.1 μF 和 1 nH 将在 16 MHz 下产生谐振。

不过,由 100 μF 电容和 1 μF 电感组成的去耦网络在 16 kHz 下产生谐振。如果不予检查,一旦此频率出现在电源线路上,可带来谐振问题。该效应可通过降低电路 Q 降至最低。在电源线路内靠近 IC 的地方插入小电阻(~10 Ω)便可轻松完成,如右例所示。电阻应尽可能压低,最大程度地减小电阻两端的 IR 压降。也可用小铁氧体磁珠替代电阻,它在谐振频率下主要表现为阻性。

使用铁氧体磁珠代替电感可以减少谐振问题,因为铁氧体磁珠在 100 kHz 以上表现为阻性,所以会降低电路的有效 Q 值。典型铁氧体磁珠阻抗如图 8 所示。

图 8:铁氧体磁珠阻抗与 1μH 电感的比较

简单 LRC 去耦网络的响应可以使用基于 SPICE 的程序轻松仿真,例如 National InstrumentsMultisim™,ADI 公司版。典型电路模型如图 9 所示,仿真响应如图 10 所示。

图 9:LC 滤波器衰减近似值

图 10:使用 NI Multisim™ Analog Devices®版仿真 LC 网络增益

举报

举报

举报

举报

举报

举报

举报

举报