硬件加速应用程序开发流程:

对于基于FPGA的加速,Vitis核心开发套件支持用户通过API函数创建软件应用程序,例如OpenCL函数,在Alveo加速卡上运行加速硬核。Vitis核心开发套件也支持将软件程序运行在基于Linux的嵌入式处理器平台上,例如ZYNQ的UltraScale+MPSOC设备。对于嵌入式处理器平台Vitis开发套件执行模型也通过OpenCL API和基于Linux的Xilinx运行库(XRT)来调度硬核和控制数据的搬移。(加速库和xilinx运行库在GitHub上可下载)

Vitis核心开发套件可支持Alveo U50、U200、U250、U280加速卡,也支持zcu102、zcu104、zc702、zc706嵌入式处理器平台。除了以上比较流行的平台外,同时也支持自定义平台。

Vitis软件平台允许用户将数据中心应用程序移植到嵌入式平台上。Vitis核心开发套件不仅具有适用于硬核的V++编译器。也具有运行在X86主机的g++编译器和运行在Xilinx设备的嵌入式处理器的Arm编译器

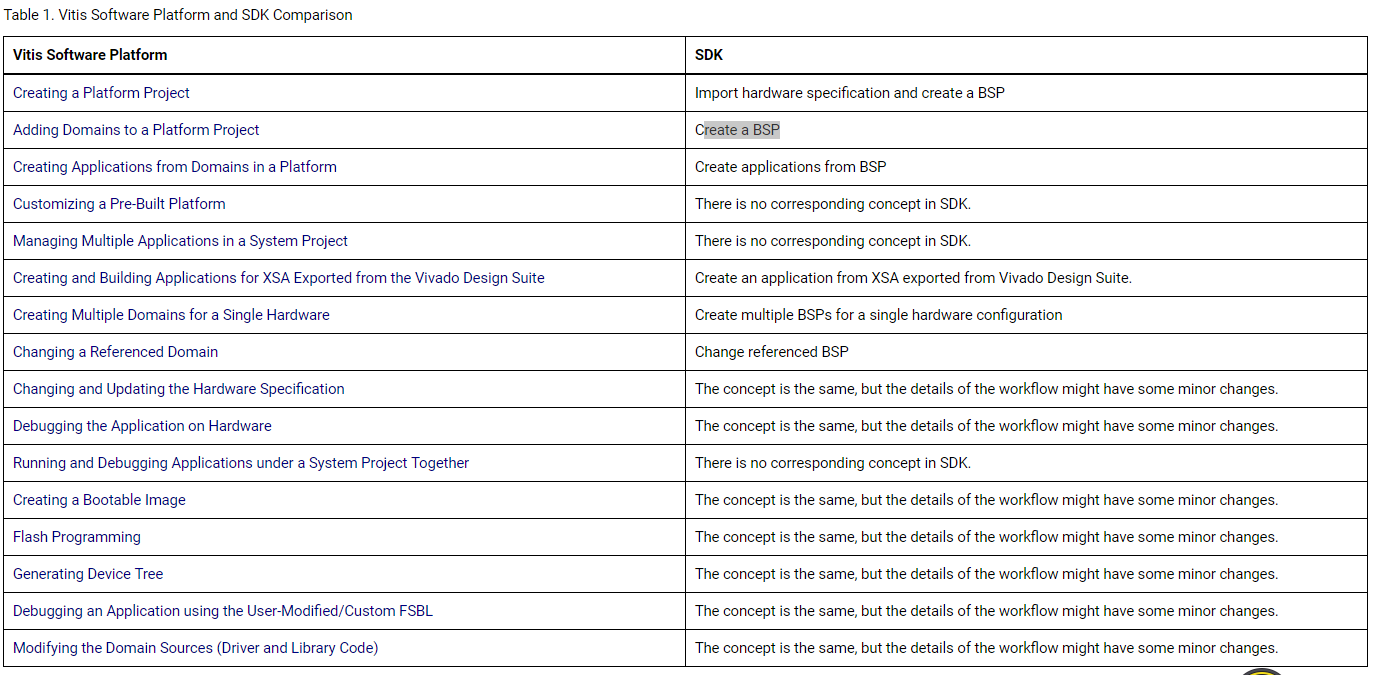

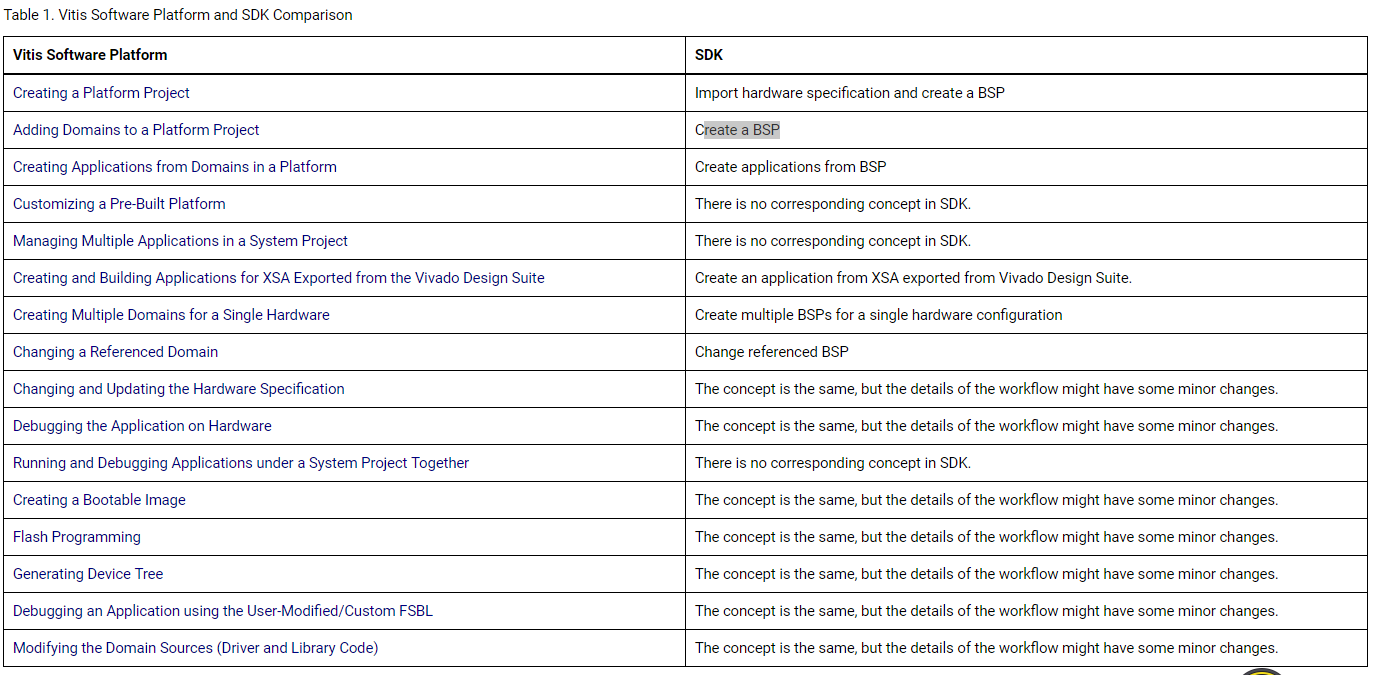

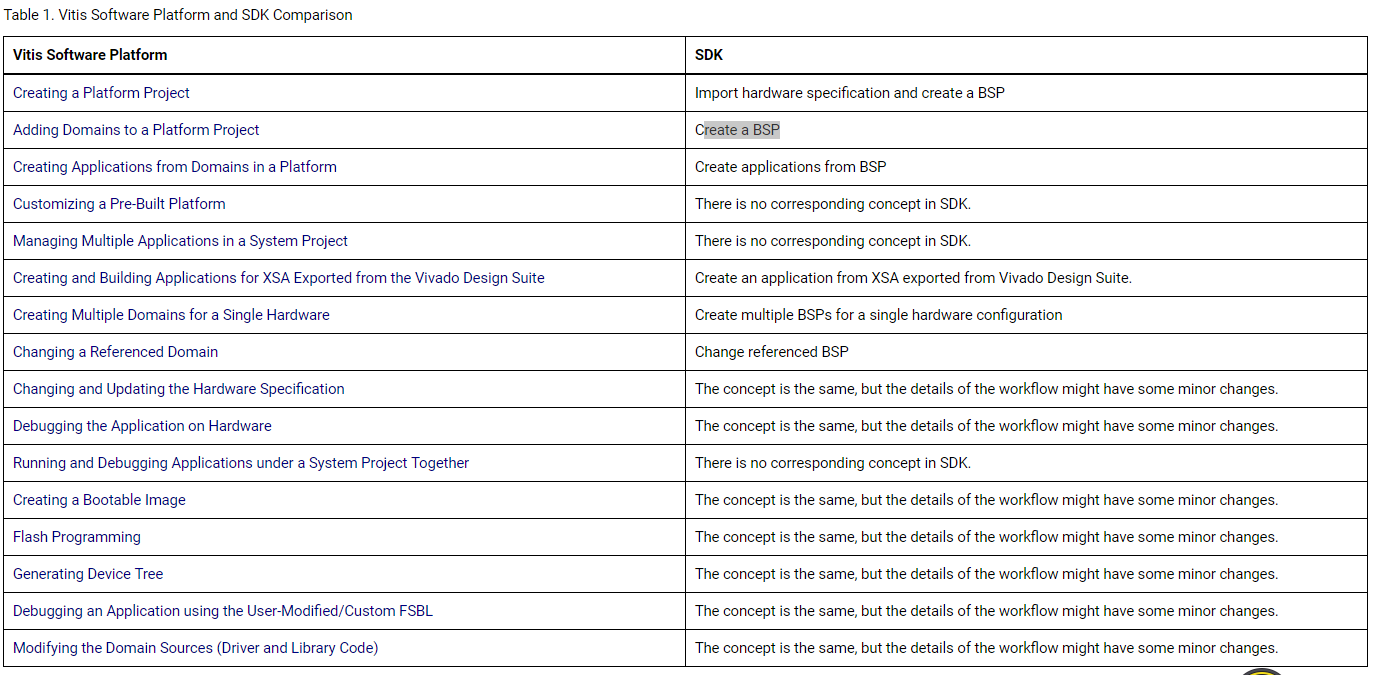

Vitis与SDK对比:

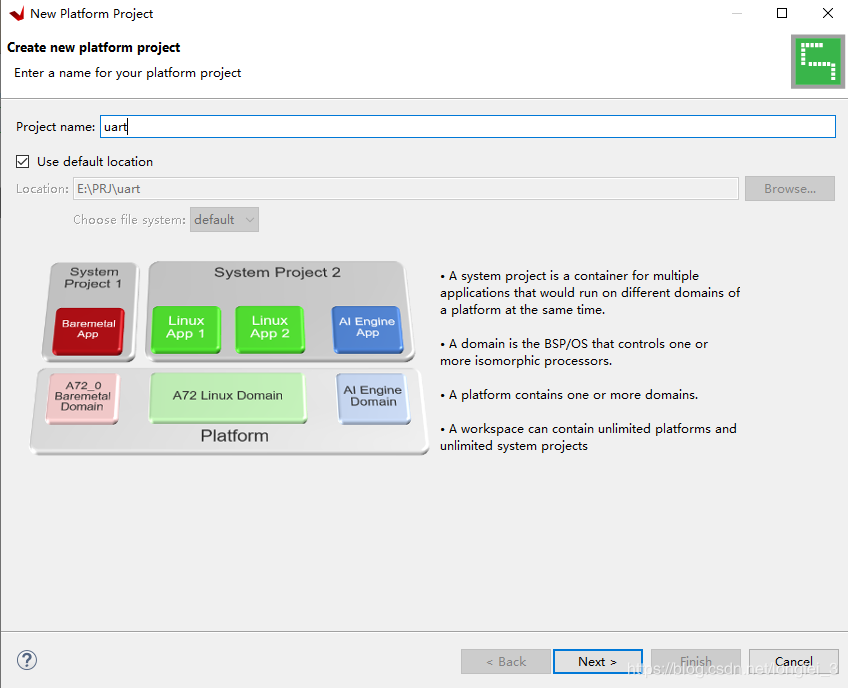

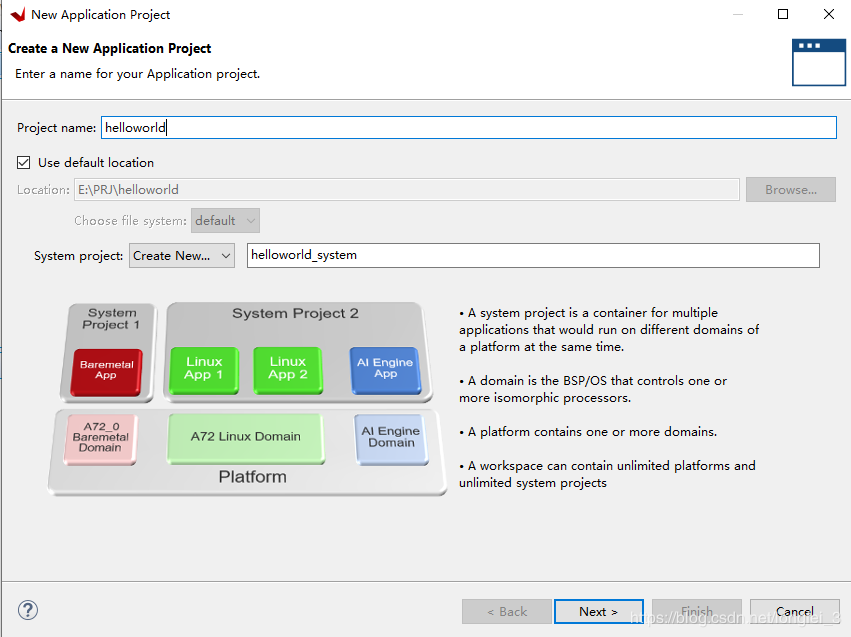

系统项目指的是什么?域domain可以理解成SDK中的BSP么?

系统项目就是指在Vitis中创建的application。

Vitis软件平台SDK

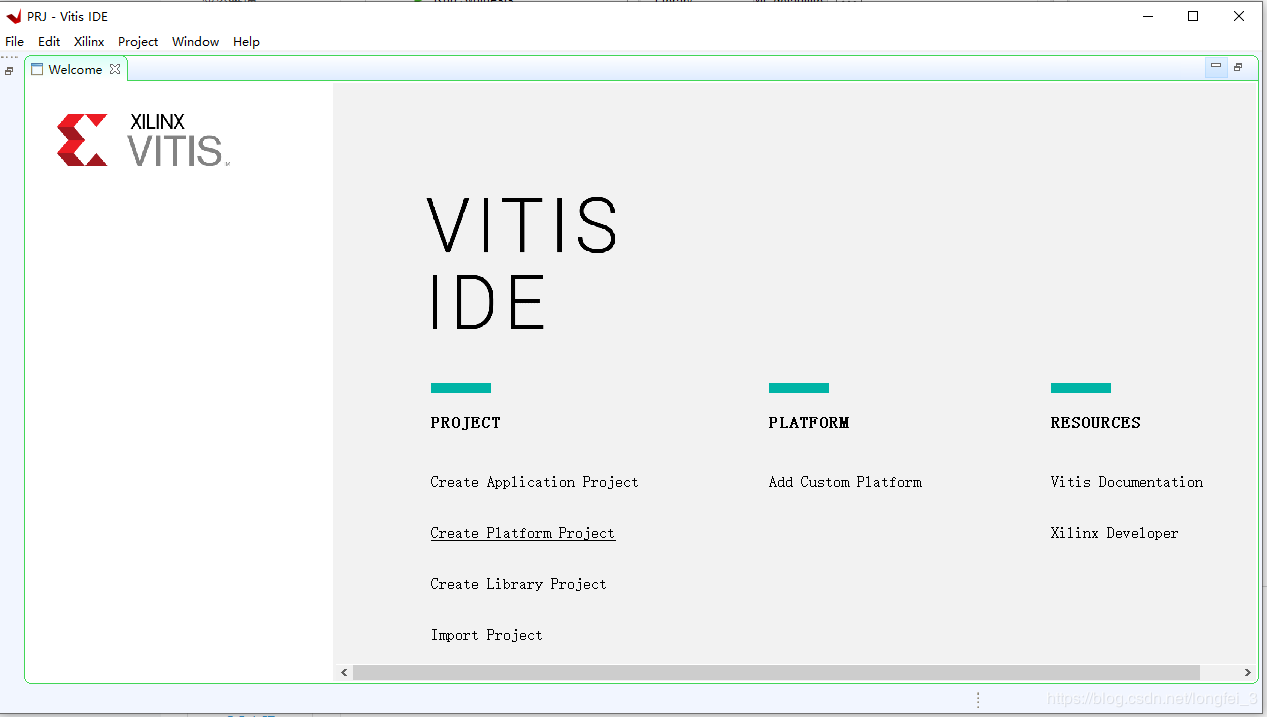

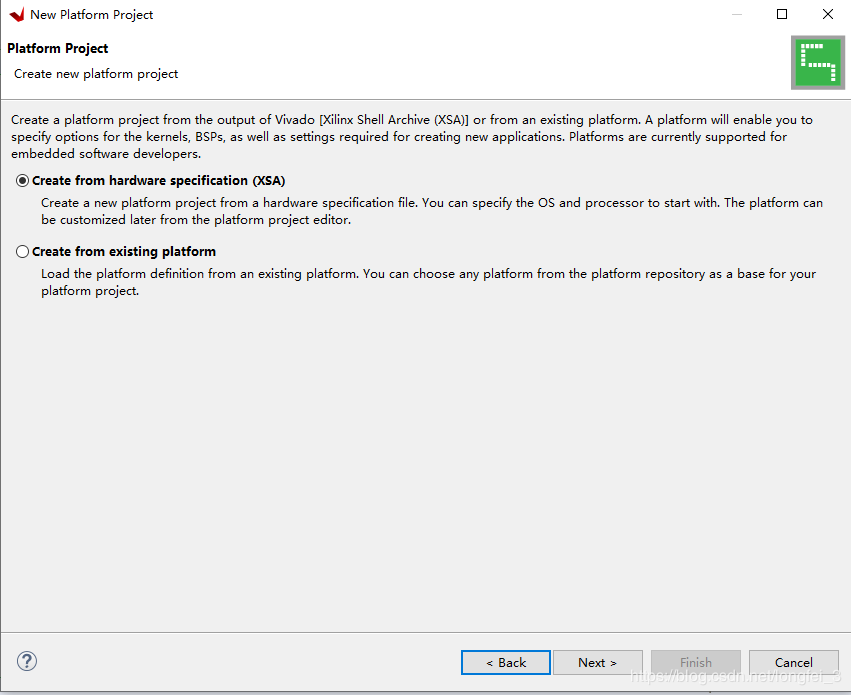

可在Vitis中直接创建一个平台项目(需要添加vivado生成的XSA文件或者从平台库中添加任意平台作为基础例如vck190.xsa、zc702.xsa、zc706.xsa、zcu102.xsa、zed.xsa)SDK是从vivado工程中导出硬件平台项目

为平台添加域创建BSP

创建应用程序(通过平台的域)创建应用程序(通过BSP)

改制一个预置平台无提及

可在一个系统项目中管理多个应用程序无提及

修改并且更新硬件基本相同,工作流程可能有细微改变

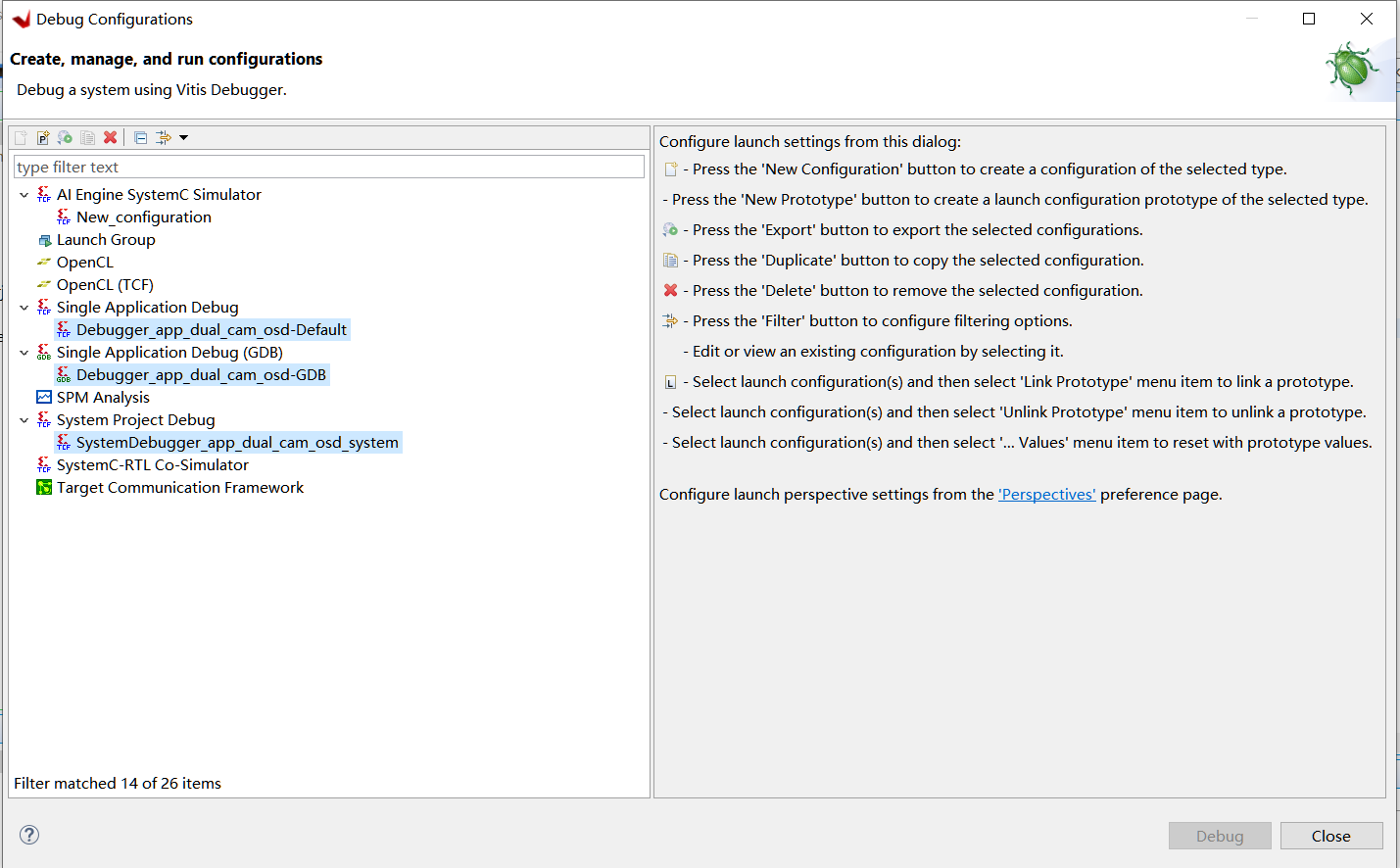

在硬件上调试应用程序基本相同,工作流程可能有细微改变

在一个系统项目下运行和调试应用程序无提及

创建boot image基本相同,工作流程可能有细微改变

Flash 编程基本相同,工作流程可能有细微改变

生成设备树基本相同,工作流程可能有细微改变

通过User-Modify/Custom FSBL测试应用程序基本相同,工作流程可能有细微改变

修改域源文件基本相同,工作流程可能有细微改变

实测Vitis编译时间要比SDK编译时间略长;

Vitis实现简单的HelloWord

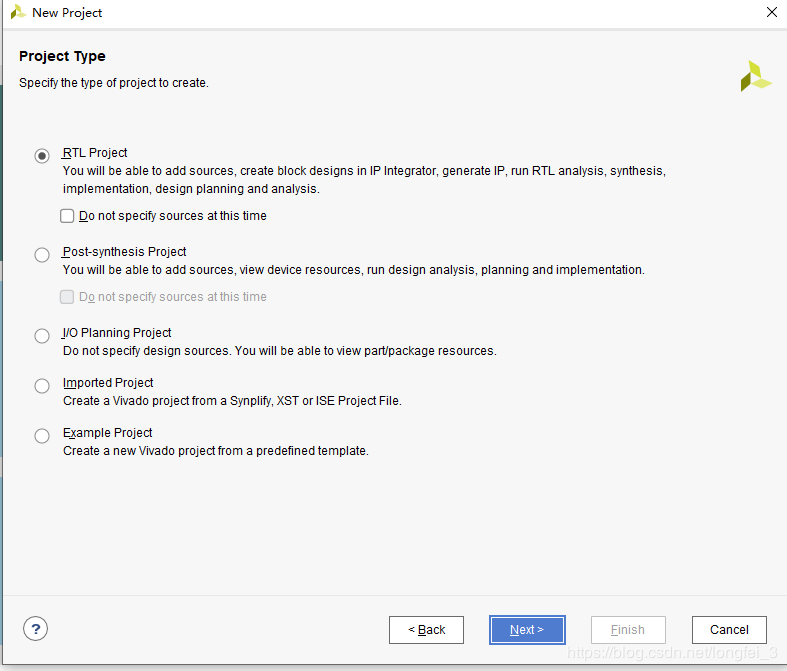

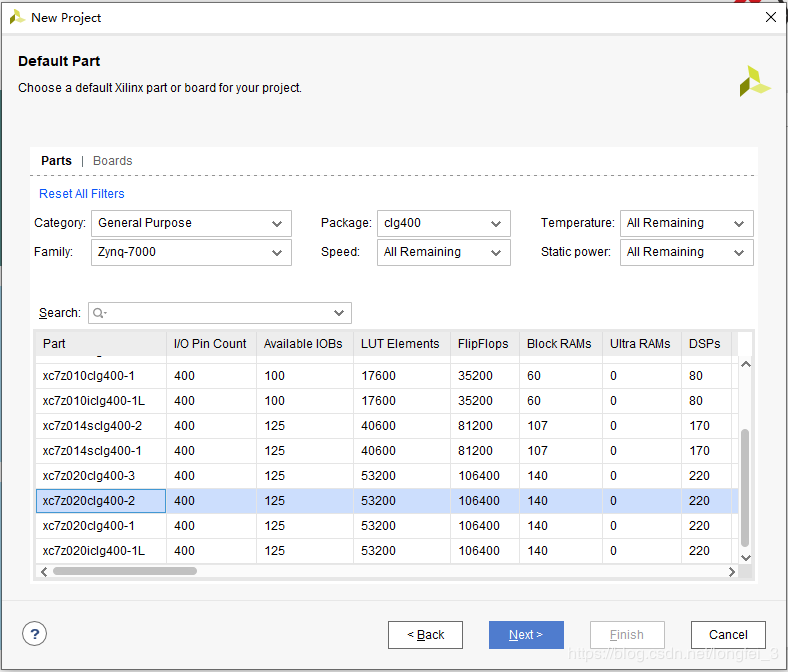

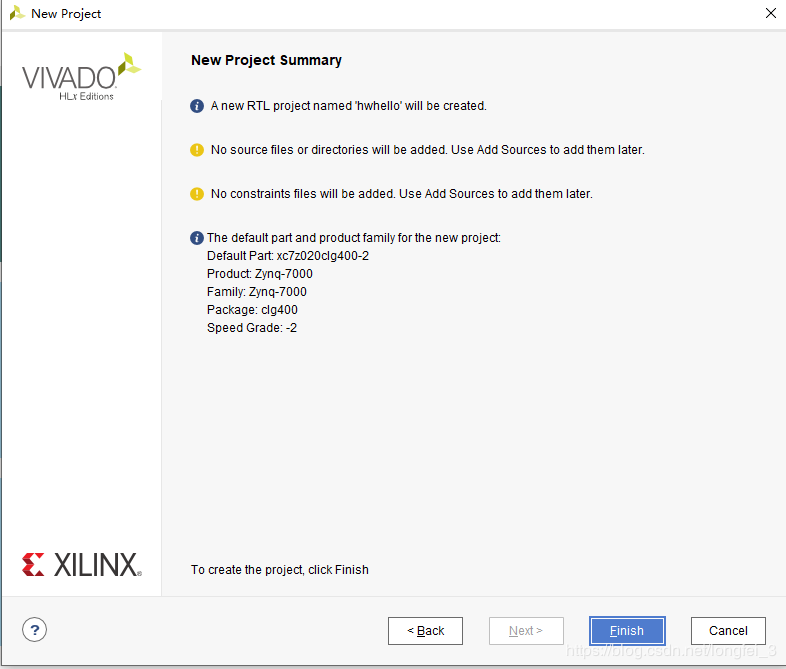

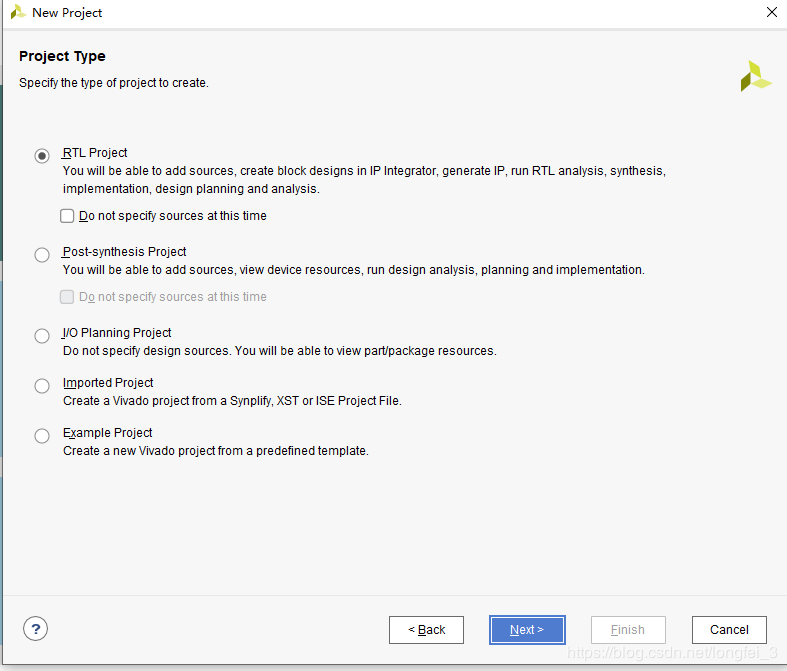

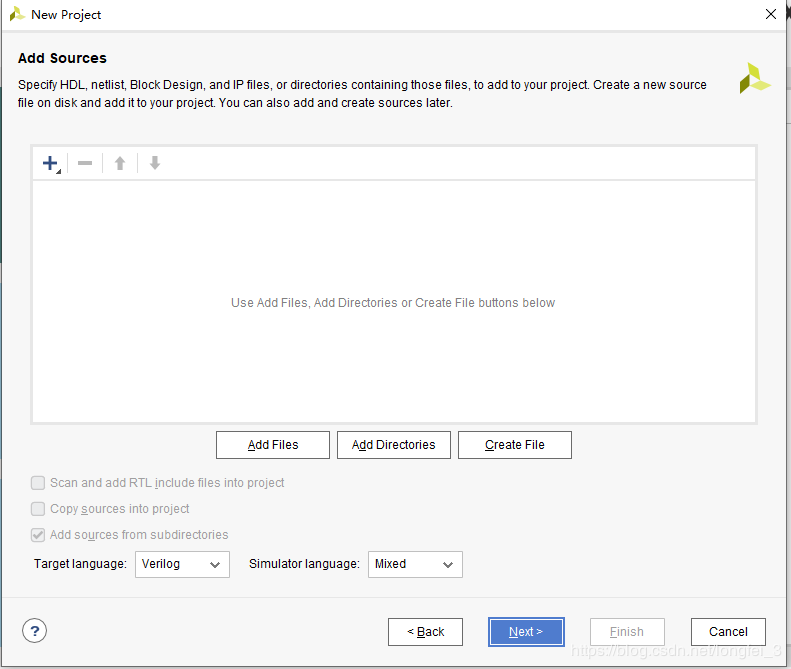

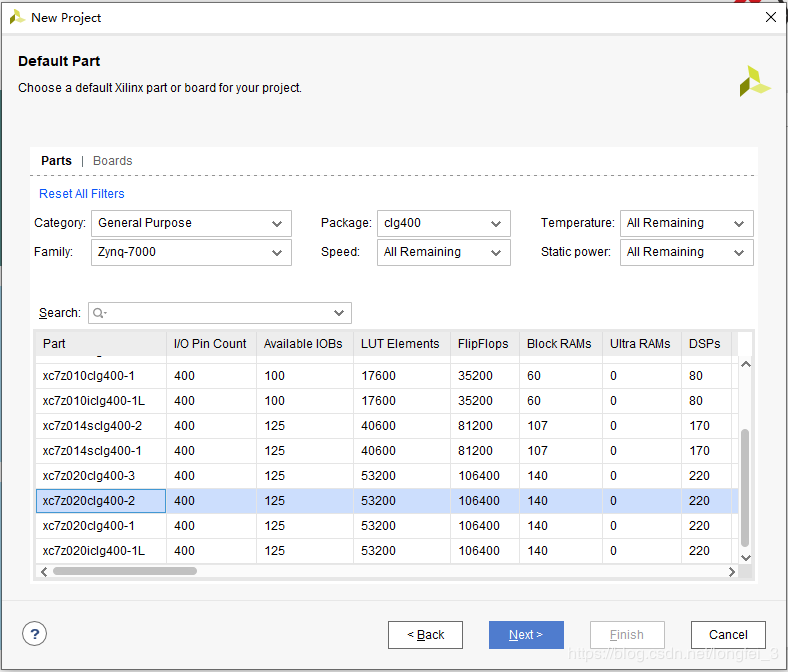

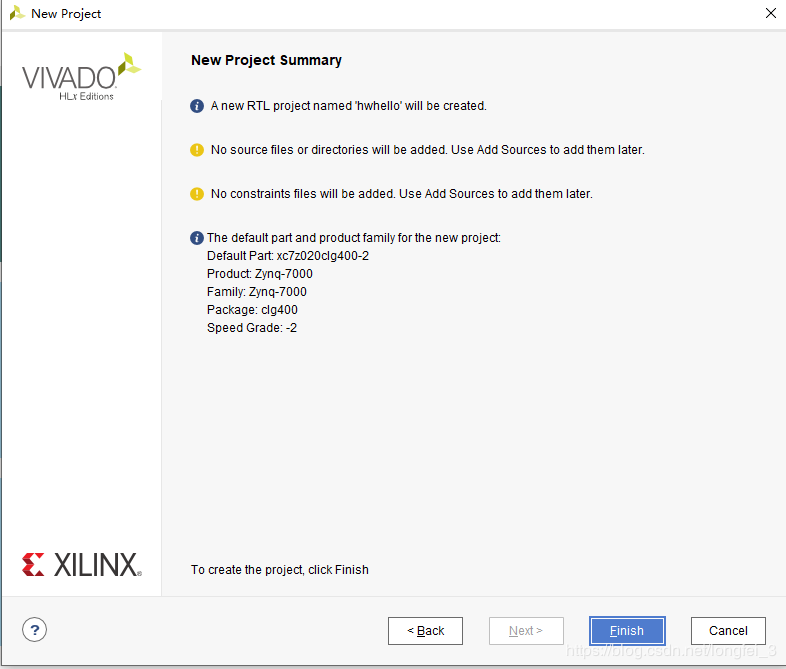

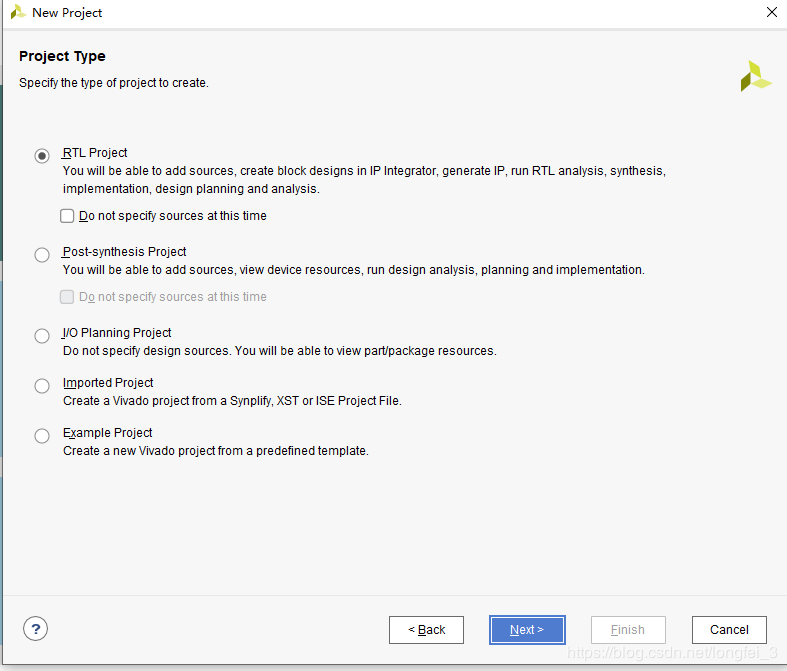

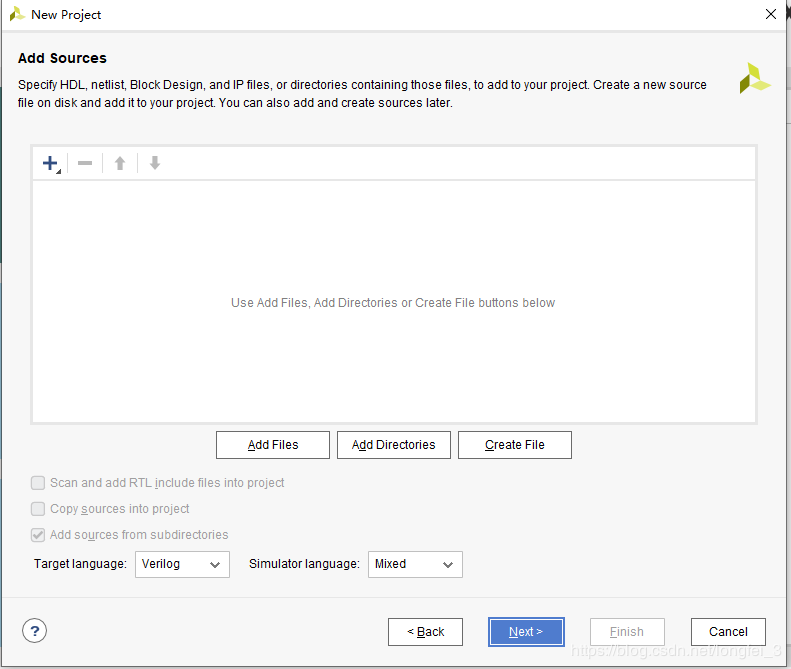

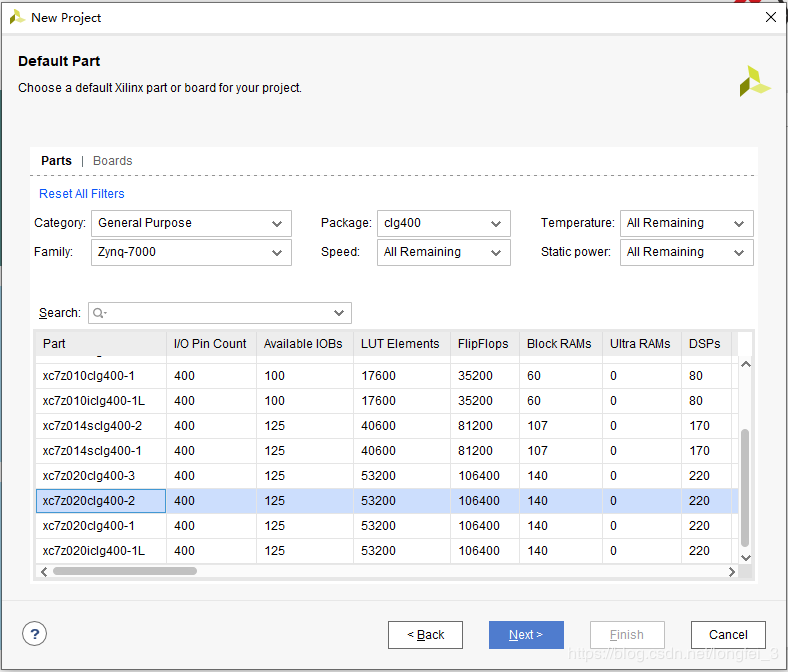

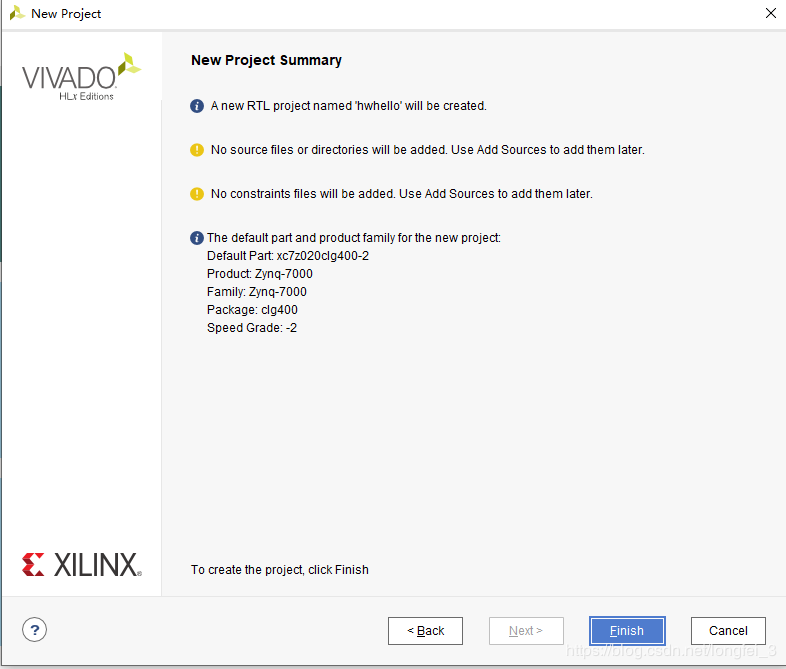

基于黑金ZYNQ 7020开发板创建工程,打开vivado2019.2一步步创建工程,vivado部分还是与之前一模一样没有任何改变。

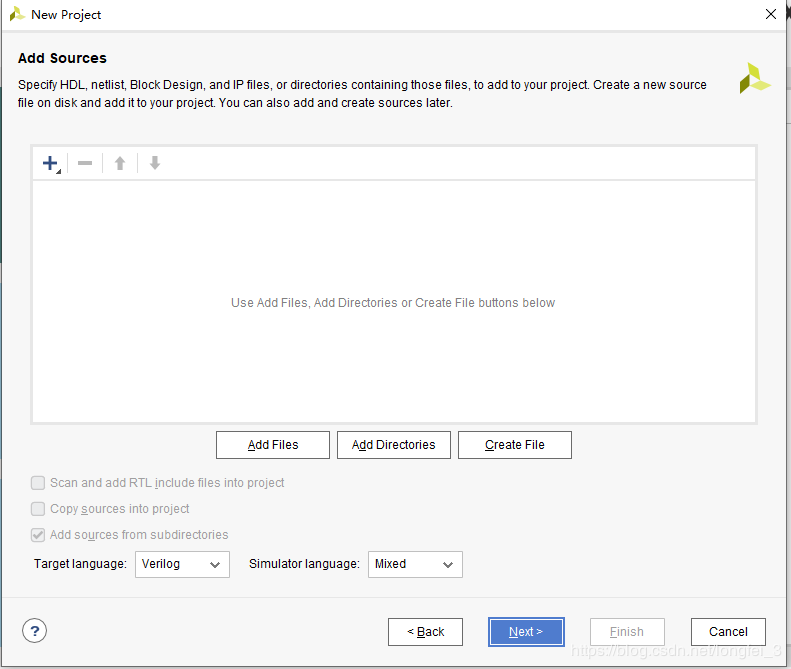

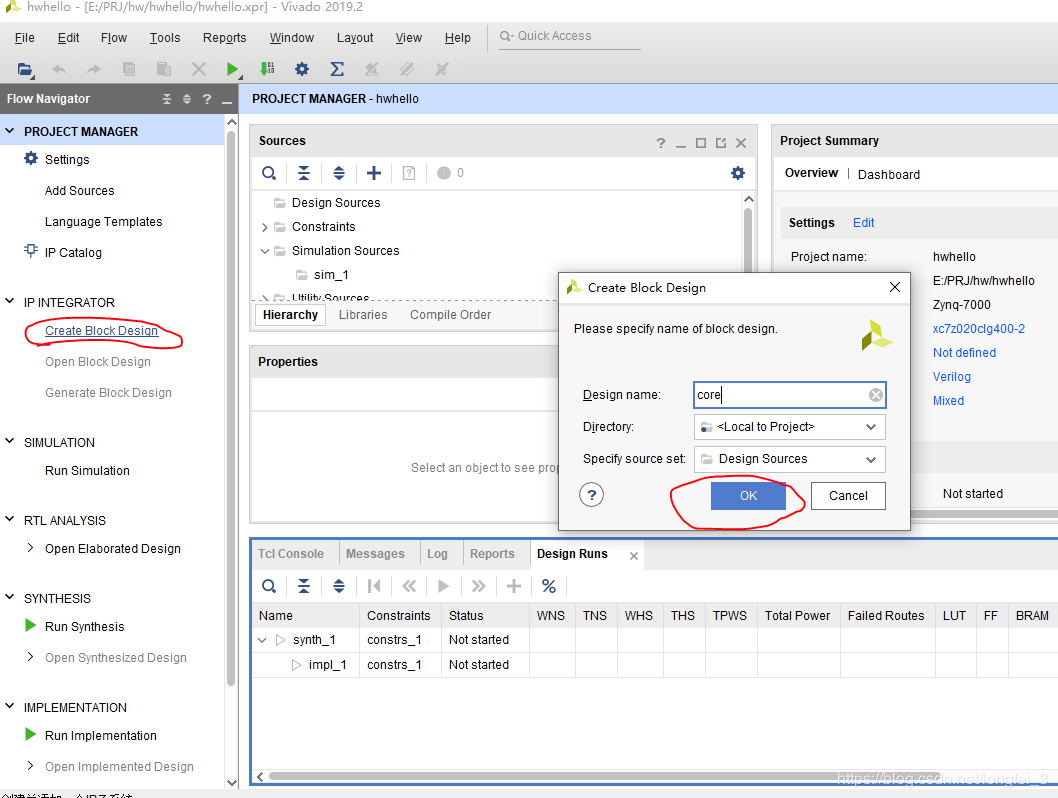

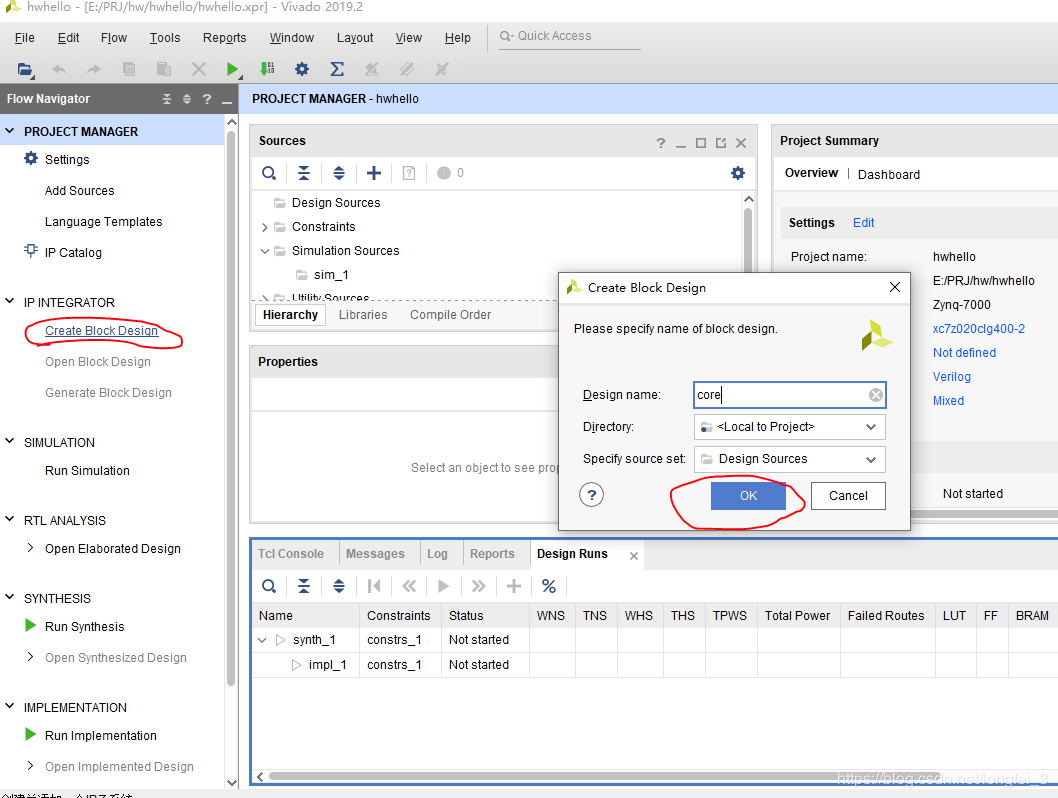

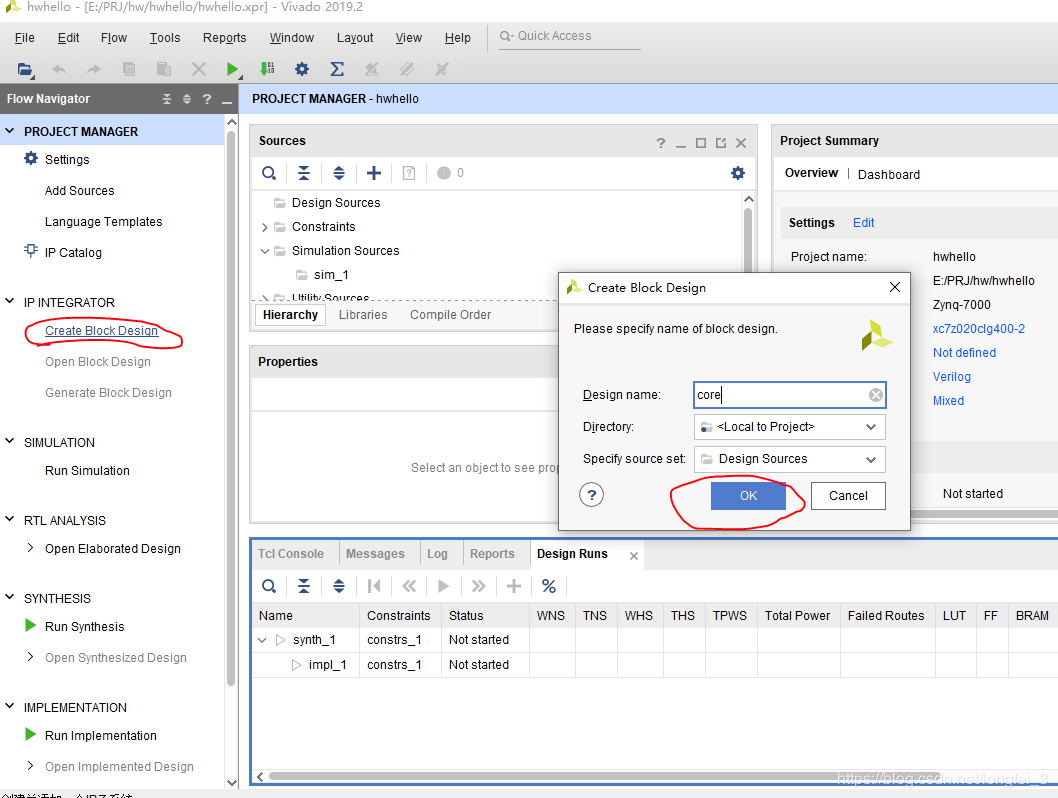

创建完工程,创建同一个 Block Design工程

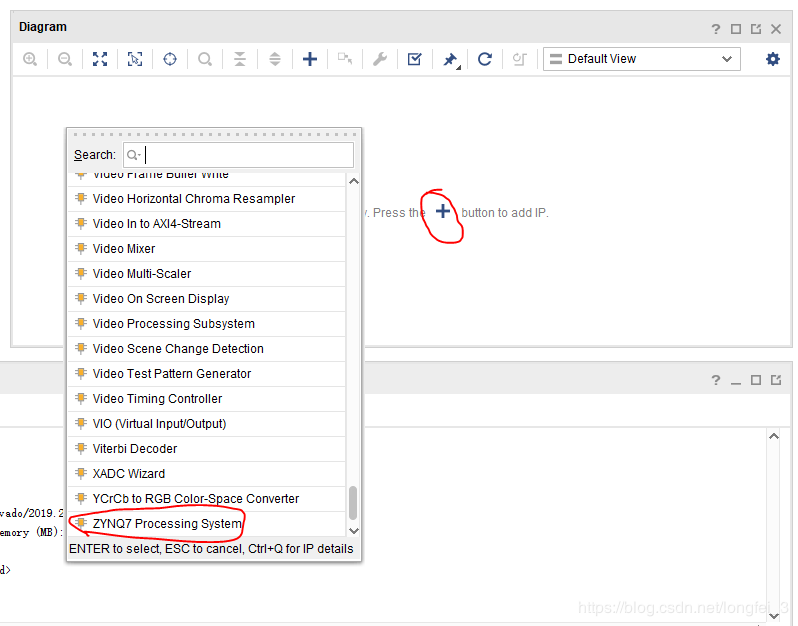

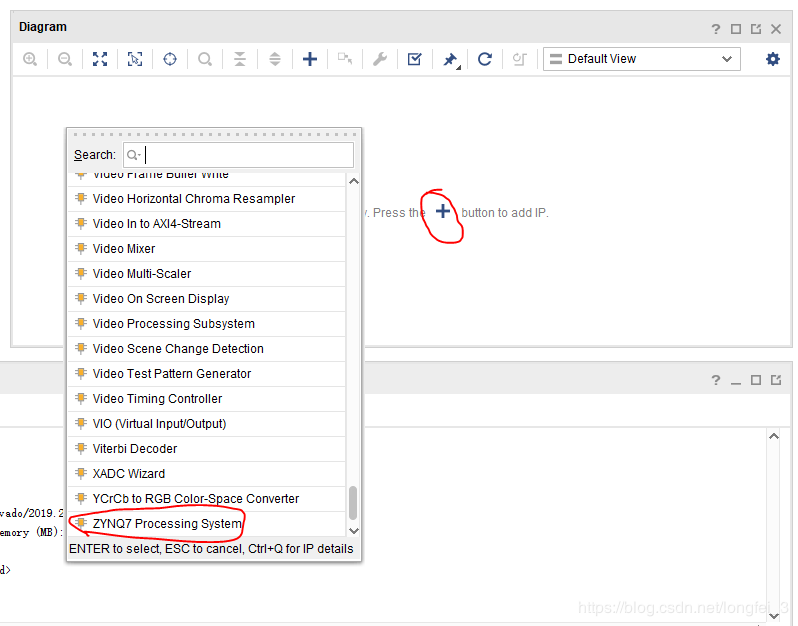

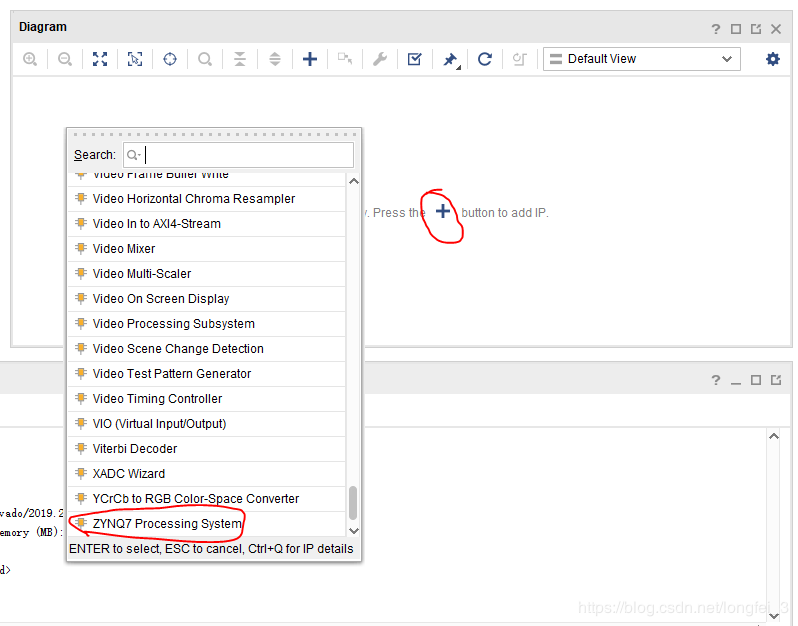

添加ZYNQ 核

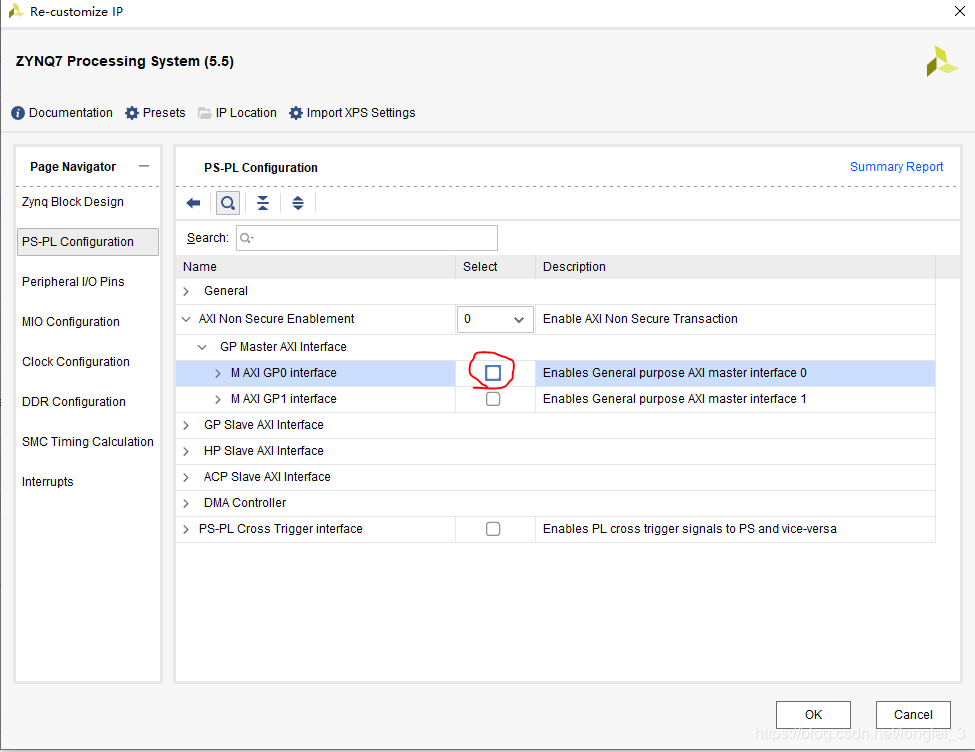

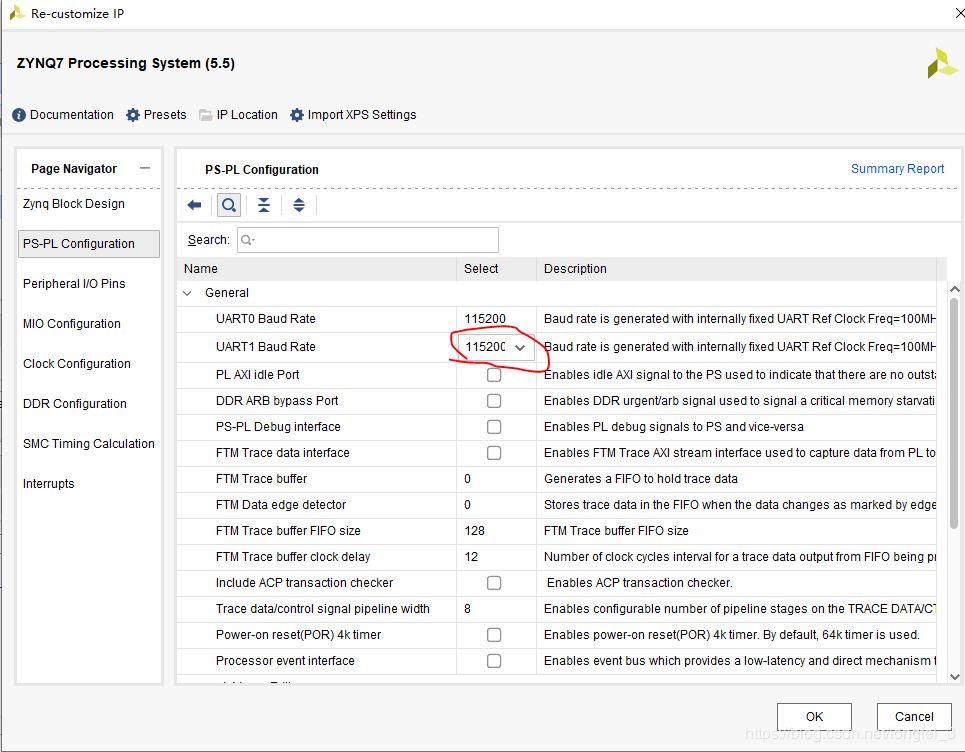

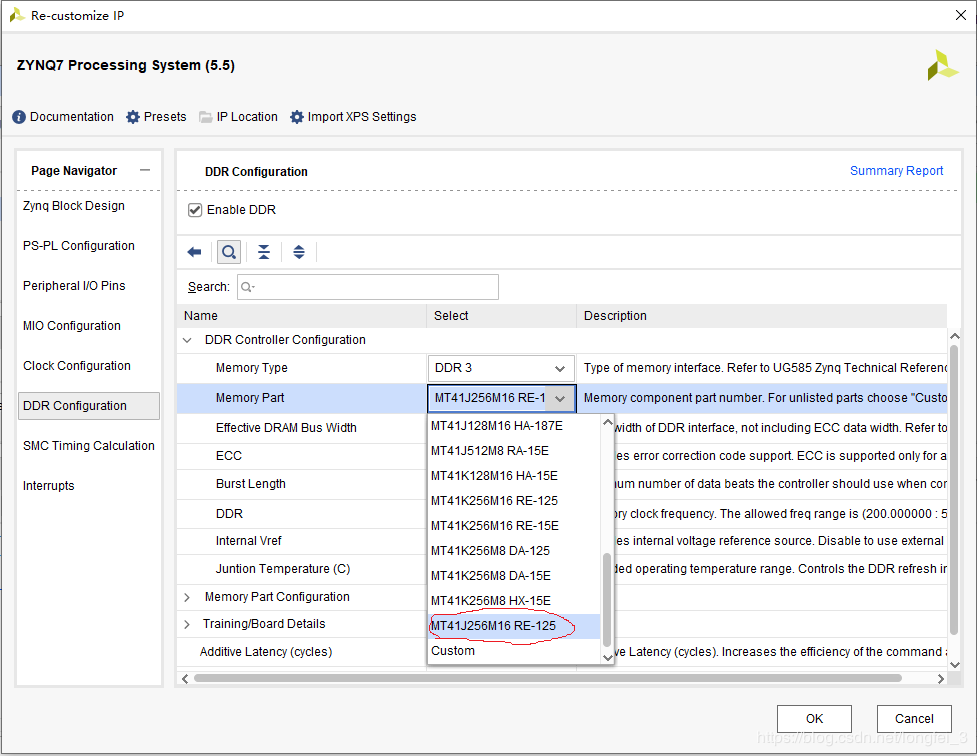

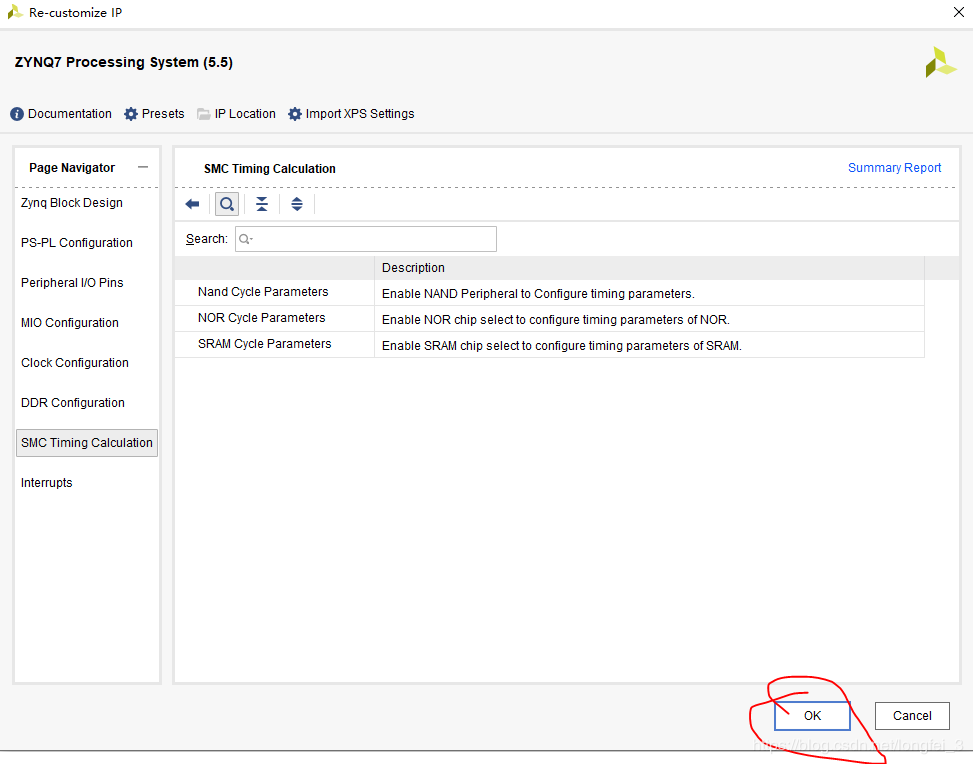

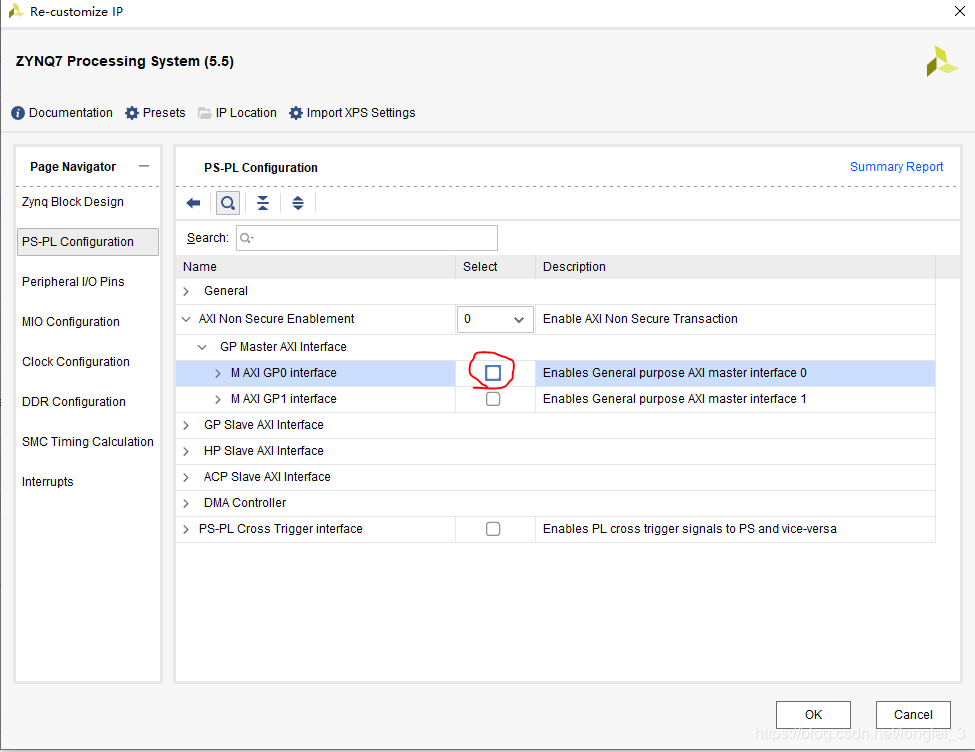

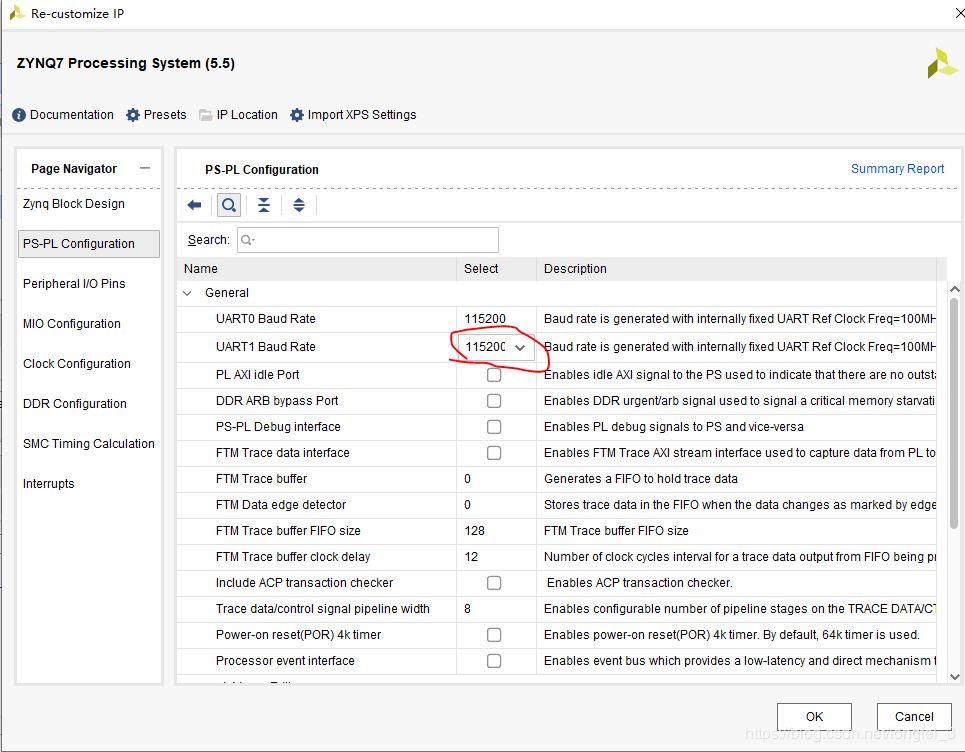

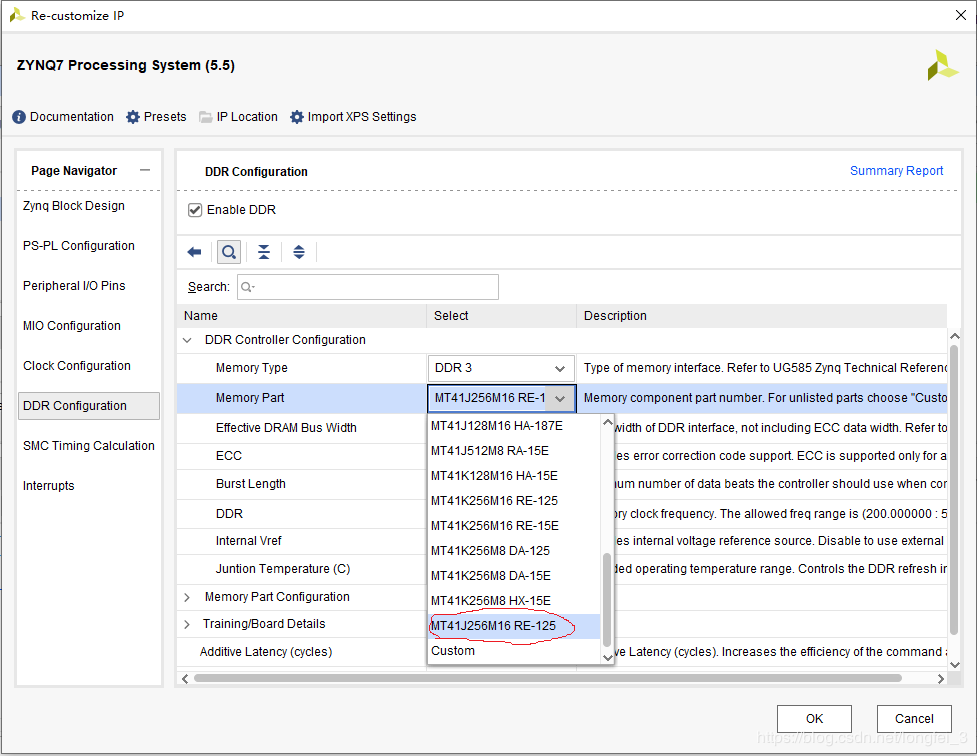

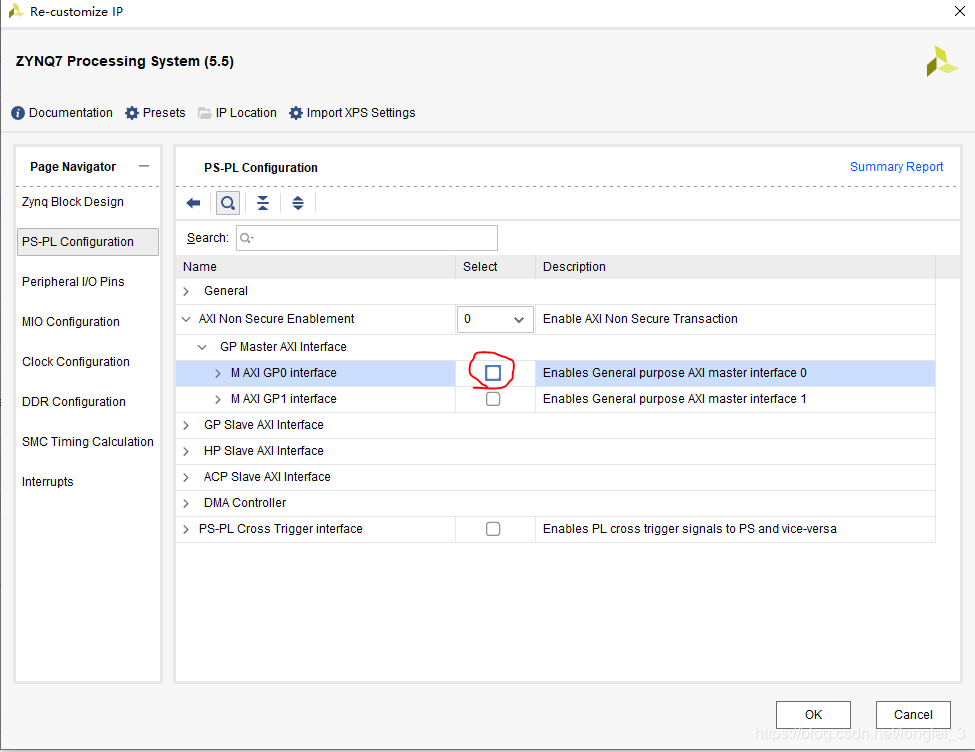

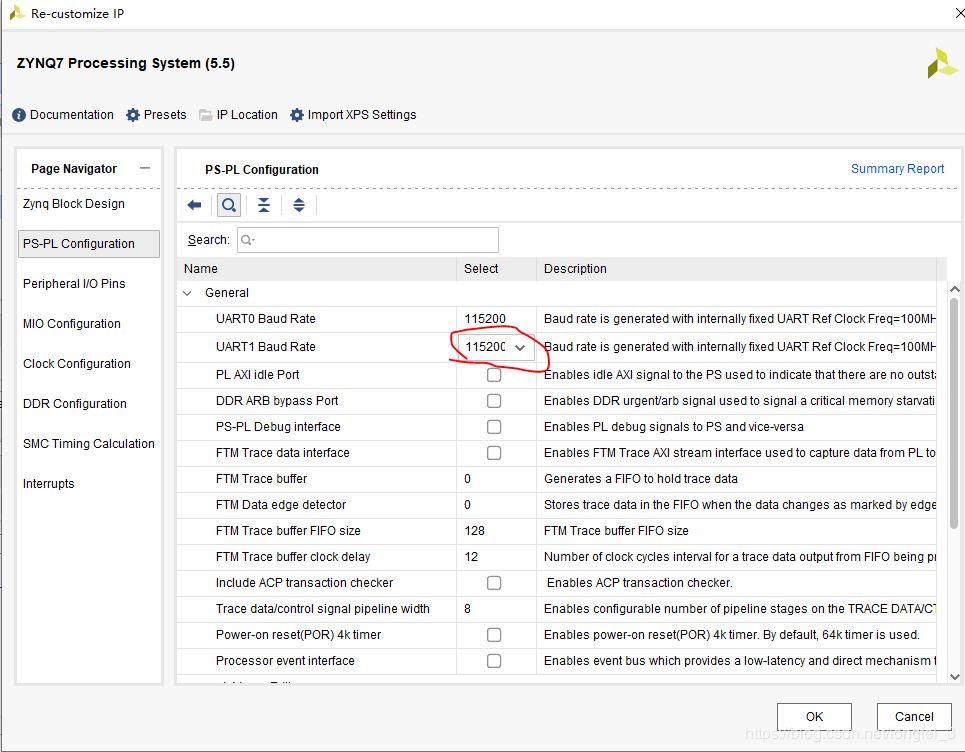

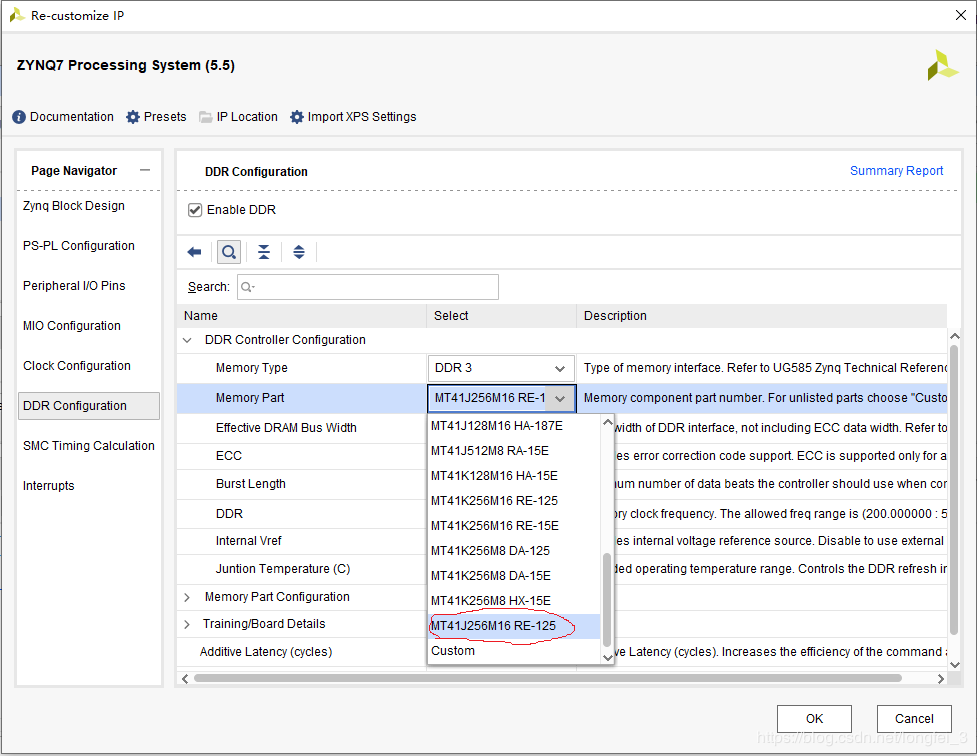

双击ZYNQ核设置一下,这里设置跟板子一致UART1,波特率选择115200,没有用到PL,AXI也没使用。

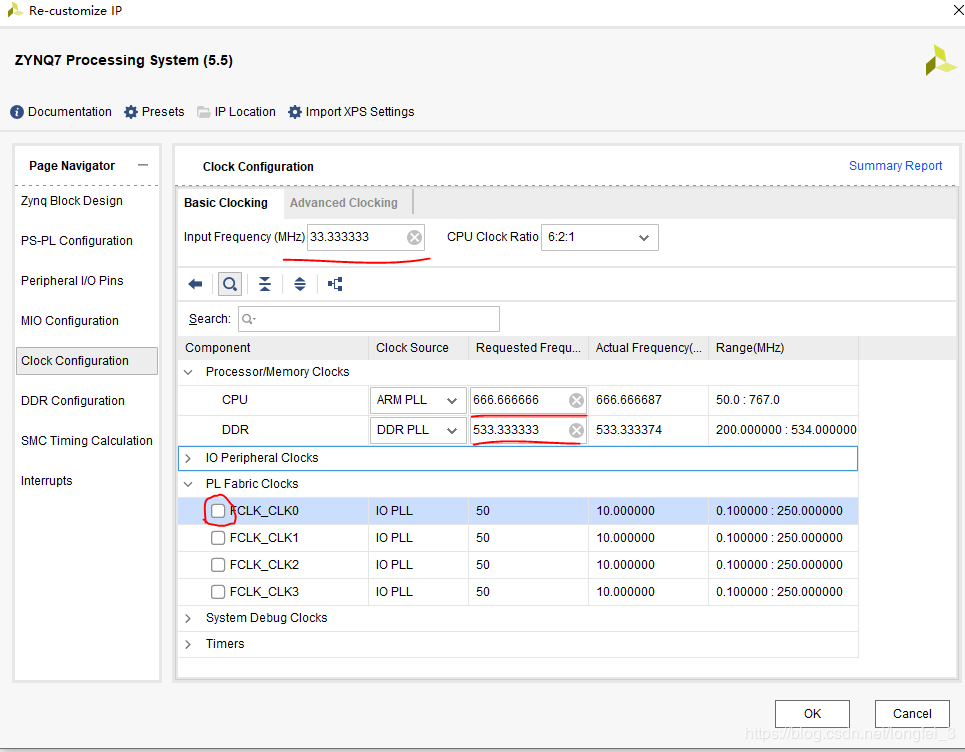

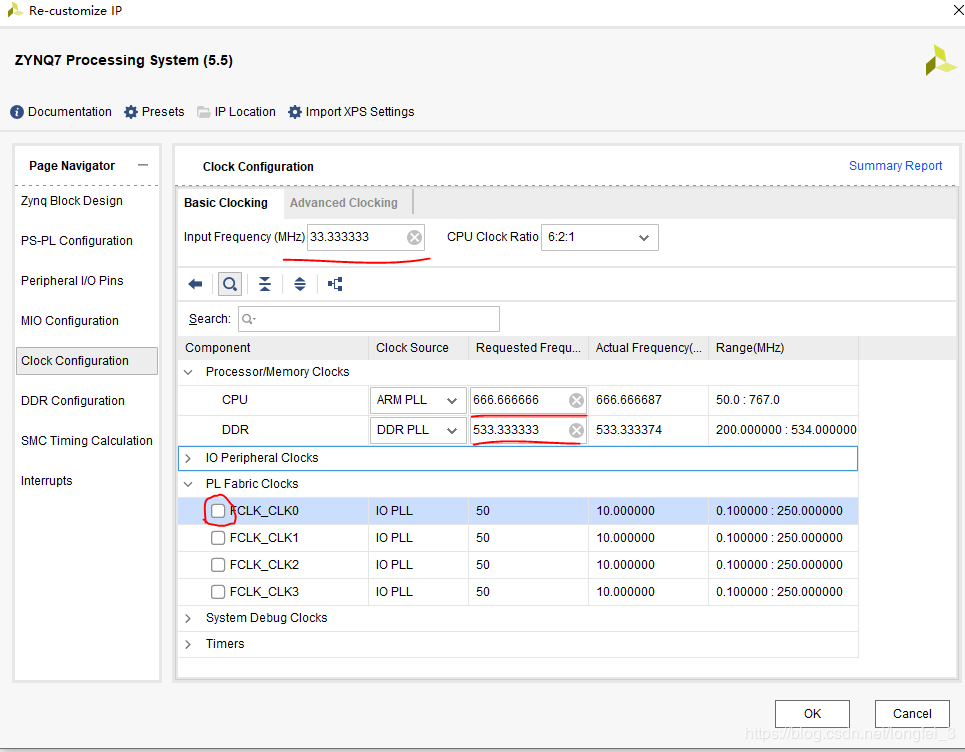

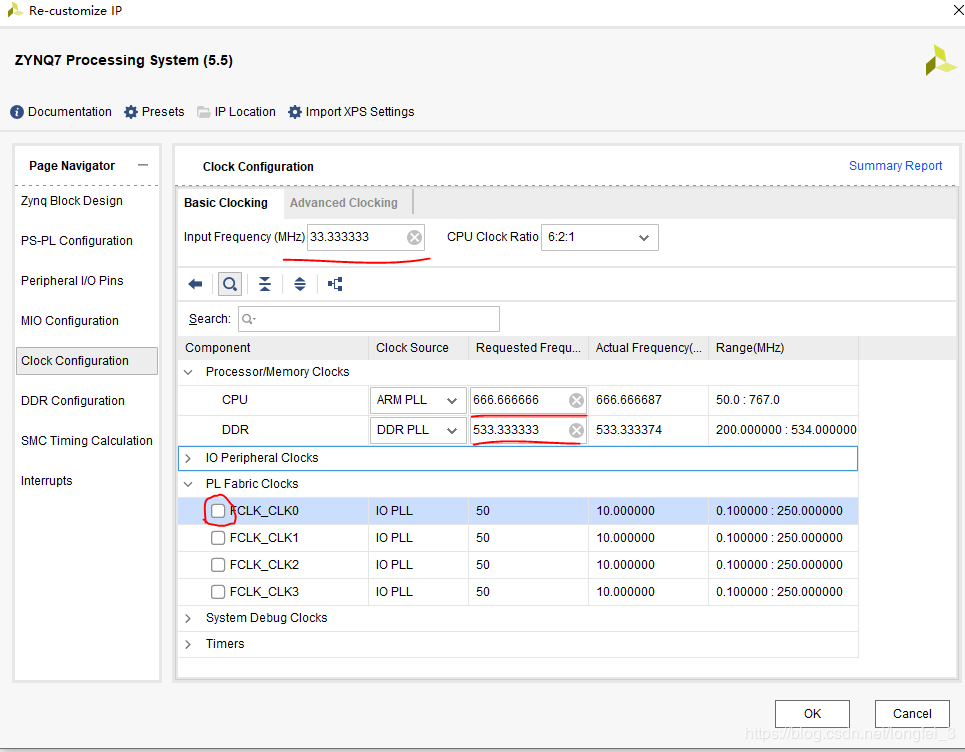

时钟默认即可,黑金的7020最高可以跑到767Mhz。

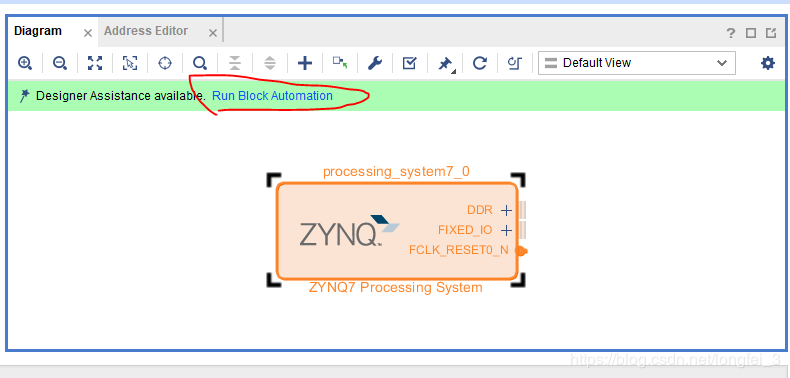

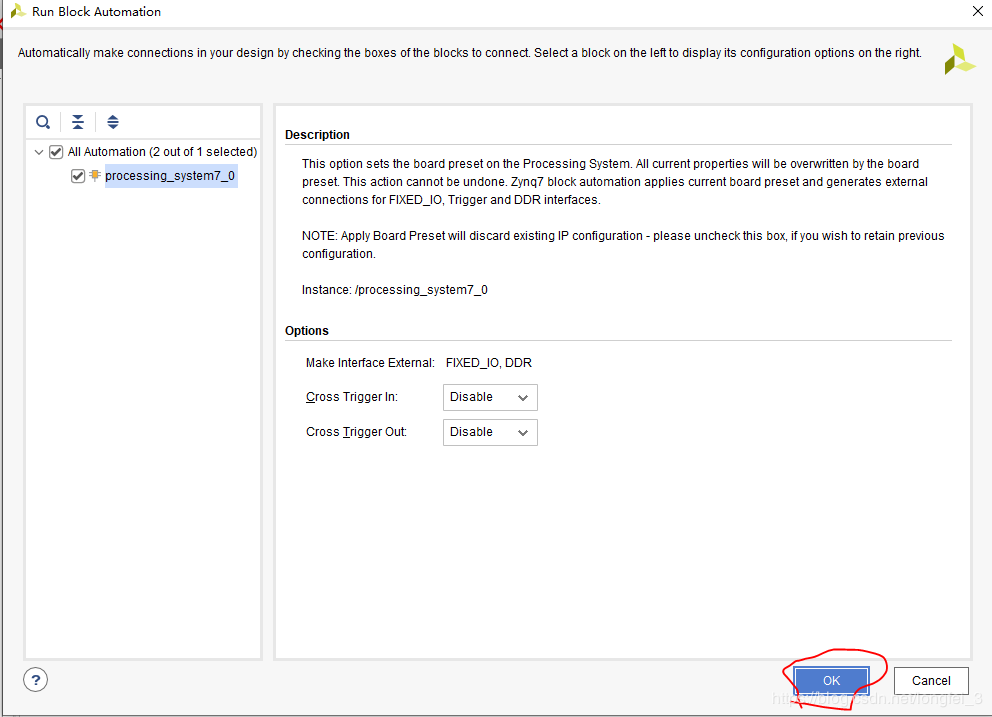

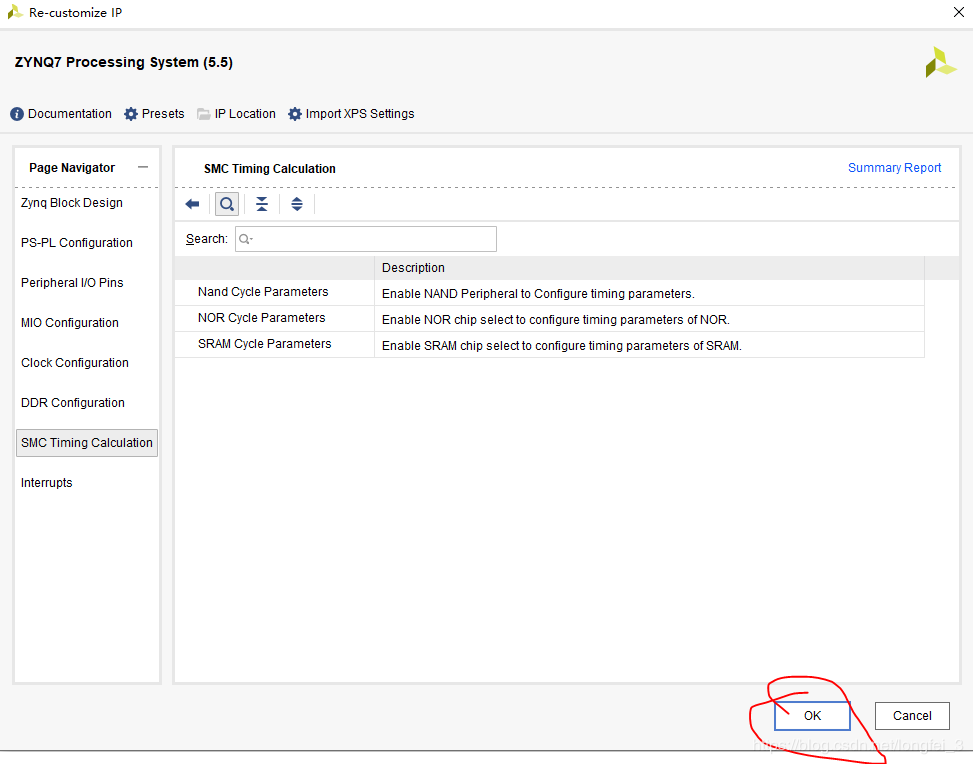

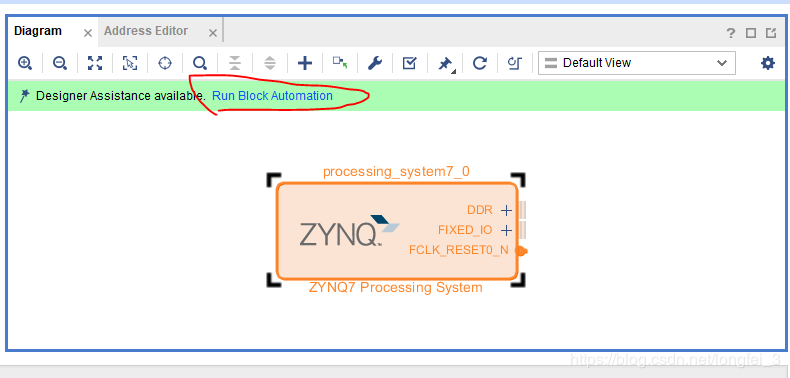

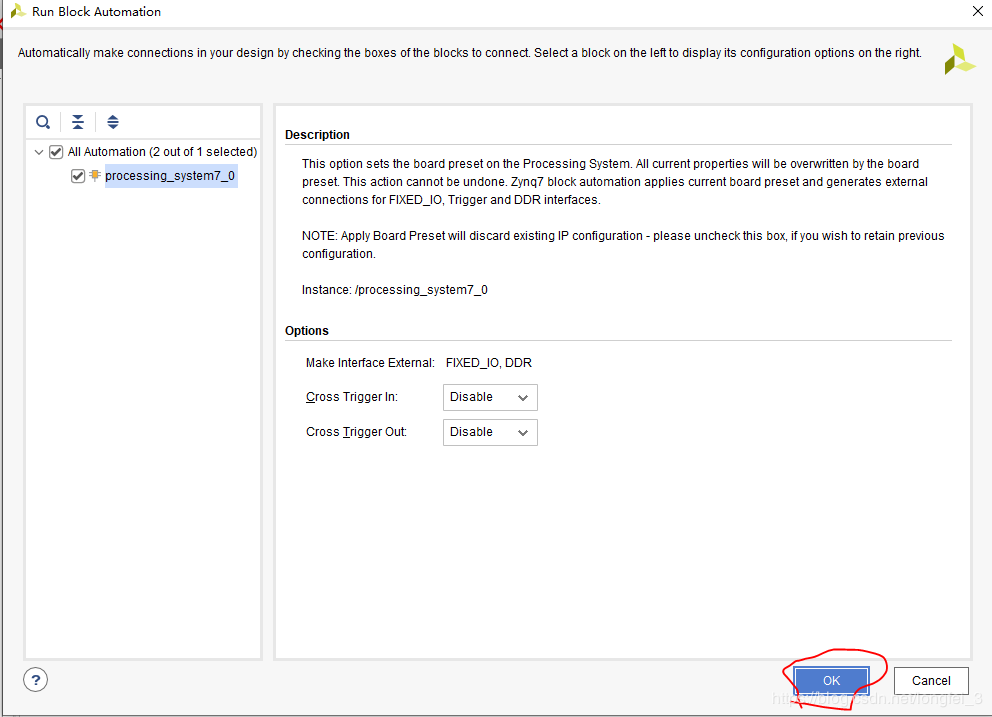

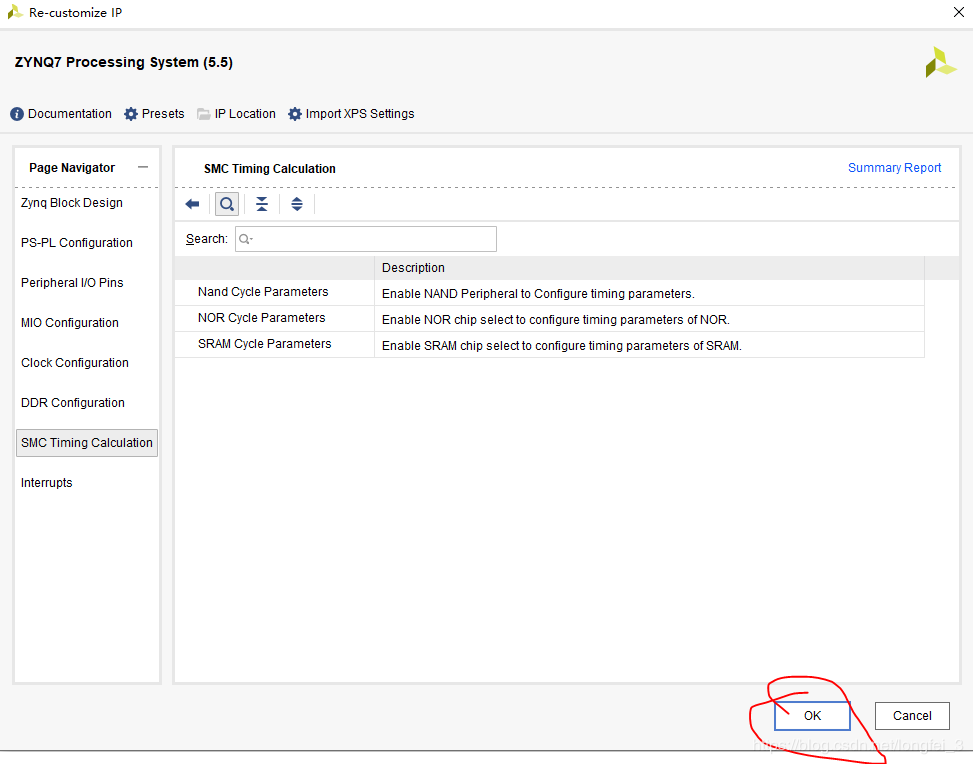

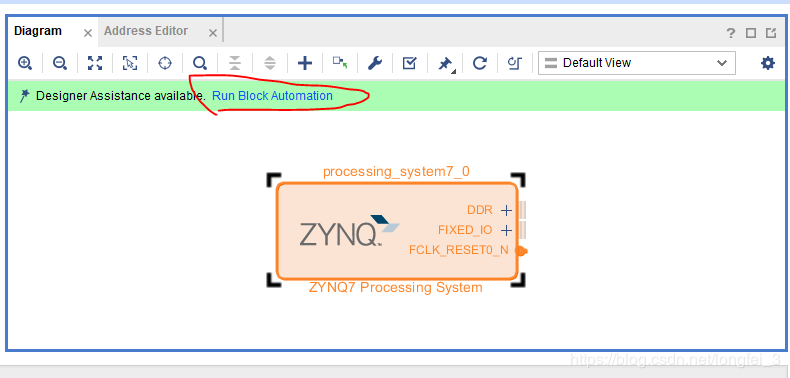

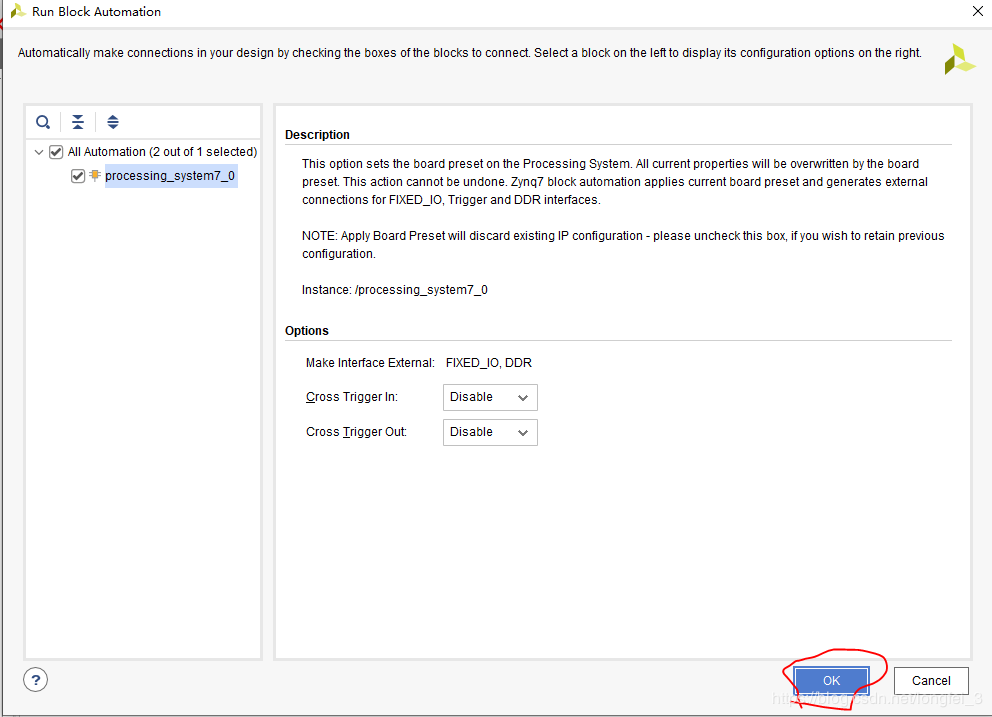

设置完成。自动连线。

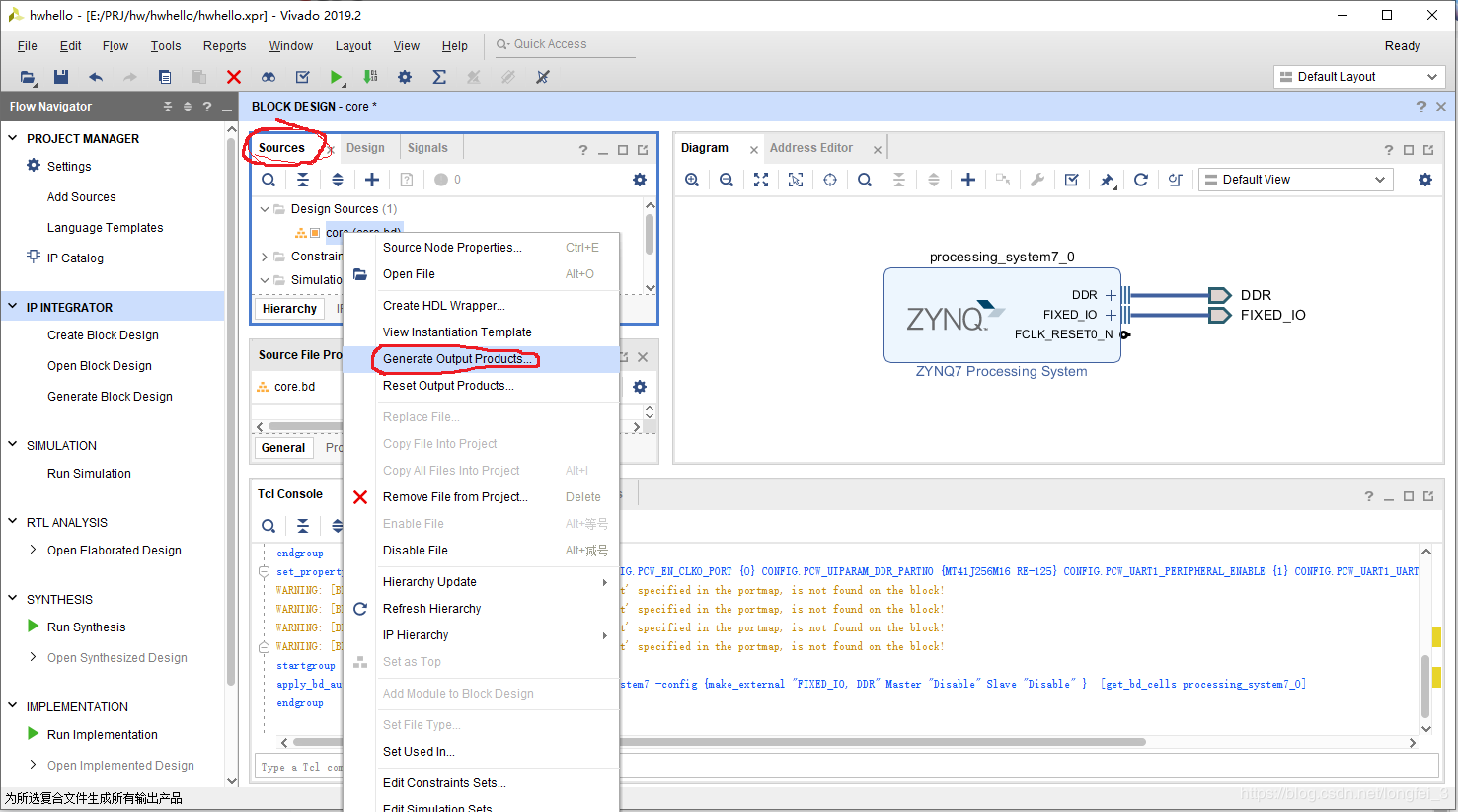

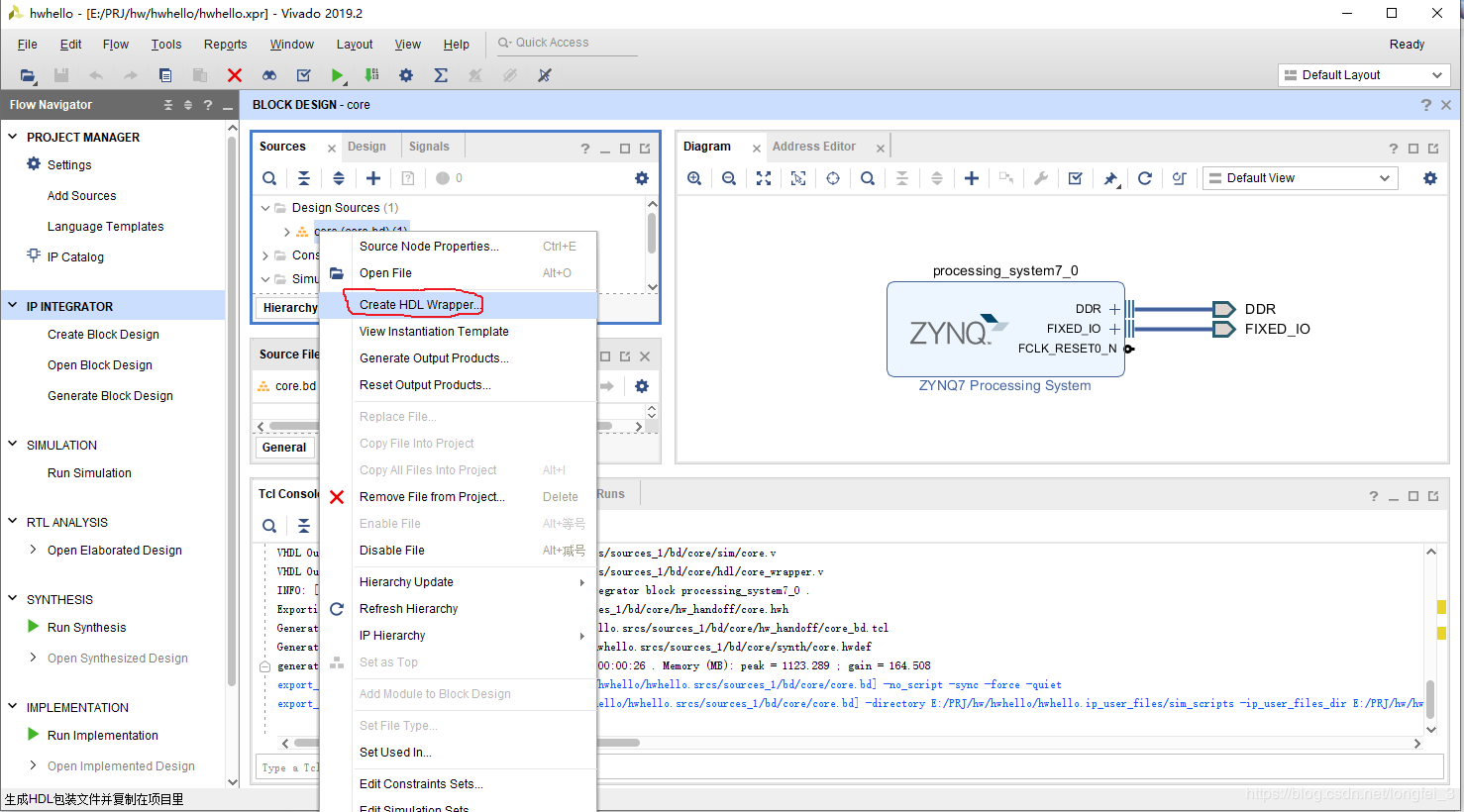

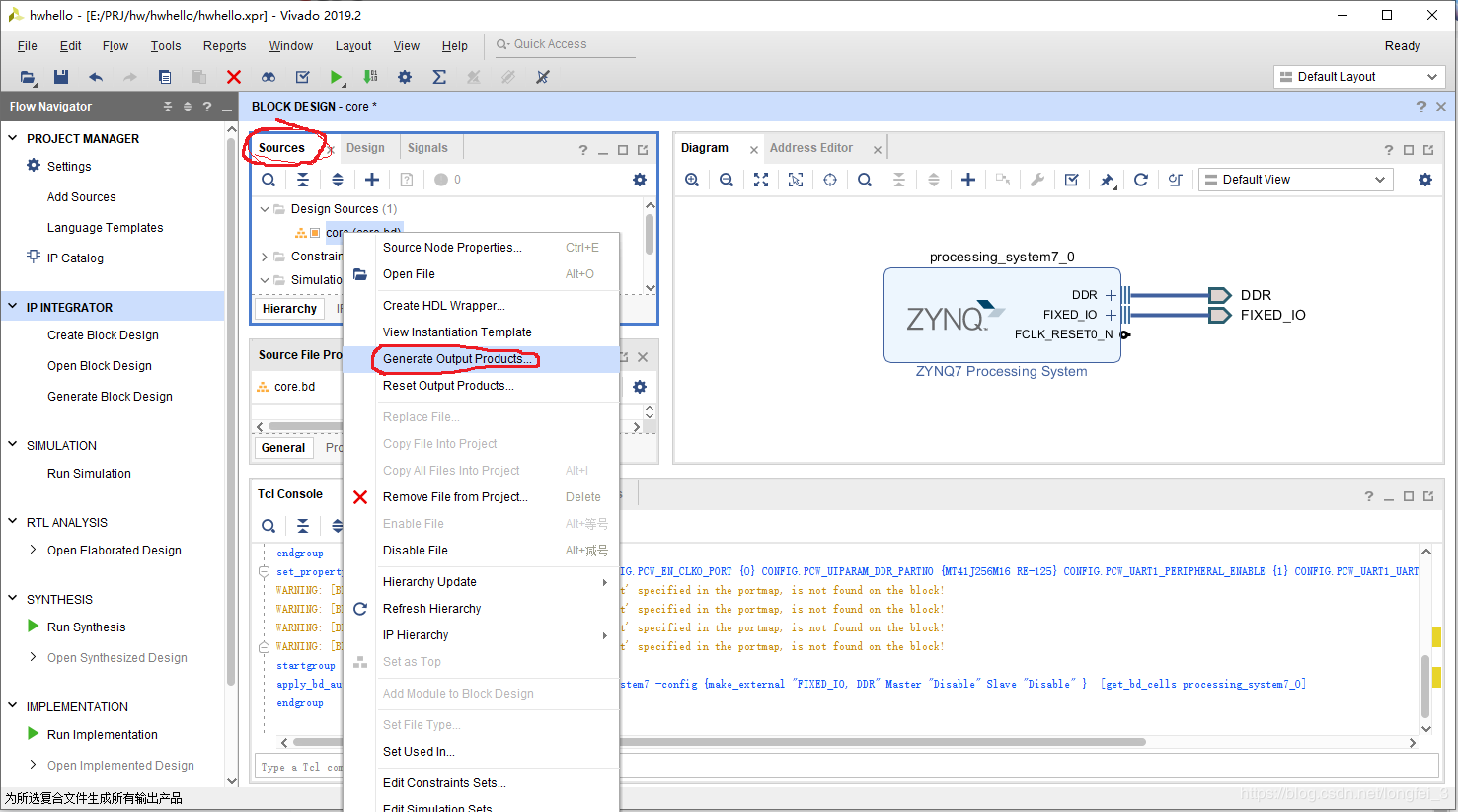

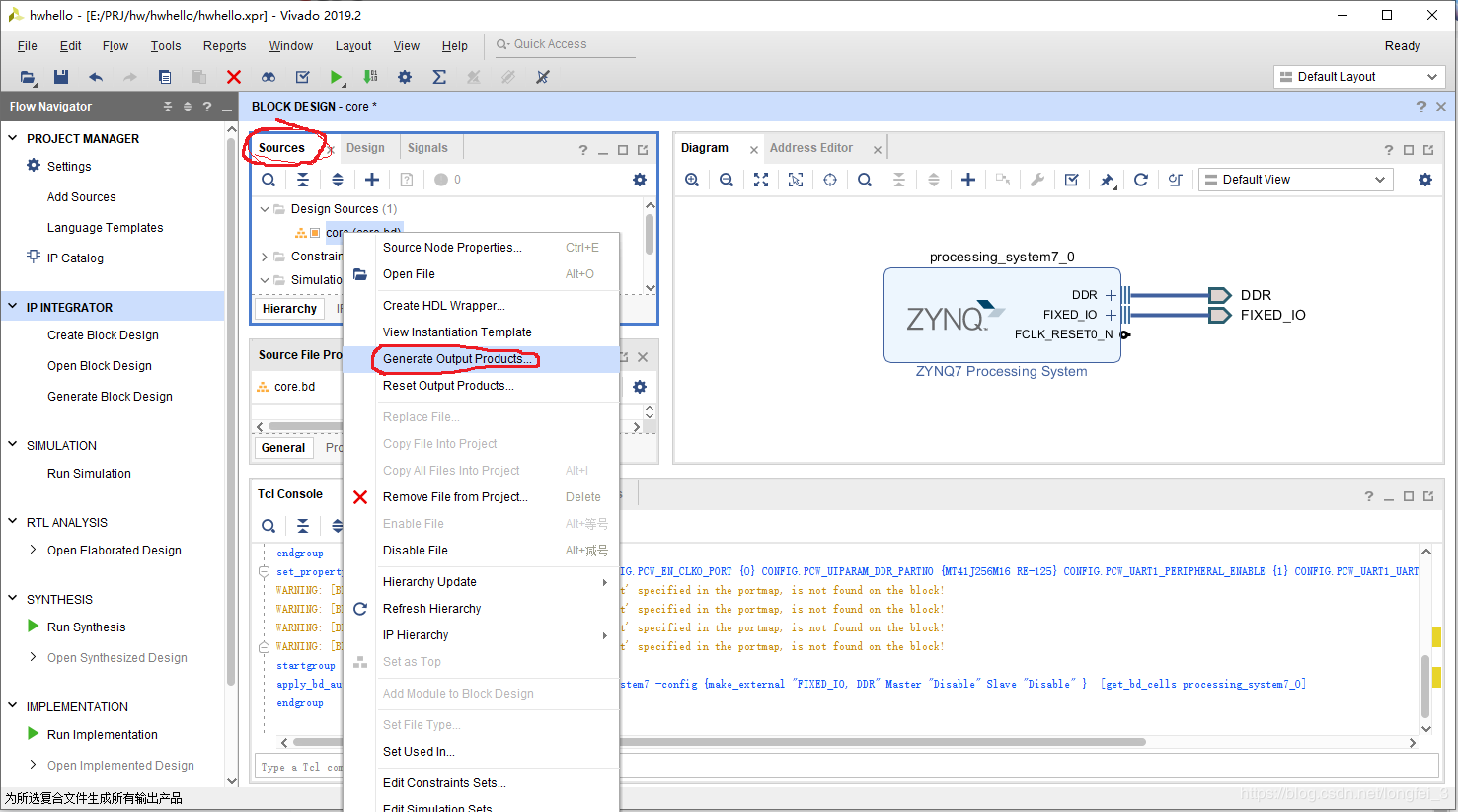

生成文件:

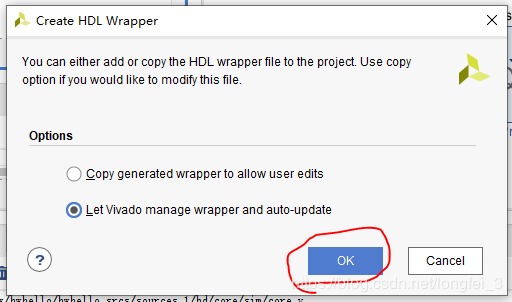

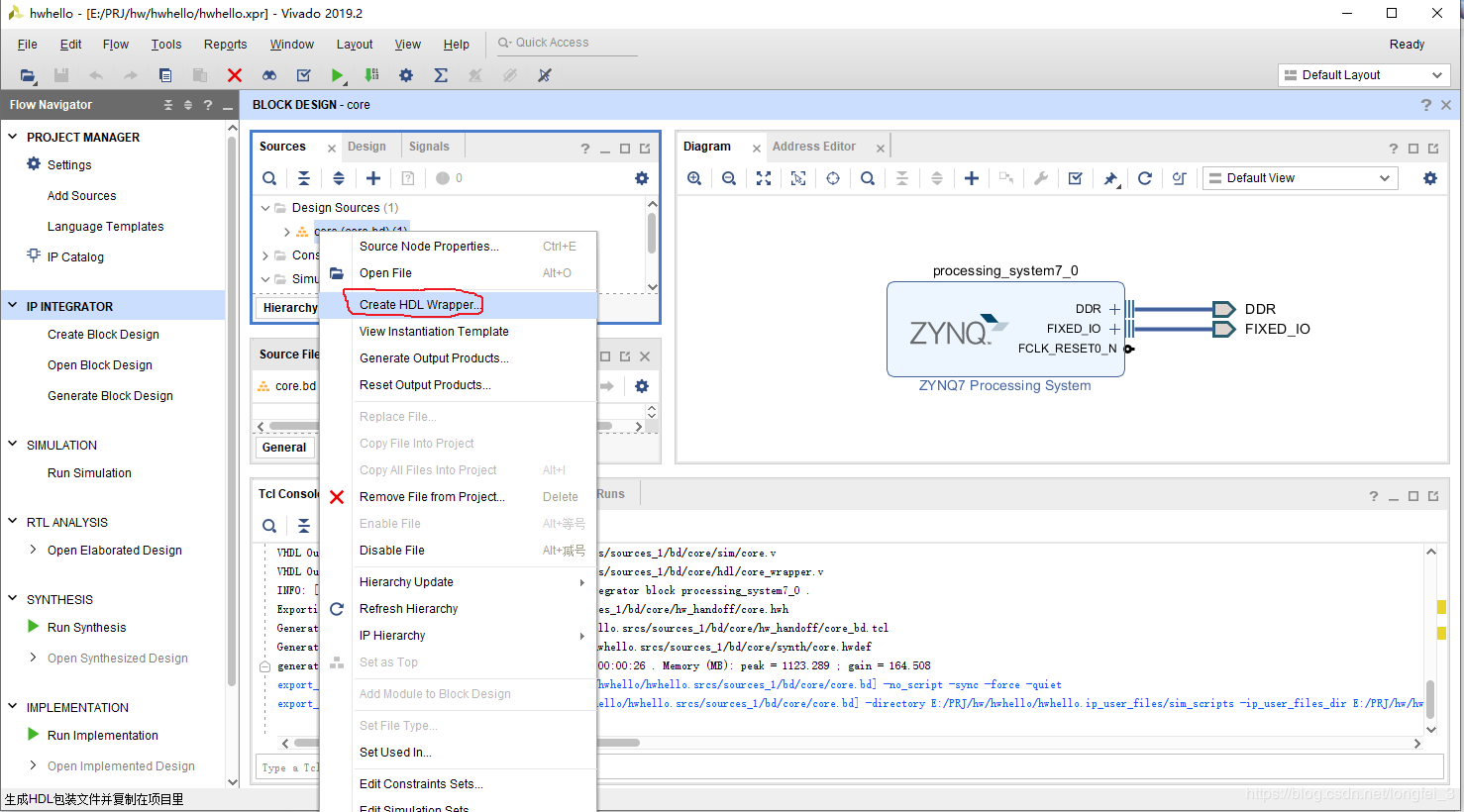

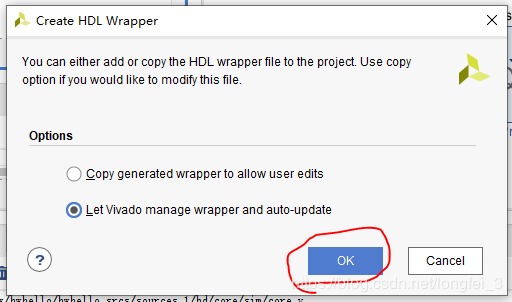

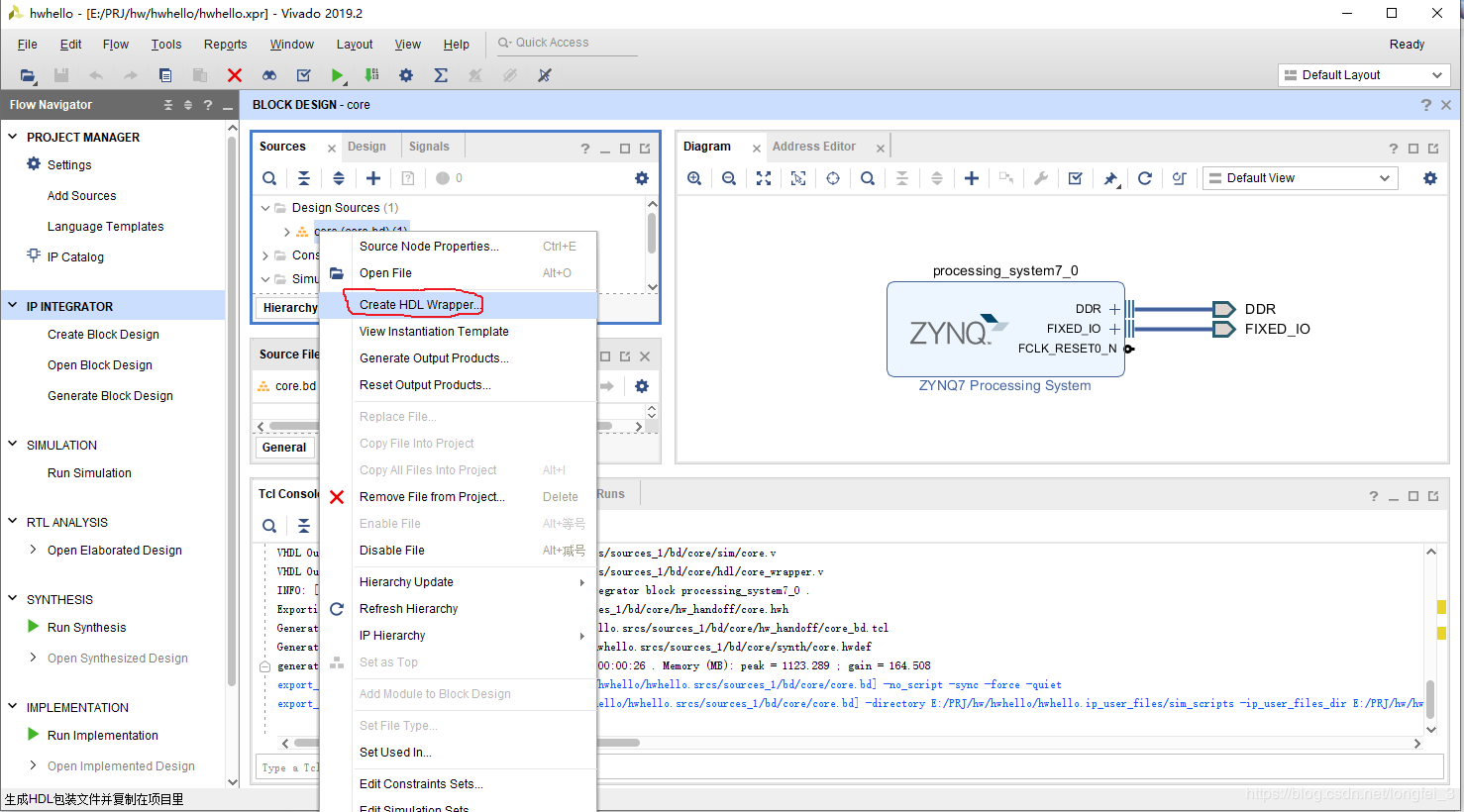

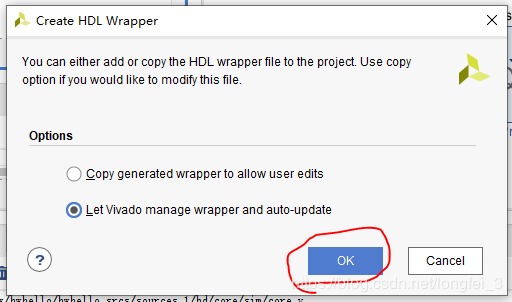

生成顶层文件:

至此PL部分完成了。

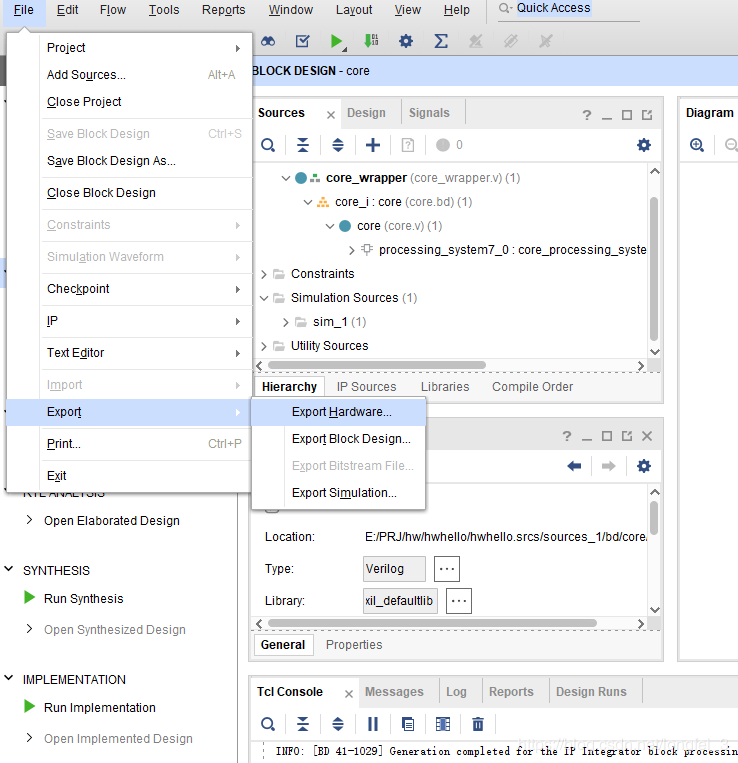

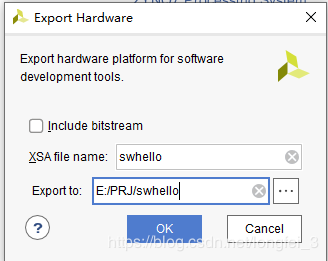

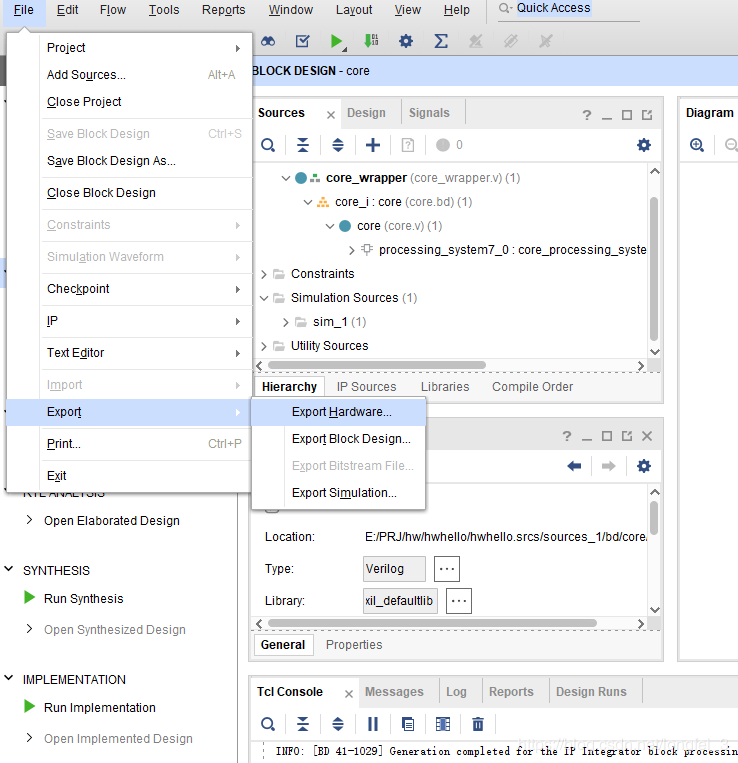

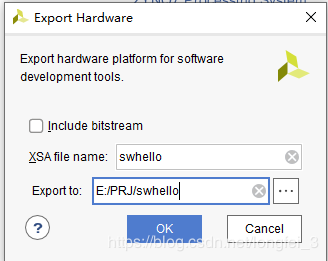

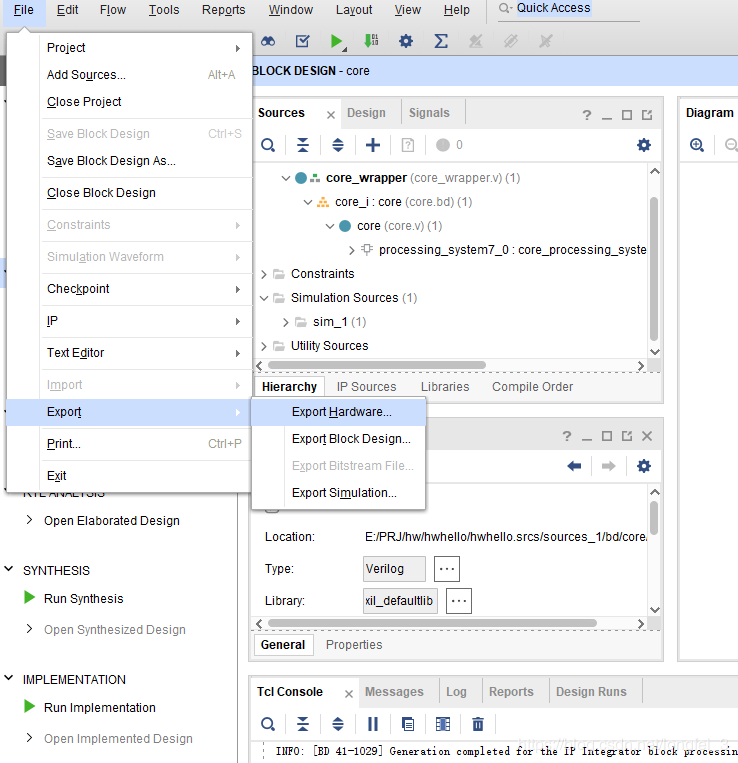

导出设计到软件,没有用到PL,所以不用综合生成bit文件了,这里直接导出

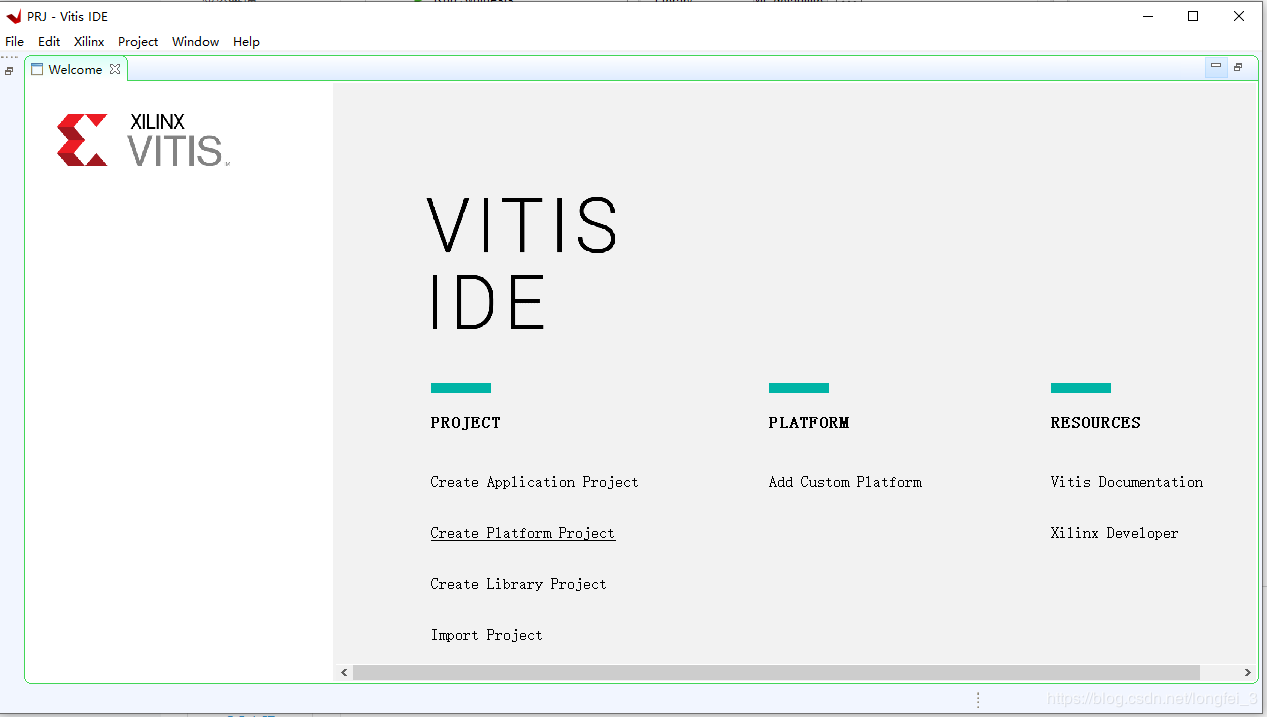

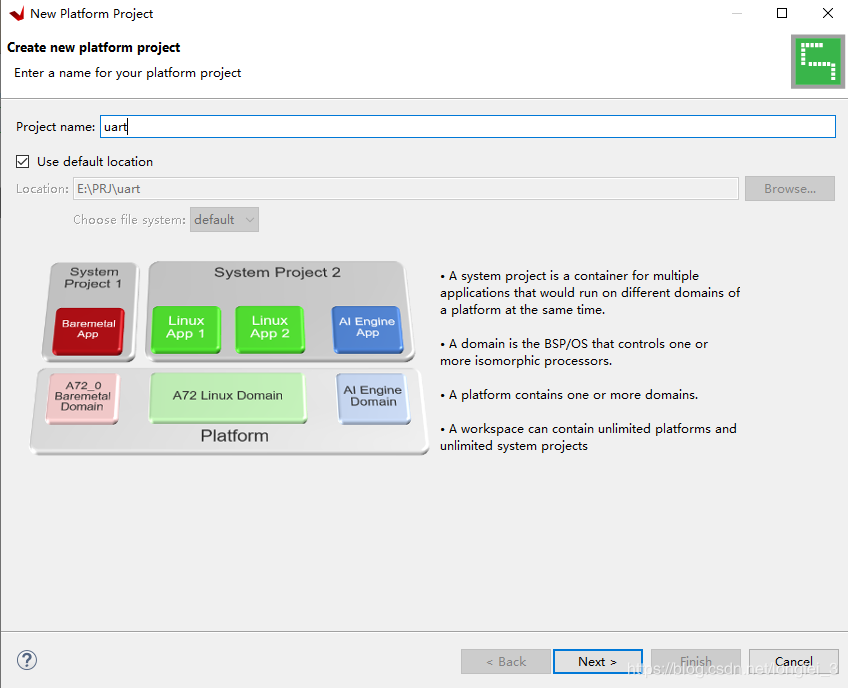

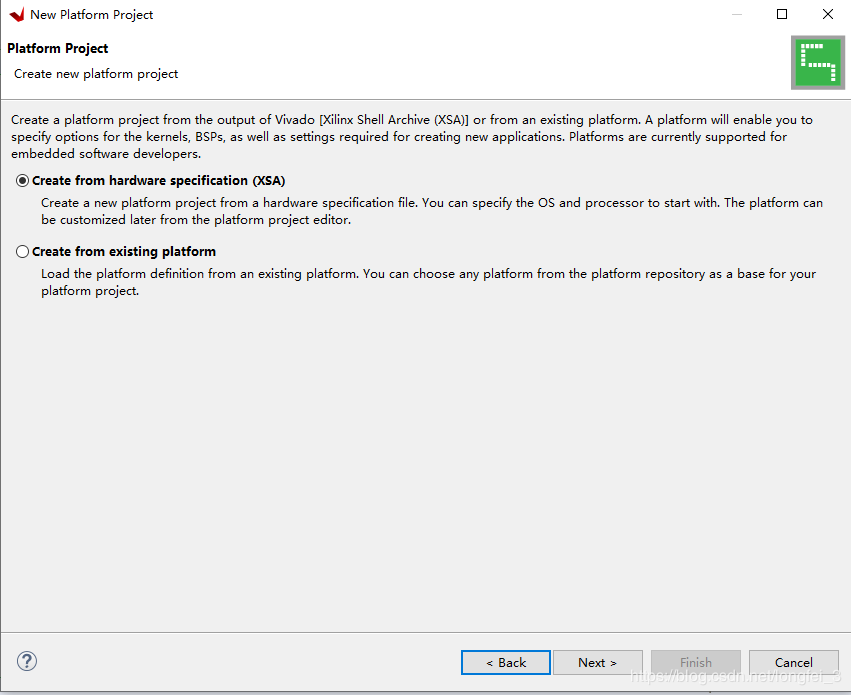

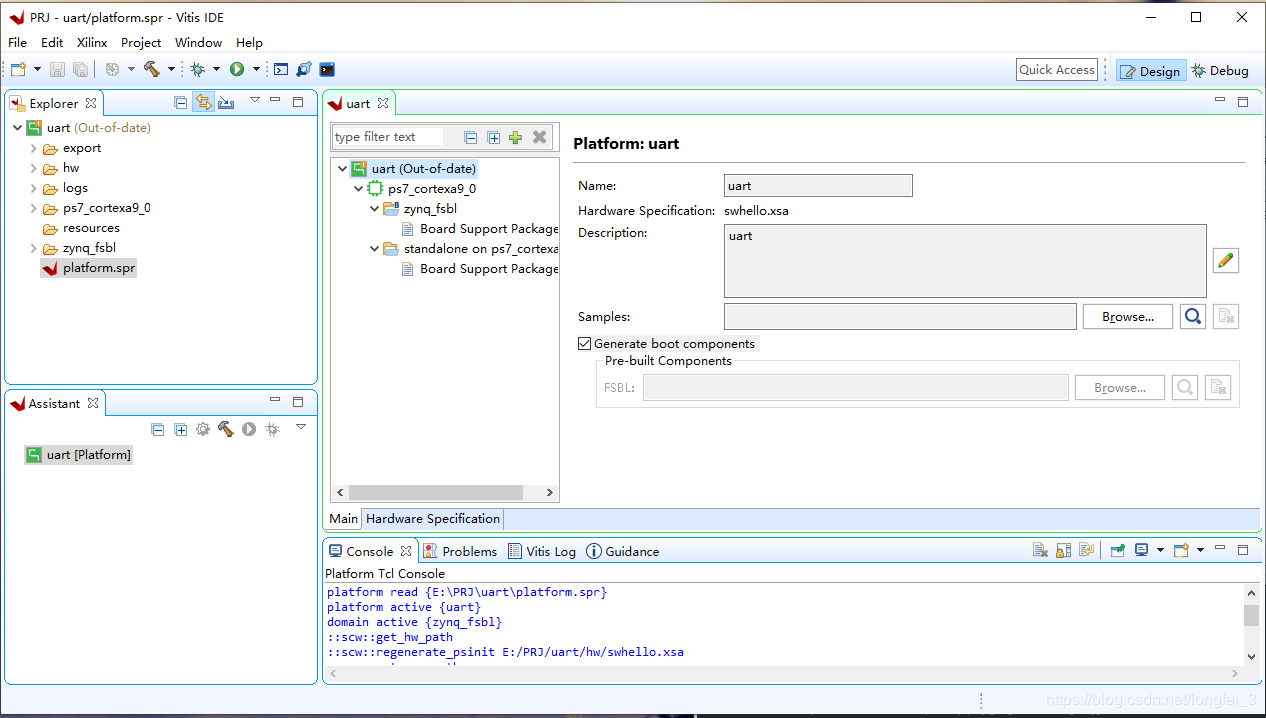

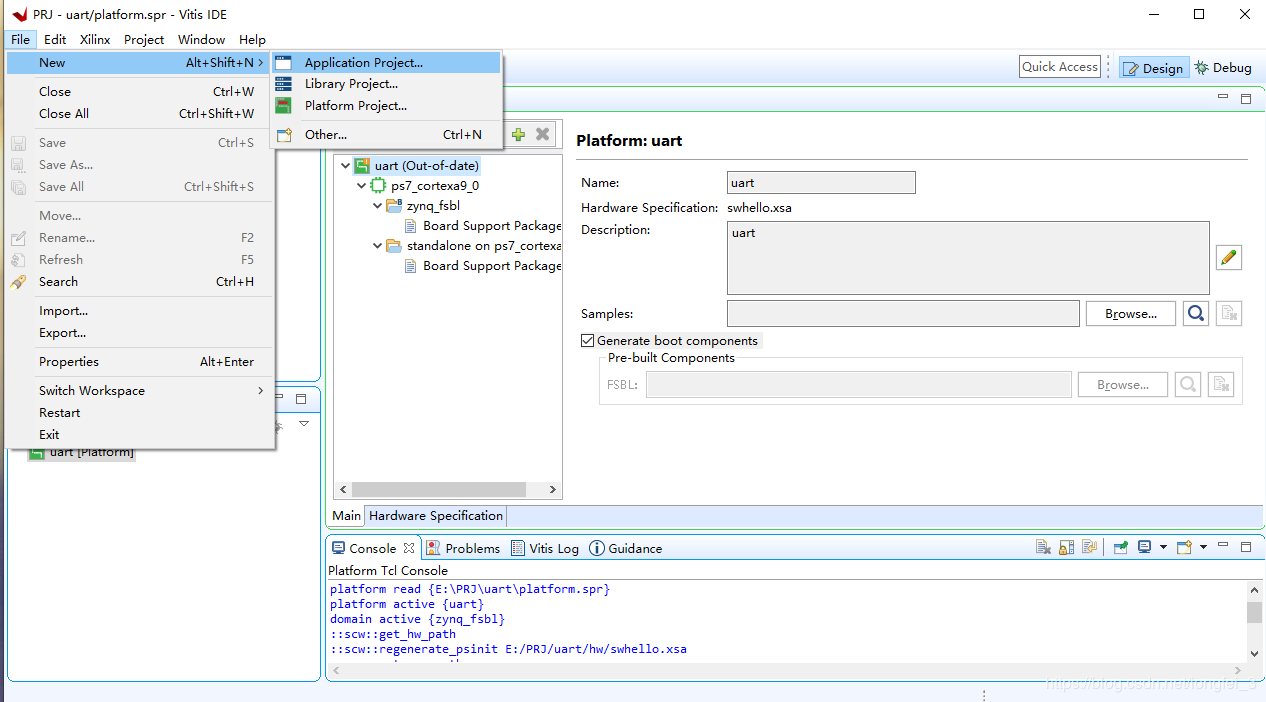

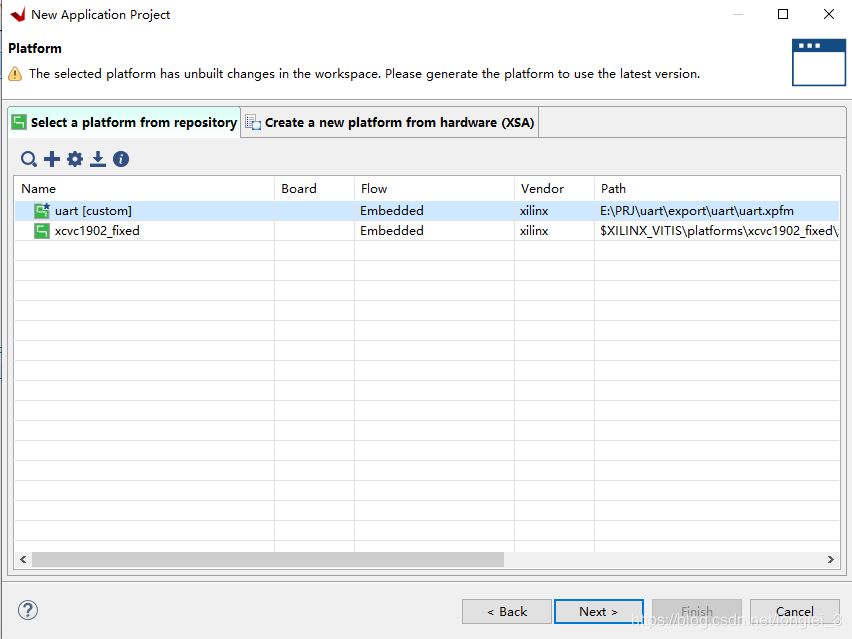

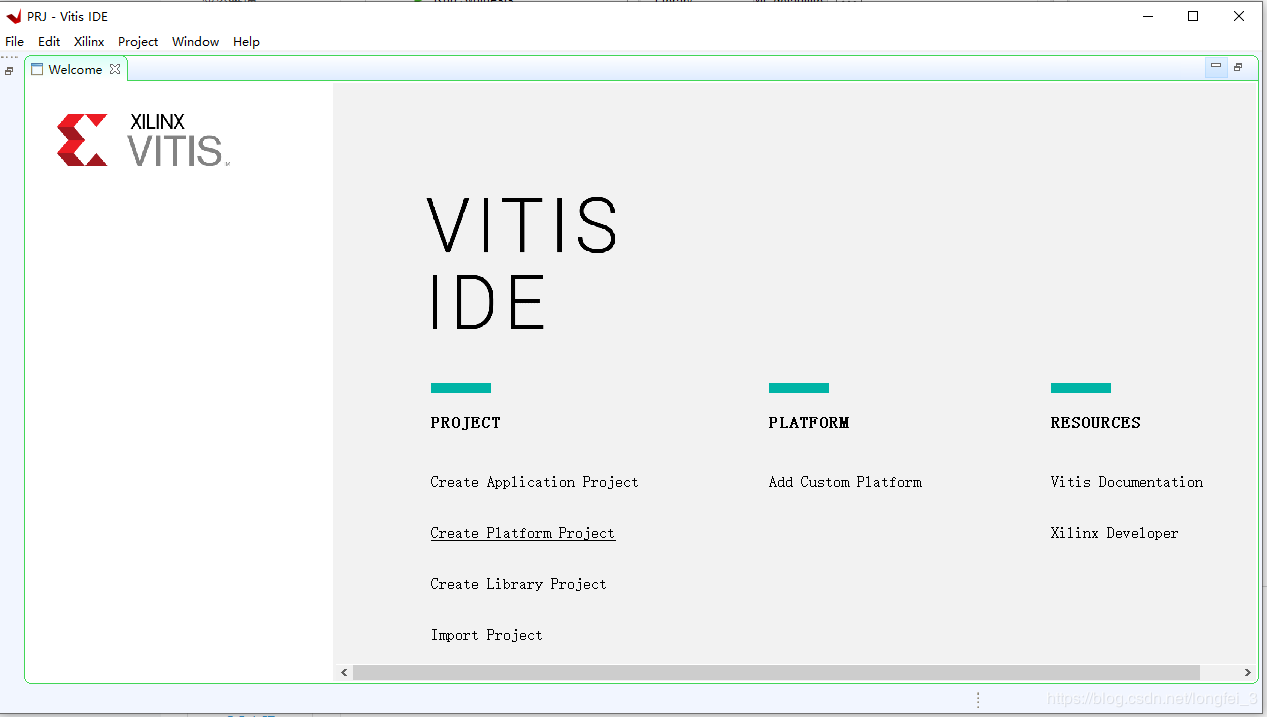

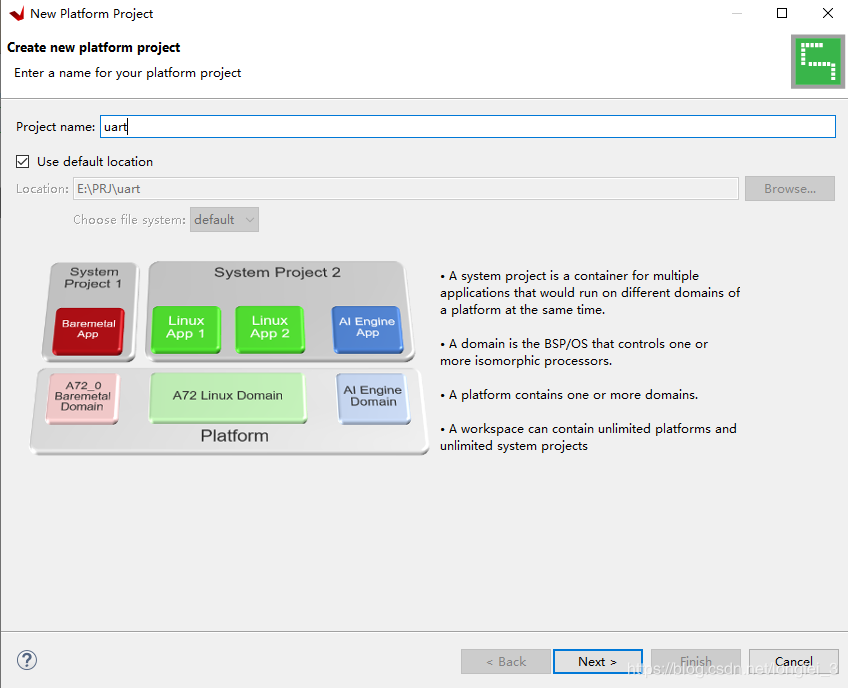

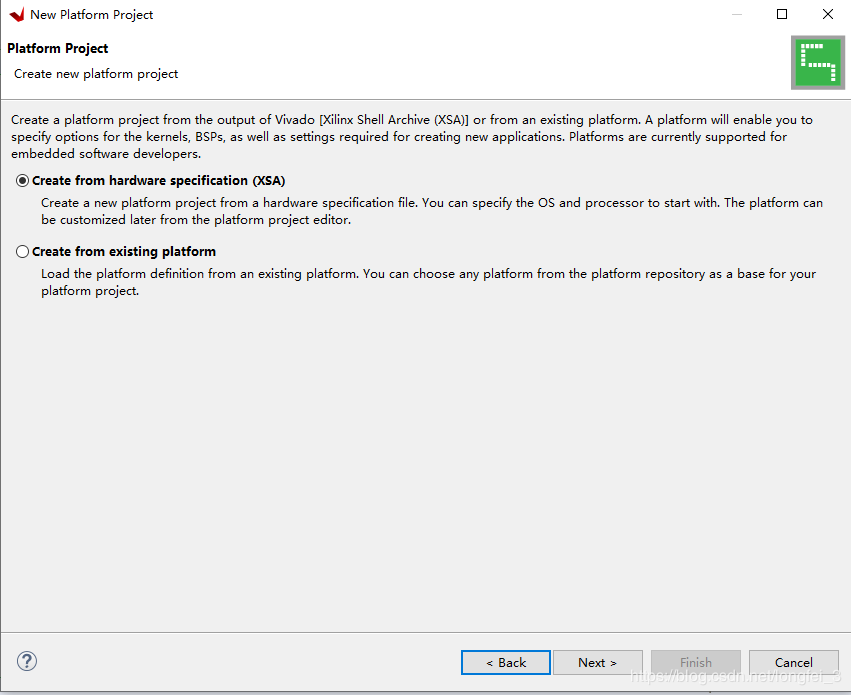

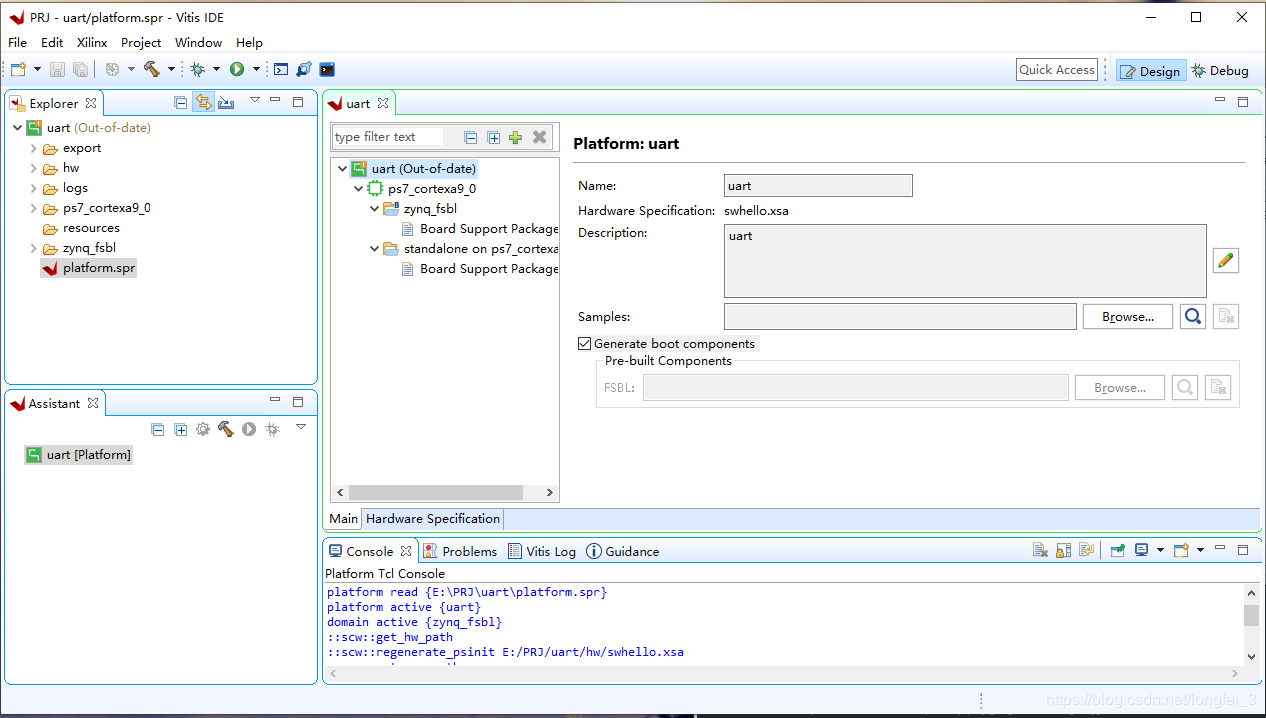

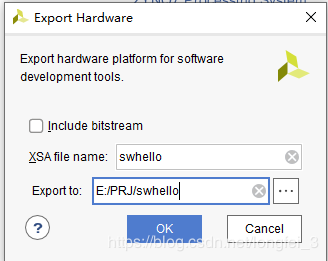

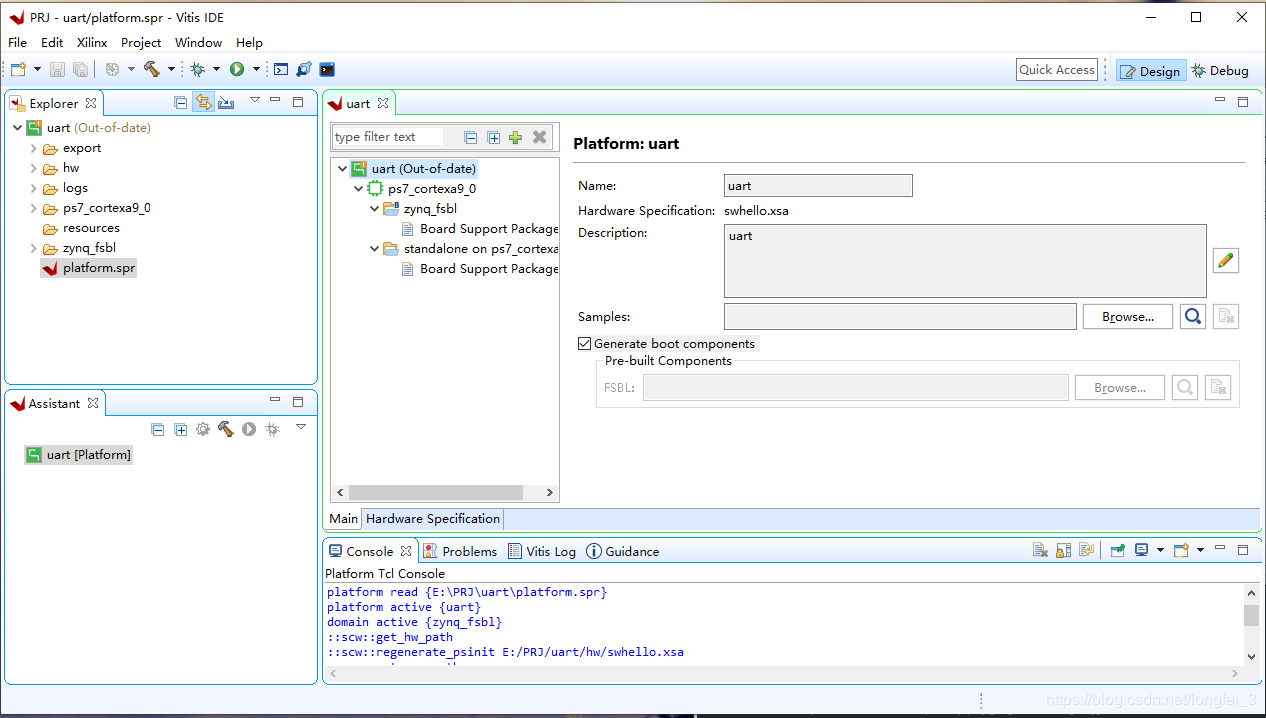

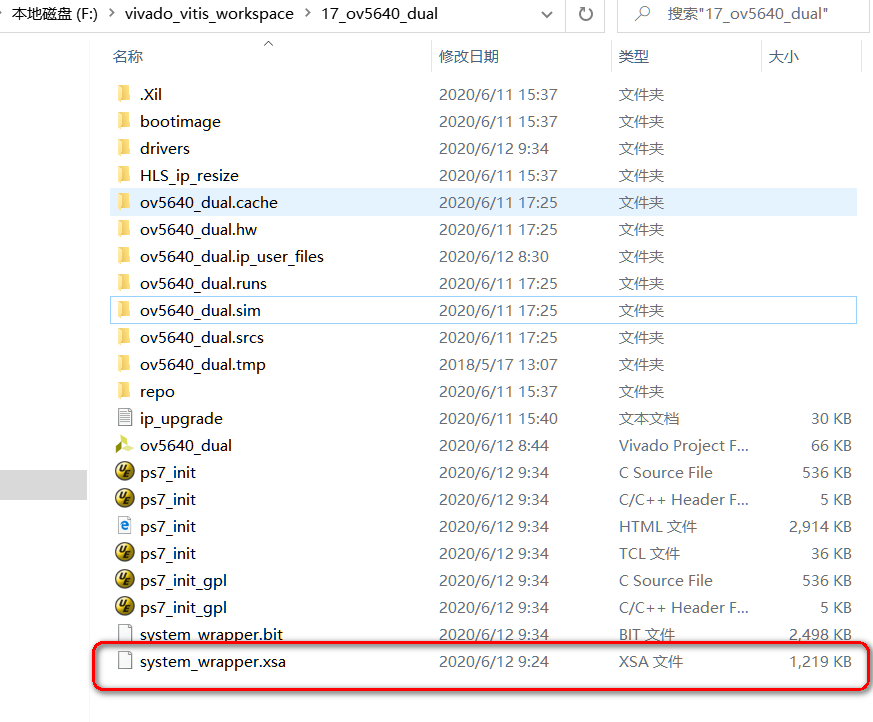

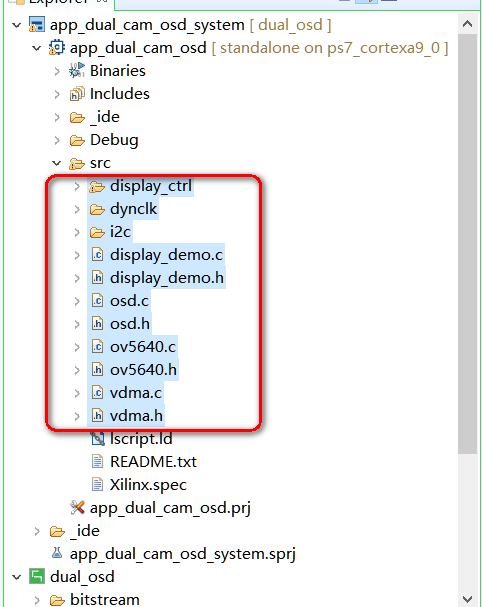

导出完成,这里开始软件操作,打开vitis先创建一个 platform project导入刚才的设计xsa文件。

这里与SDK不同,SDK是从vivado直接Launch打开,而Vitis是独立与vivado IDE的开发工具。

选择Vivado导出的设计,点击 finish完成

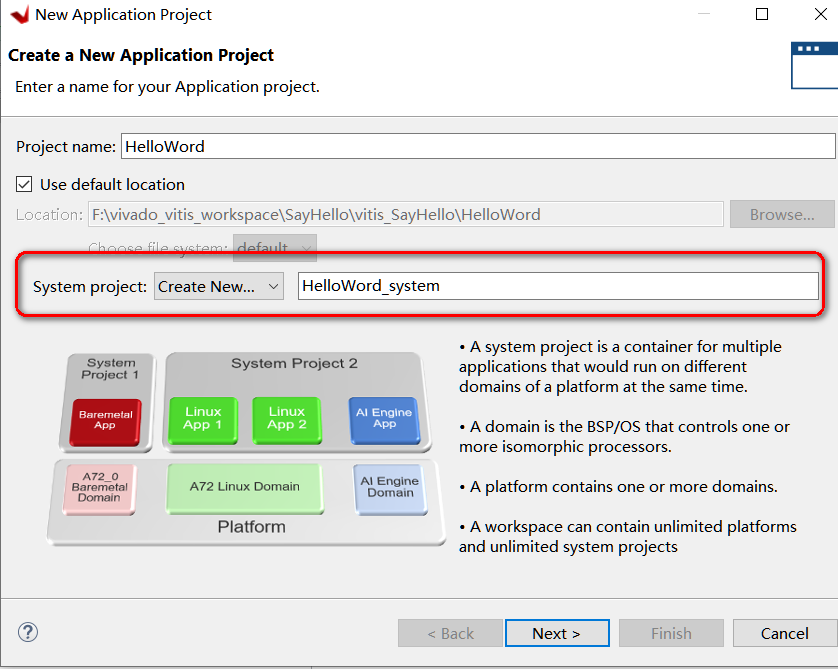

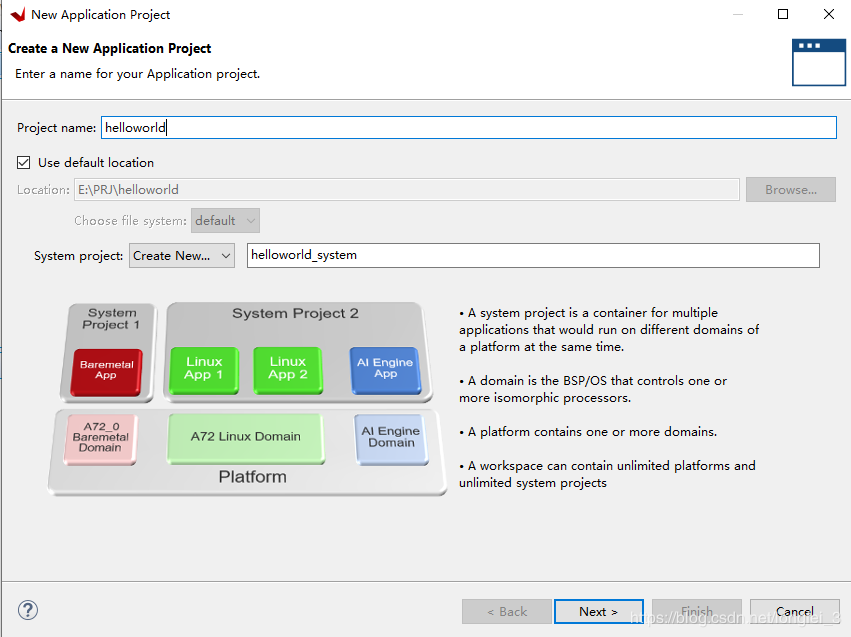

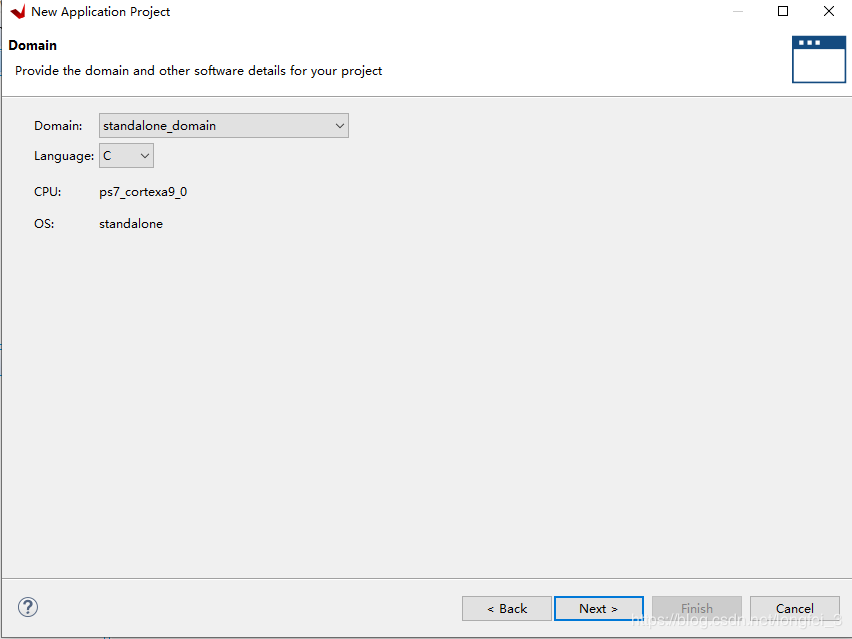

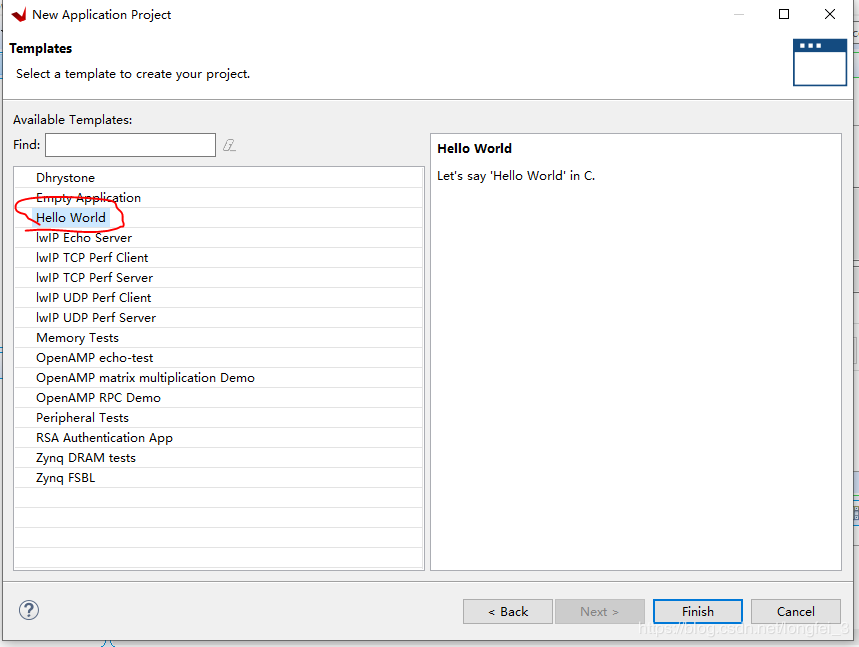

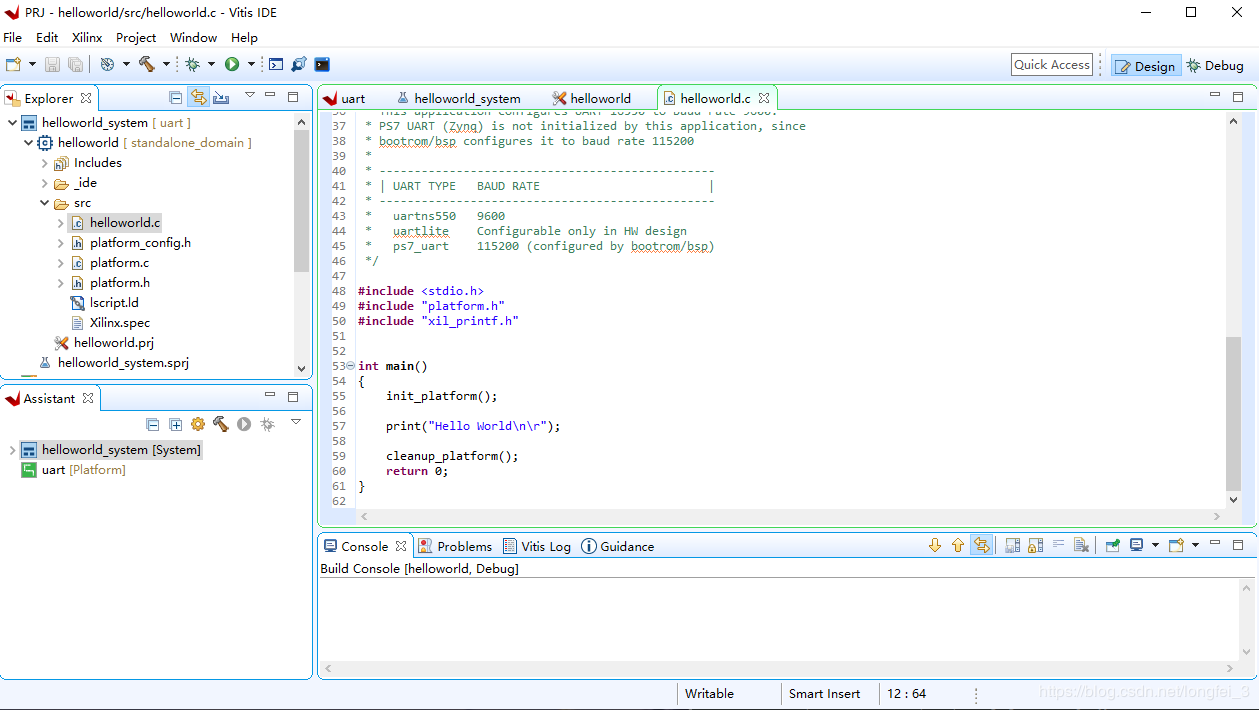

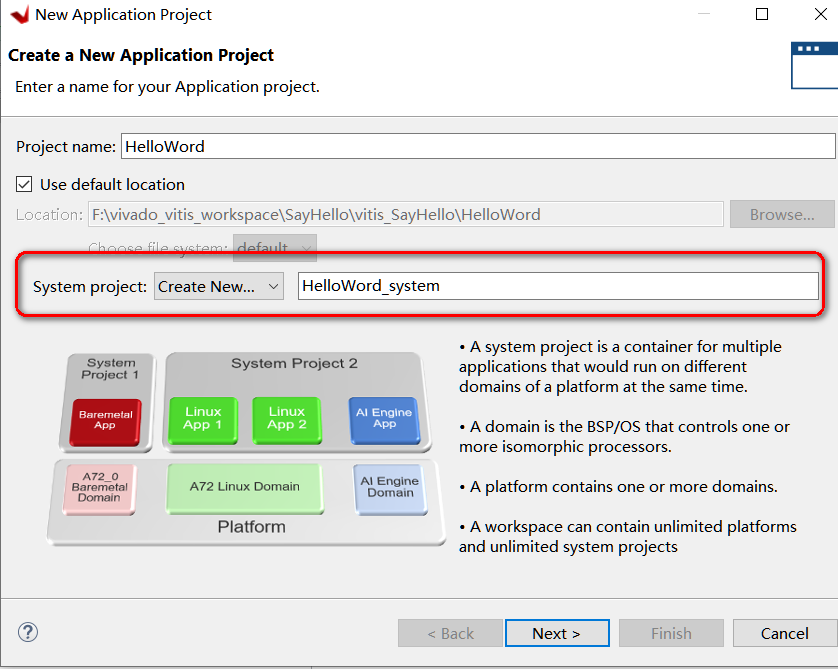

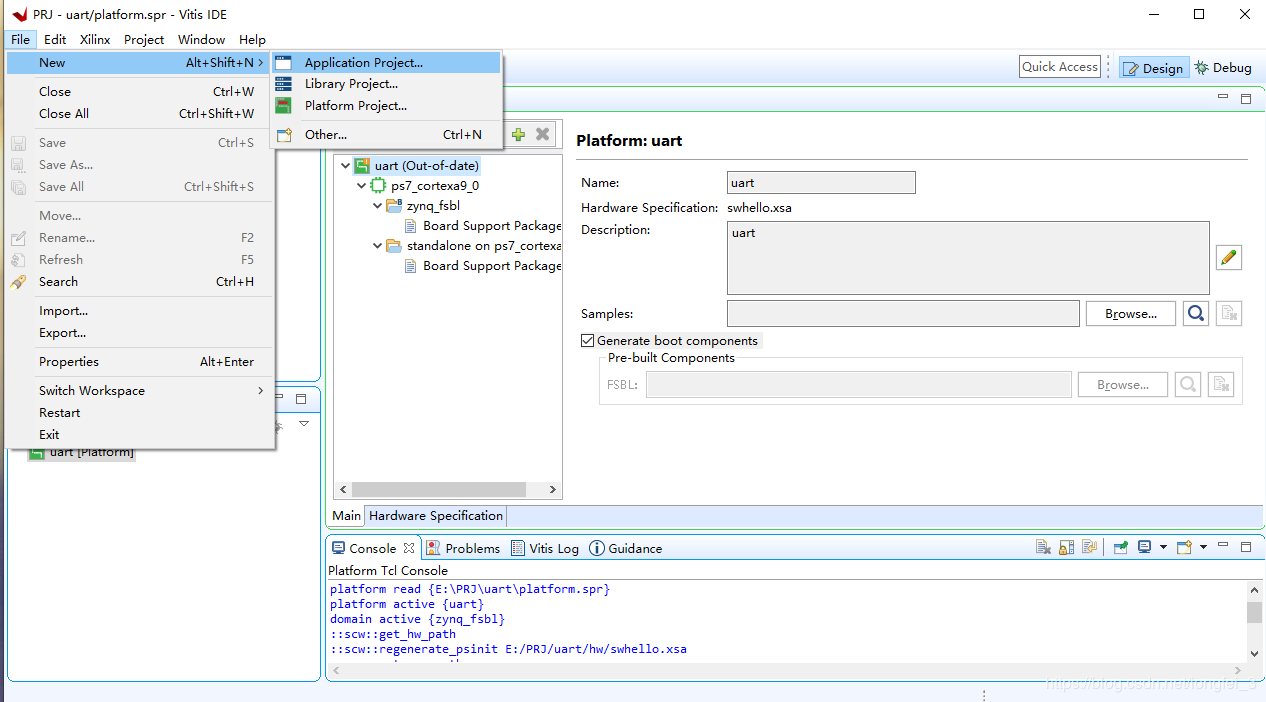

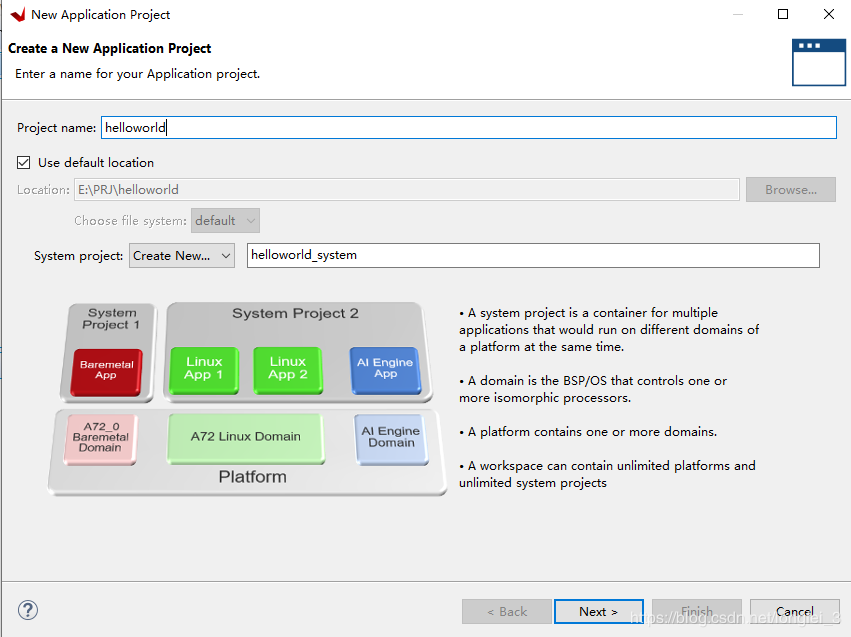

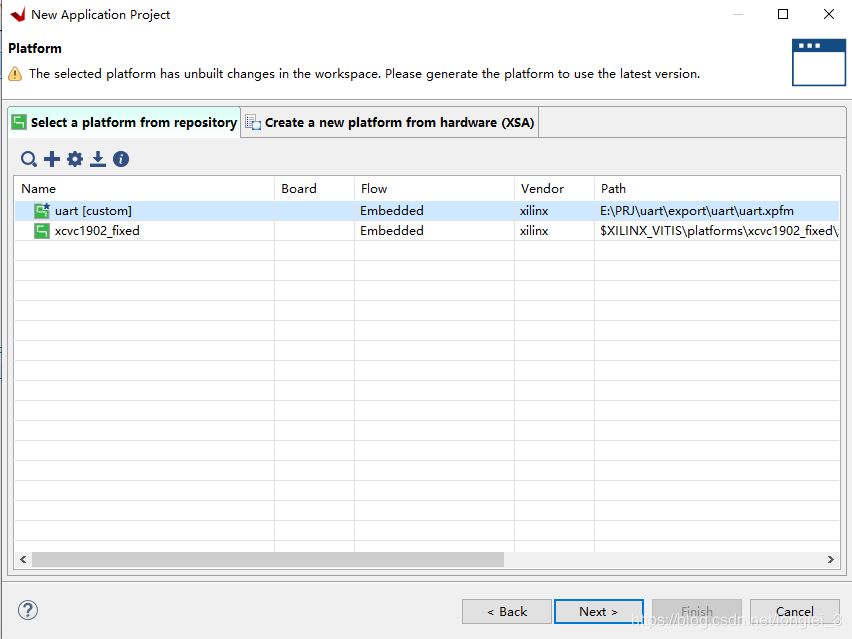

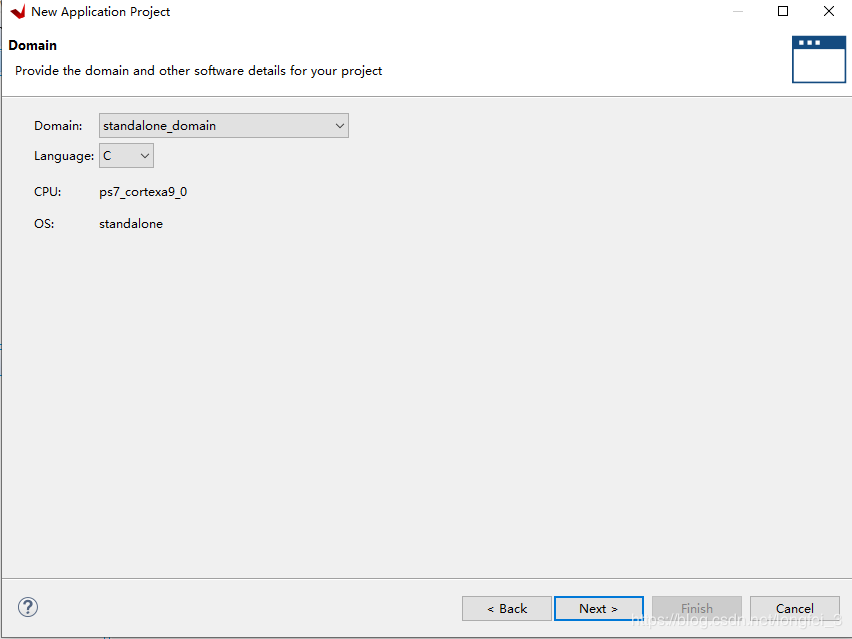

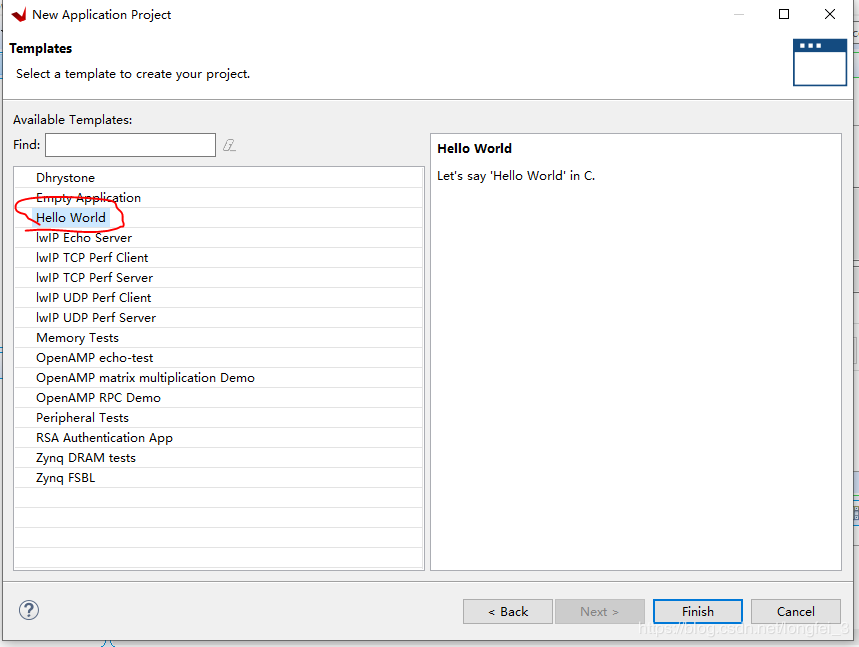

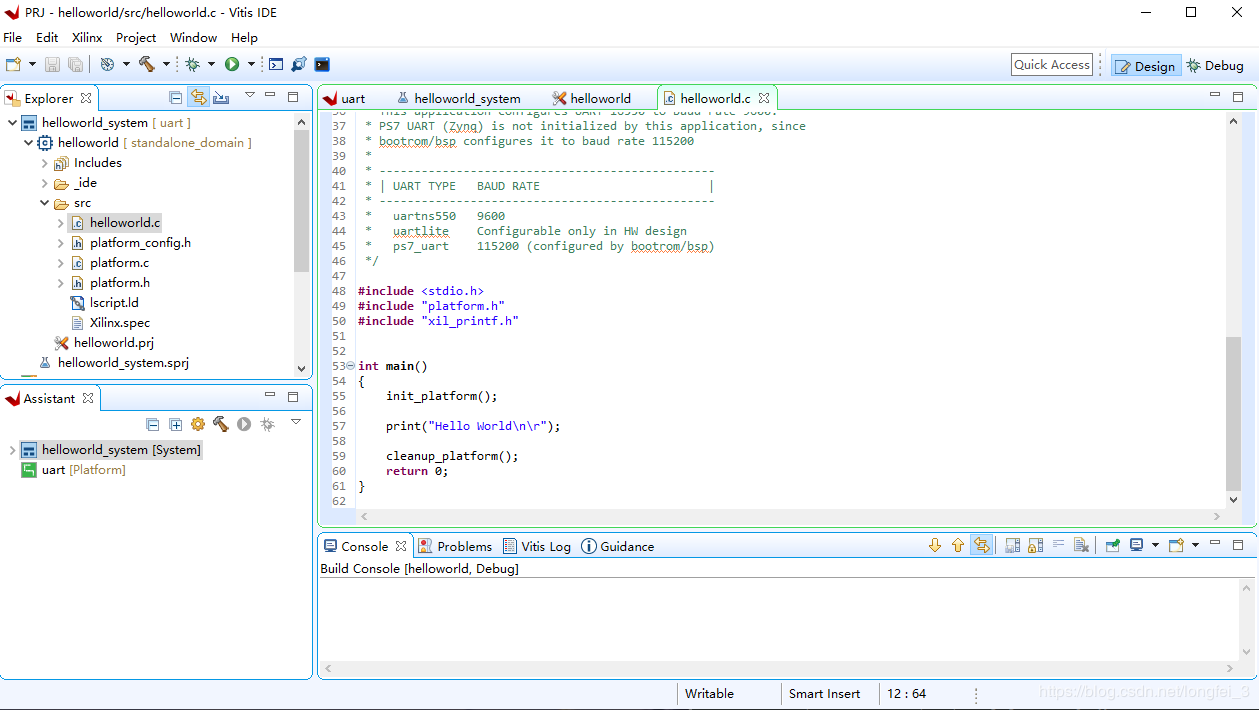

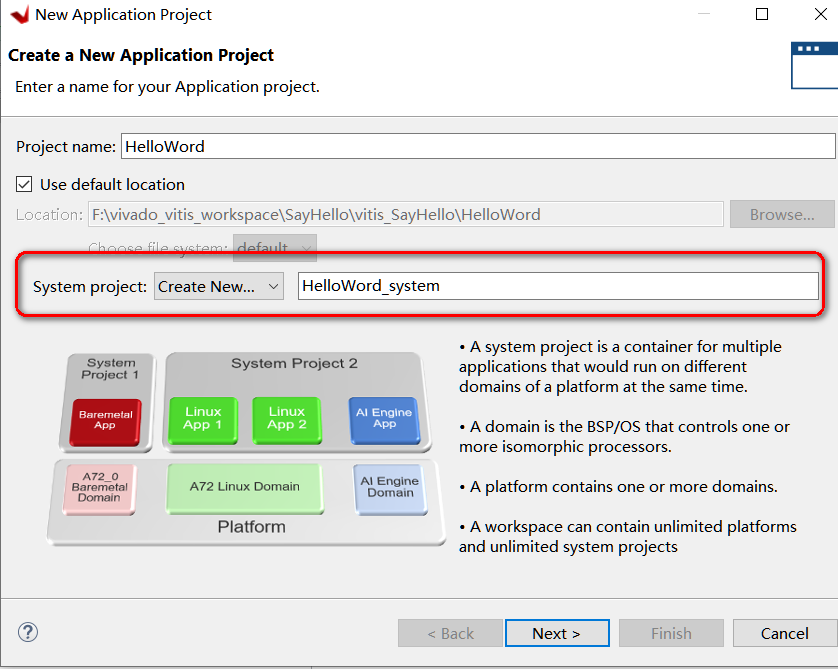

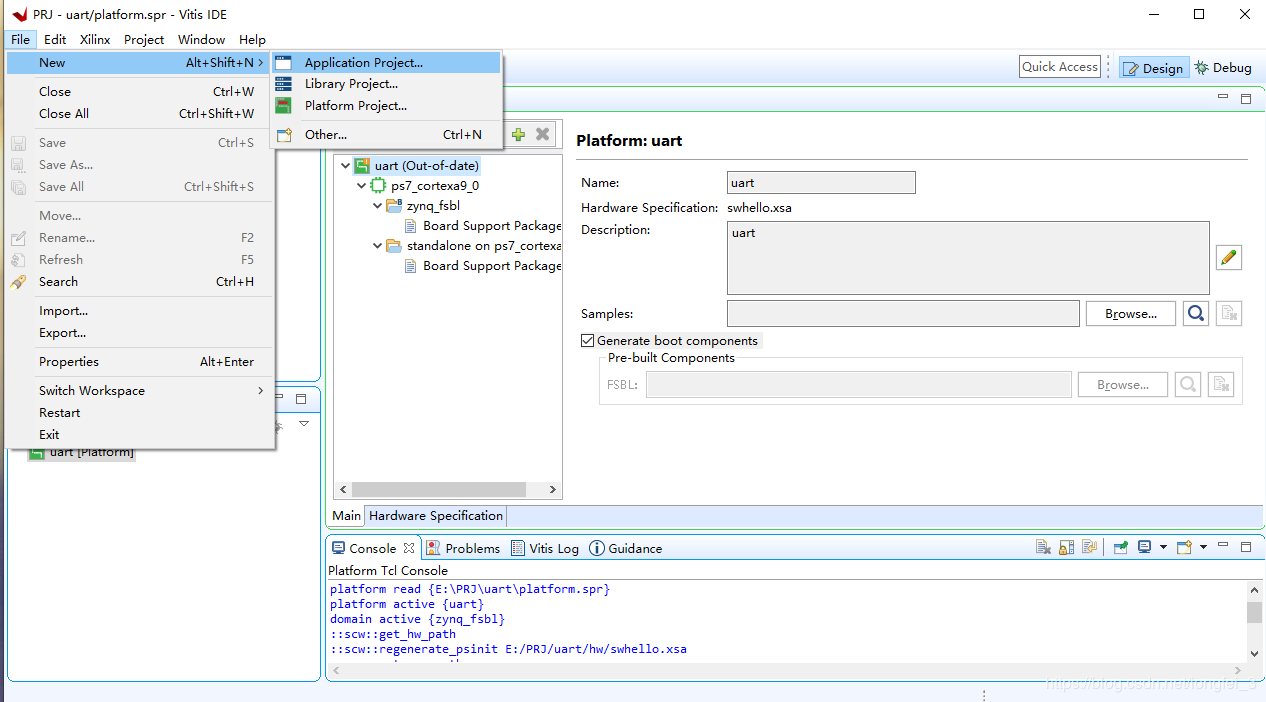

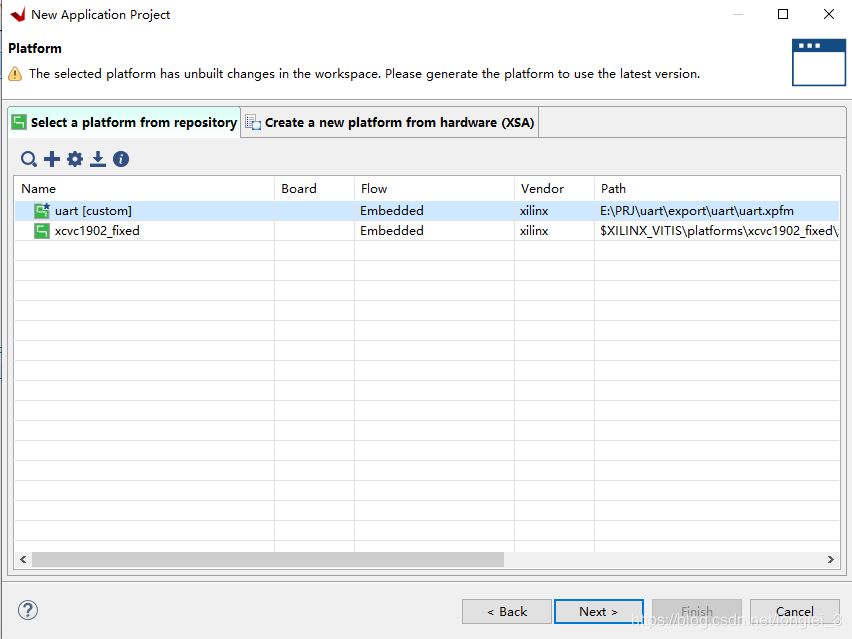

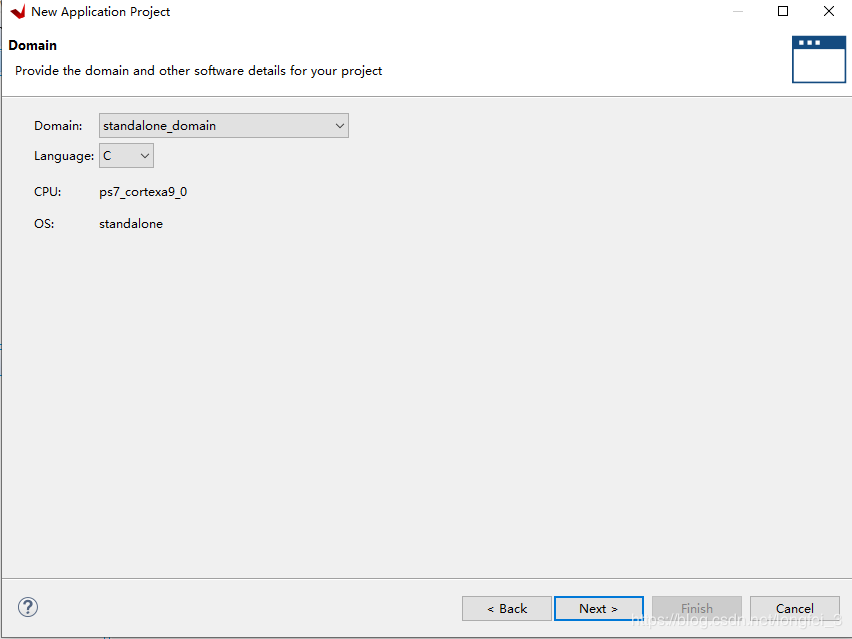

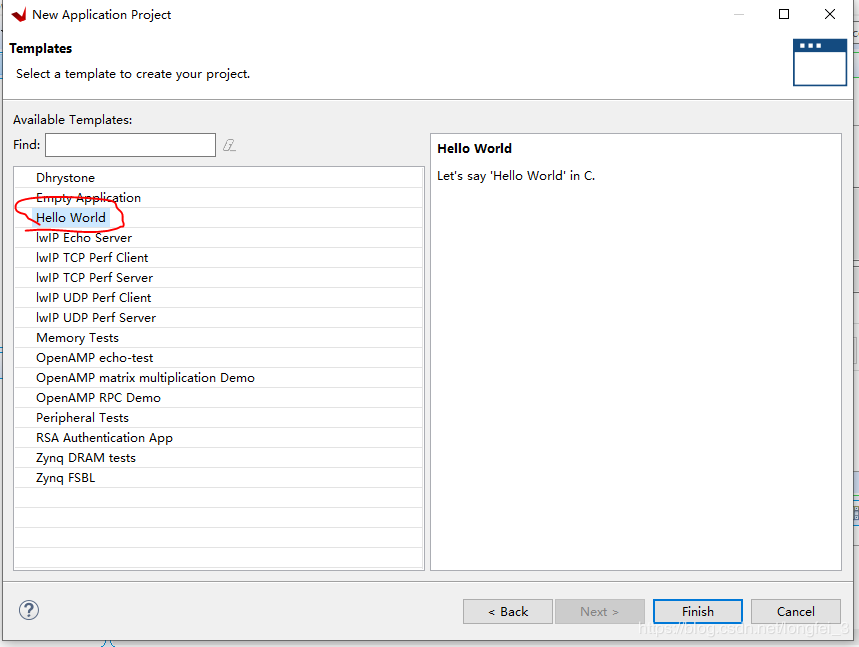

创建一个Application project:

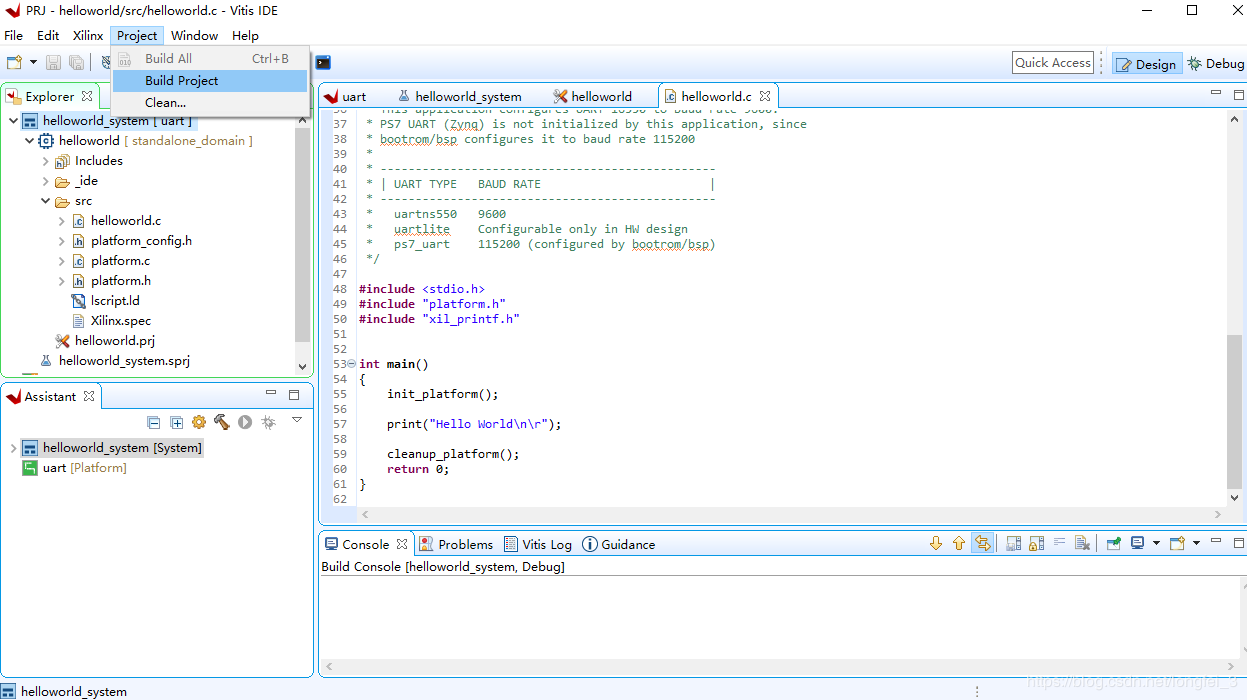

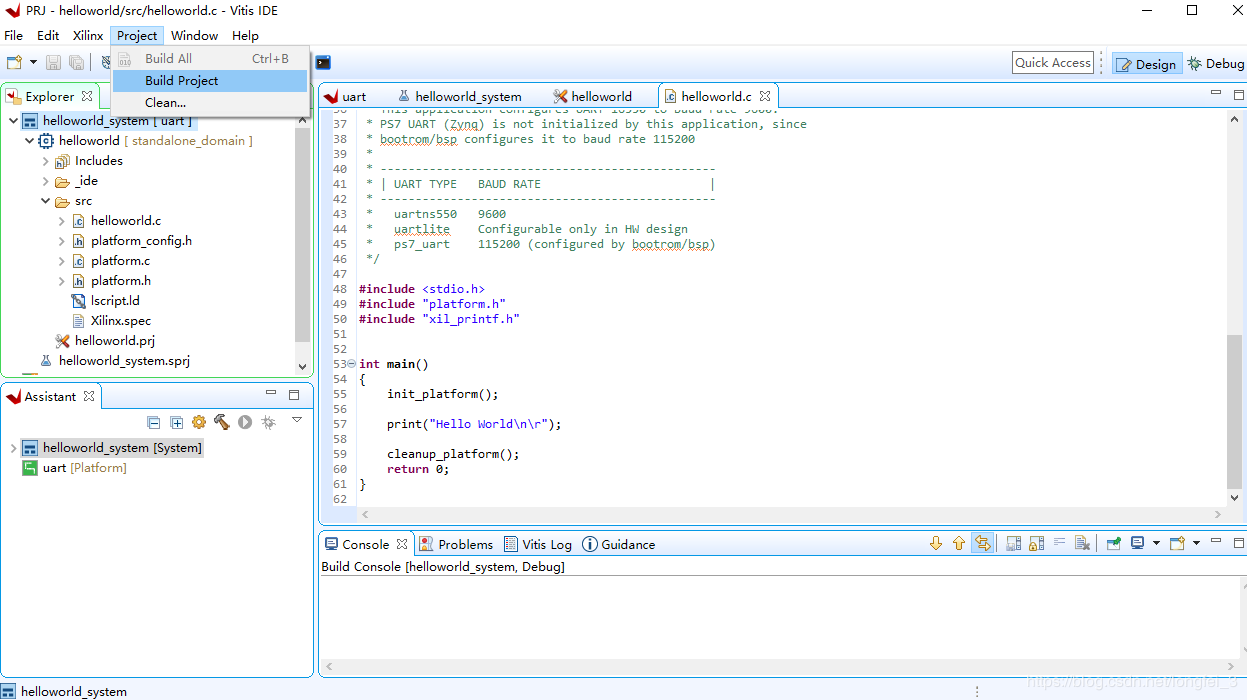

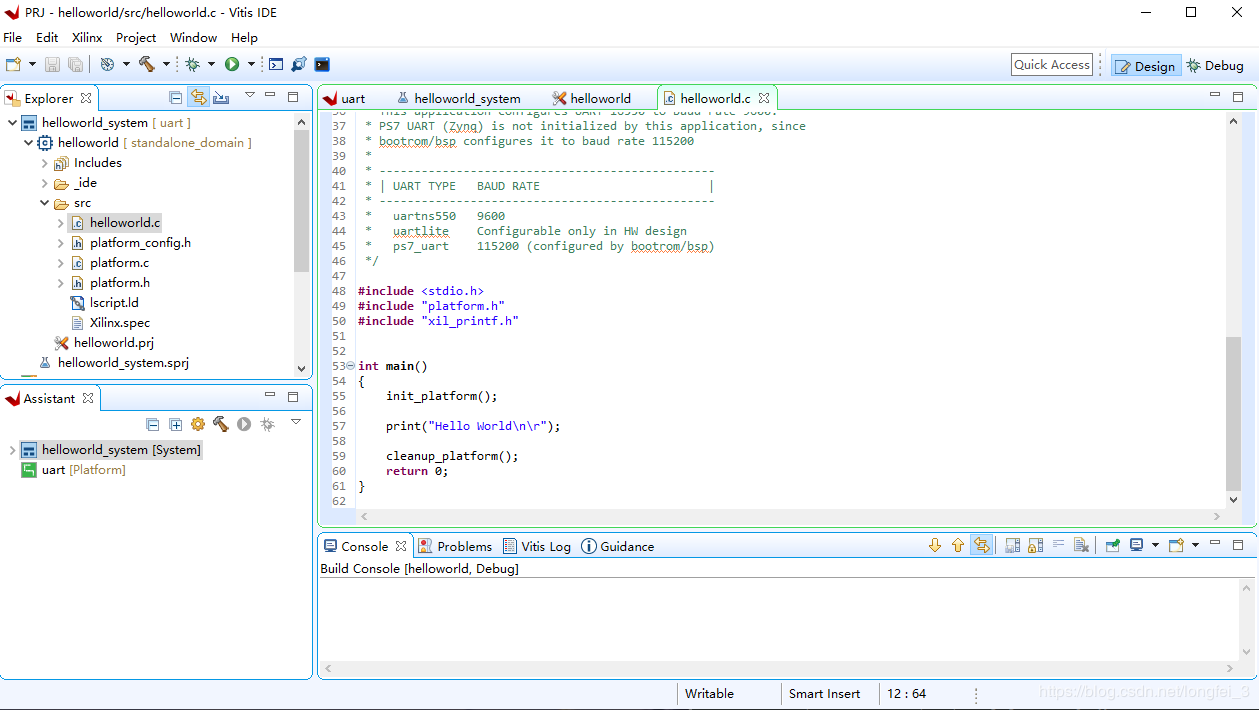

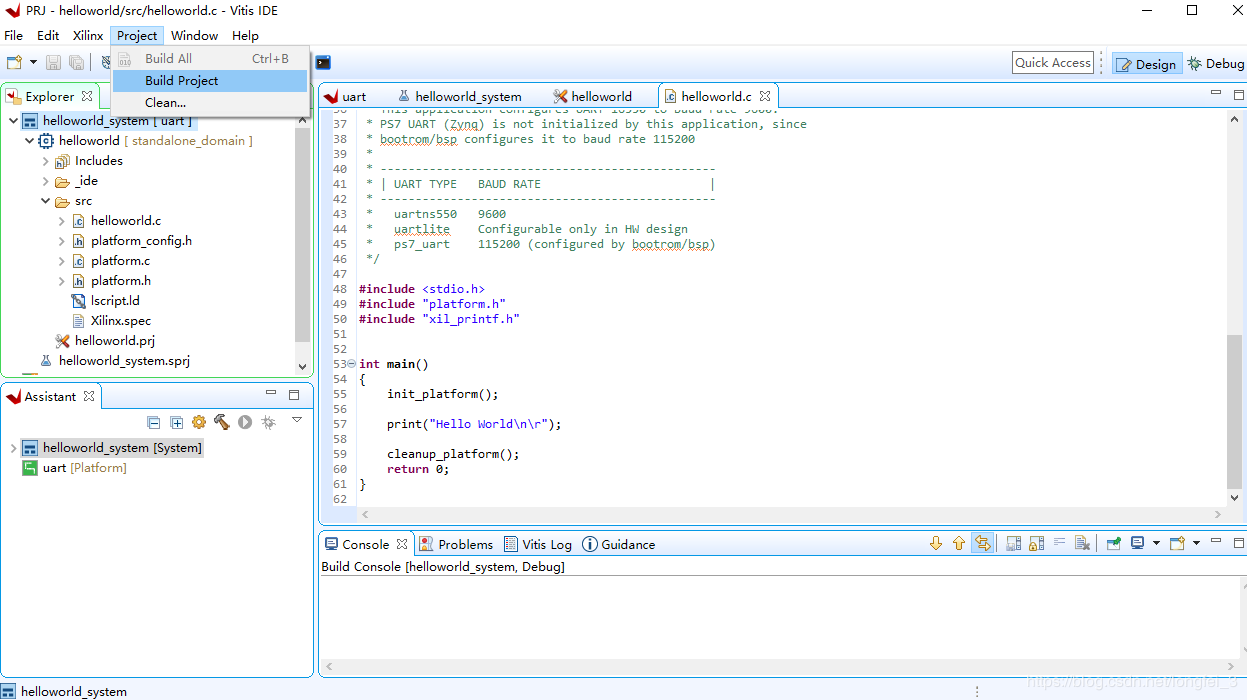

编译helloworld工程

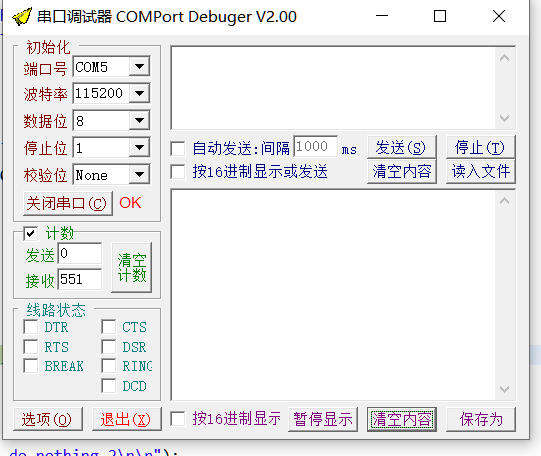

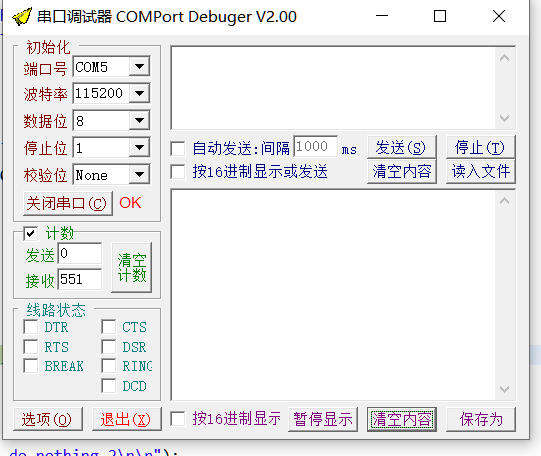

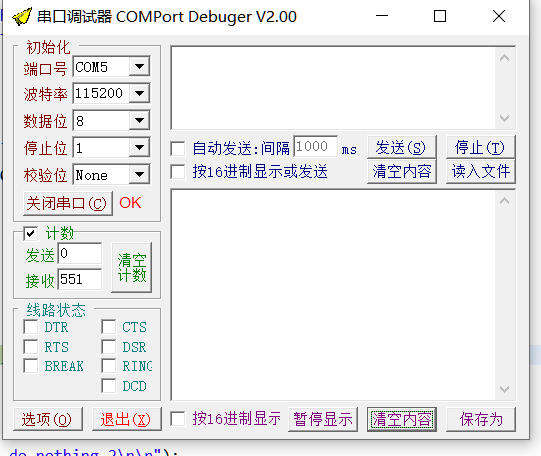

给板子接好上电,连接串口助手软件,打开串口设置如下,com口根据实际而定。

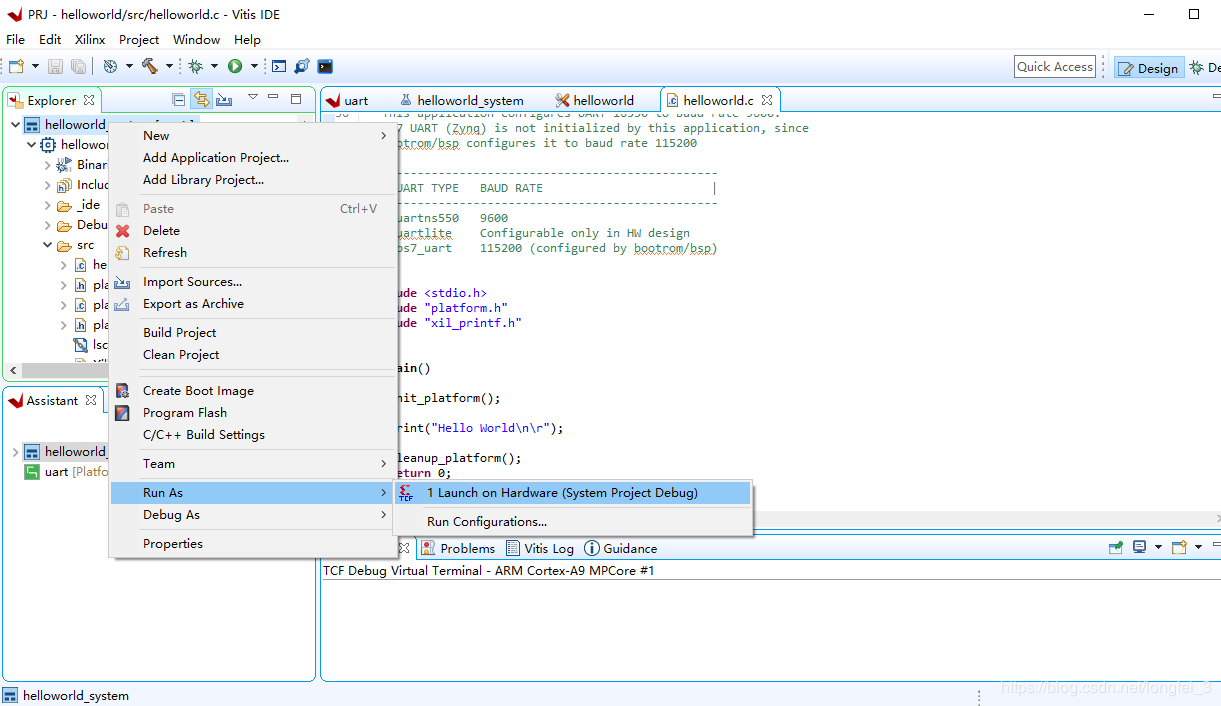

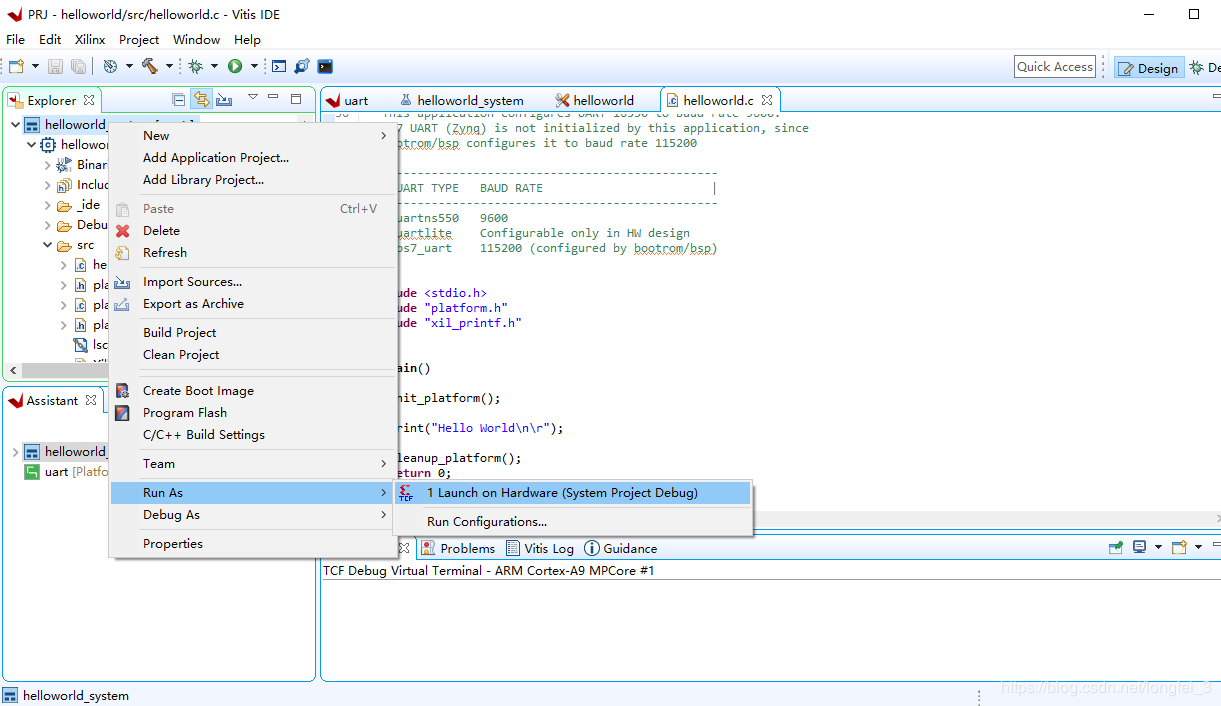

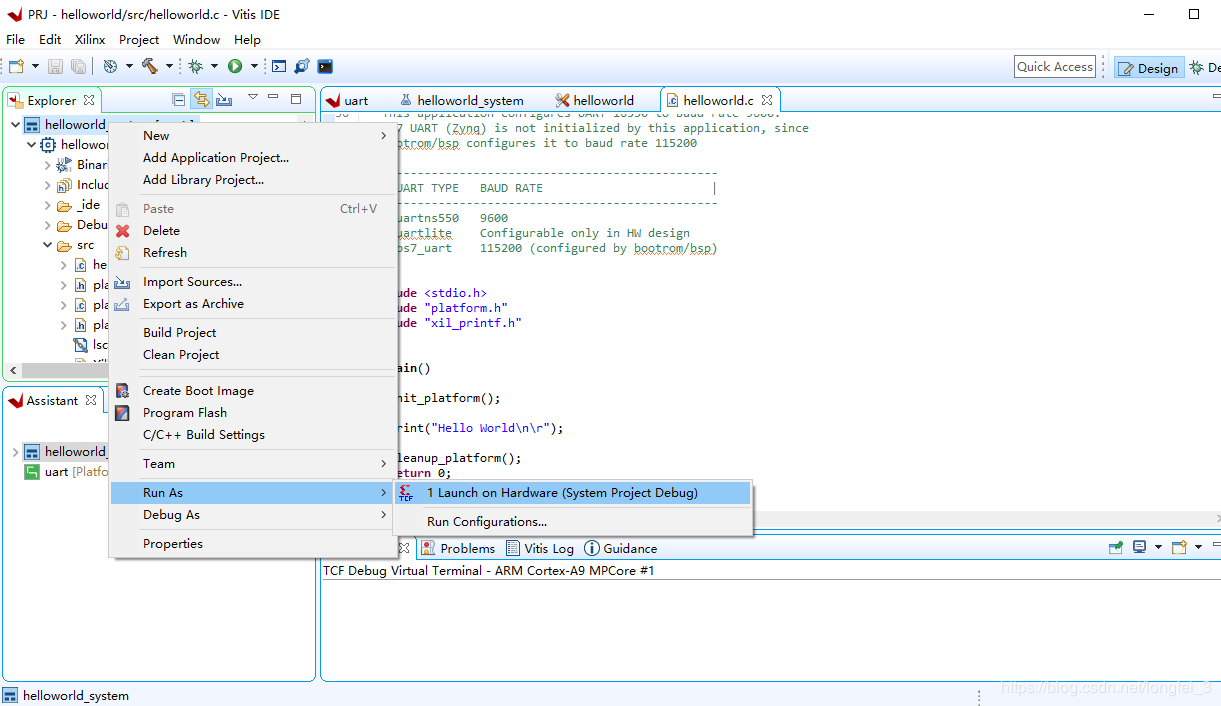

下载运行

已经输出了“hello world”

硬件加速应用程序开发流程:

对于基于FPGA的加速,Vitis核心开发套件支持用户通过API函数创建软件应用程序,例如OpenCL函数,在Alveo加速卡上运行加速硬核。Vitis核心开发套件也支持将软件程序运行在基于Linux的嵌入式处理器平台上,例如ZYNQ的UltraScale+MPSOC设备。对于嵌入式处理器平台Vitis开发套件执行模型也通过OpenCL API和基于Linux的Xilinx运行库(XRT)来调度硬核和控制数据的搬移。(加速库和xilinx运行库在GitHub上可下载)

Vitis核心开发套件可支持Alveo U50、U200、U250、U280加速卡,也支持zcu102、zcu104、zc702、zc706嵌入式处理器平台。除了以上比较流行的平台外,同时也支持自定义平台。

Vitis软件平台允许用户将数据中心应用程序移植到嵌入式平台上。Vitis核心开发套件不仅具有适用于硬核的V++编译器。也具有运行在X86主机的g++编译器和运行在Xilinx设备的嵌入式处理器的Arm编译器

Vitis与SDK对比:

系统项目指的是什么?域domain可以理解成SDK中的BSP么?

系统项目就是指在Vitis中创建的application。

Vitis软件平台SDK

可在Vitis中直接创建一个平台项目(需要添加vivado生成的XSA文件或者从平台库中添加任意平台作为基础例如vck190.xsa、zc702.xsa、zc706.xsa、zcu102.xsa、zed.xsa)SDK是从vivado工程中导出硬件平台项目

为平台添加域创建BSP

创建应用程序(通过平台的域)创建应用程序(通过BSP)

改制一个预置平台无提及

可在一个系统项目中管理多个应用程序无提及

修改并且更新硬件基本相同,工作流程可能有细微改变

在硬件上调试应用程序基本相同,工作流程可能有细微改变

在一个系统项目下运行和调试应用程序无提及

创建boot image基本相同,工作流程可能有细微改变

Flash 编程基本相同,工作流程可能有细微改变

生成设备树基本相同,工作流程可能有细微改变

通过User-Modify/Custom FSBL测试应用程序基本相同,工作流程可能有细微改变

修改域源文件基本相同,工作流程可能有细微改变

实测Vitis编译时间要比SDK编译时间略长;

Vitis实现简单的HelloWord

基于黑金ZYNQ 7020开发板创建工程,打开vivado2019.2一步步创建工程,vivado部分还是与之前一模一样没有任何改变。

创建完工程,创建同一个 Block Design工程

添加ZYNQ 核

双击ZYNQ核设置一下,这里设置跟板子一致UART1,波特率选择115200,没有用到PL,AXI也没使用。

时钟默认即可,黑金的7020最高可以跑到767Mhz。

设置完成。自动连线。

生成文件:

生成顶层文件:

至此PL部分完成了。

导出设计到软件,没有用到PL,所以不用综合生成bit文件了,这里直接导出

导出完成,这里开始软件操作,打开vitis先创建一个 platform project导入刚才的设计xsa文件。

这里与SDK不同,SDK是从vivado直接Launch打开,而Vitis是独立与vivado IDE的开发工具。

选择Vivado导出的设计,点击 finish完成

创建一个Application project:

编译helloworld工程

给板子接好上电,连接串口助手软件,打开串口设置如下,com口根据实际而定。

下载运行

已经输出了“hello world”

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报