晶振振荡器设计电路

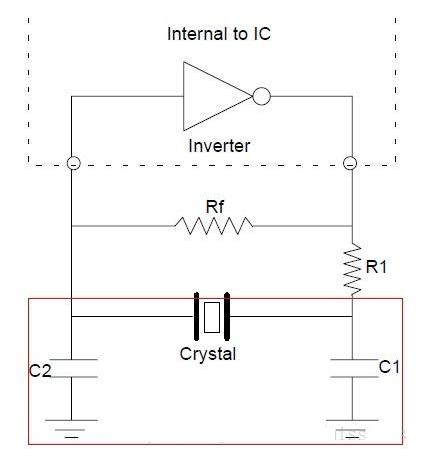

图示中,没在红方框之内部分电路一般都被集成在芯片(如STM3210xxx)内部。若电阻部分没有被集成在芯片内部,则需要考虑将电阻部分加入。Rf的值在500KΩ ~ 2MΩ。

图示的C1,C2就是为晶振工作在并联谐振状态下得到加载电容CL的电容。关于最优的加载电容CL的计算公式为:

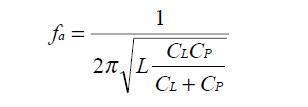

其中Cs是来自板子的干扰电容值,5pf可以作为一个典型值被带入以上公式中计算。

(2) 避免晶振振荡器的不稳定与启振问题

选择合适的C1和C2的值就能够满足以上与CL的方程(整体的思路见3)。通常需要C1和C2的值近似相等。C1和/或C2的值较大时能够增加频率的稳定性,但会减少回路增益并且可能会引起整个晶振振荡器的起振问题。

R1的主要被用来限制反相器(inverter)的输出,以保证晶振不被过分驱动。R1和C1构成划分电压电路,C1和R1的取值要尽量使反相器的输出靠近轨到轨(指器件的输入输出电压范围可以达到电源电压)且使晶振的输入要达到轨到轨的60%,通常的实践是是R1的电阻与C1的容抗相等,如R1 约等于XC1。这使晶振的输入是反相器输出的一半。通常需要确保晶振分得的电压要在晶振所能承受的范围之内,过分的驱动晶振会损害晶振。使用晶振是要参考制造商的推荐。

理想状况下,反相器会产生180°的相位偏移,但反相器固有的延迟会导致一个与这种延迟成某种比例的额外的的一个相位偏移。为了确保在在控制回路中产生360°的的相位偏移,需要使π网络(回路)产生的相位偏移少于180°。调节R1的值就可以完成这个目标。在固定C1和C2的情况下,可以通过调节R1的值来更改闭环增益和相位偏移。在某些应用中,遇到上述两种情况时R1也可被忽略。

一些IC将提到的这些器件(Rf,R1,C1,C2)都集成到了芯片内部,如此就可为晶振振荡电路的设计者免去一些担忧。在这种情况下只需要将晶振简单的连接到芯片给出的两个XTAL引脚上即可。

提示:

。选择一个有效串联电阻较小的晶振可以有利避免起振时的问题,且增加回路增益。

。缩短板上的布线路径可以减少干扰电容(Cs),这将有利于减小起振问题,同时有利于晶振振荡电路频率的稳定性。

。为了确保晶振振荡器起振良好及振荡频率的稳定性,需要在适用的温度和电压范围测试晶振振荡器电路,必要时更改各器件的值。

。优化R1值的推荐方式是提前计算出C1和C2的值并用一个分压计代替R1,设置分压计的初始值近似为XC1。在晶振起振和维持晶振振荡器稳定频率的条件下,必要时调整分压计。

。要想设计出最好的晶振振荡电路,联系制造商了解晶振的精确的特性再根据以上指标来设计。

(3) 计算C1和C2的思路

根据MCU的系统时钟(SYSCLK)或者与晶振振荡器关联的时钟需求值(芯片会告知)依据fa的计算公式计算出CL,再有计算CL的公式和C1与C2近相等的原则得出C1和C2的值。

在为芯片设计晶振振荡器的电路时,首先查看与晶振相连引脚内部都集成了哪些部分,Rf与R1是否还需要在外部设计。

晶振振荡器设计电路

图示中,没在红方框之内部分电路一般都被集成在芯片(如STM3210xxx)内部。若电阻部分没有被集成在芯片内部,则需要考虑将电阻部分加入。Rf的值在500KΩ ~ 2MΩ。

图示的C1,C2就是为晶振工作在并联谐振状态下得到加载电容CL的电容。关于最优的加载电容CL的计算公式为:

其中Cs是来自板子的干扰电容值,5pf可以作为一个典型值被带入以上公式中计算。

(2) 避免晶振振荡器的不稳定与启振问题

选择合适的C1和C2的值就能够满足以上与CL的方程(整体的思路见3)。通常需要C1和C2的值近似相等。C1和/或C2的值较大时能够增加频率的稳定性,但会减少回路增益并且可能会引起整个晶振振荡器的起振问题。

R1的主要被用来限制反相器(inverter)的输出,以保证晶振不被过分驱动。R1和C1构成划分电压电路,C1和R1的取值要尽量使反相器的输出靠近轨到轨(指器件的输入输出电压范围可以达到电源电压)且使晶振的输入要达到轨到轨的60%,通常的实践是是R1的电阻与C1的容抗相等,如R1 约等于XC1。这使晶振的输入是反相器输出的一半。通常需要确保晶振分得的电压要在晶振所能承受的范围之内,过分的驱动晶振会损害晶振。使用晶振是要参考制造商的推荐。

理想状况下,反相器会产生180°的相位偏移,但反相器固有的延迟会导致一个与这种延迟成某种比例的额外的的一个相位偏移。为了确保在在控制回路中产生360°的的相位偏移,需要使π网络(回路)产生的相位偏移少于180°。调节R1的值就可以完成这个目标。在固定C1和C2的情况下,可以通过调节R1的值来更改闭环增益和相位偏移。在某些应用中,遇到上述两种情况时R1也可被忽略。

一些IC将提到的这些器件(Rf,R1,C1,C2)都集成到了芯片内部,如此就可为晶振振荡电路的设计者免去一些担忧。在这种情况下只需要将晶振简单的连接到芯片给出的两个XTAL引脚上即可。

提示:

。选择一个有效串联电阻较小的晶振可以有利避免起振时的问题,且增加回路增益。

。缩短板上的布线路径可以减少干扰电容(Cs),这将有利于减小起振问题,同时有利于晶振振荡电路频率的稳定性。

。为了确保晶振振荡器起振良好及振荡频率的稳定性,需要在适用的温度和电压范围测试晶振振荡器电路,必要时更改各器件的值。

。优化R1值的推荐方式是提前计算出C1和C2的值并用一个分压计代替R1,设置分压计的初始值近似为XC1。在晶振起振和维持晶振振荡器稳定频率的条件下,必要时调整分压计。

。要想设计出最好的晶振振荡电路,联系制造商了解晶振的精确的特性再根据以上指标来设计。

(3) 计算C1和C2的思路

根据MCU的系统时钟(SYSCLK)或者与晶振振荡器关联的时钟需求值(芯片会告知)依据fa的计算公式计算出CL,再有计算CL的公式和C1与C2近相等的原则得出C1和C2的值。

在为芯片设计晶振振荡器的电路时,首先查看与晶振相连引脚内部都集成了哪些部分,Rf与R1是否还需要在外部设计。

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报