系统硬件设计

3.1 VGA接口

VGA是一种D型接口,可传输VGA,SVGA,XGA,SXGA等图像格式。VGA接口共有15针,分成3排,每排5个。VGA接口是显卡应用最为广泛的接口类型。

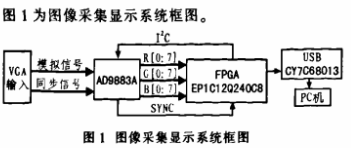

系统VGA模拟信号输入与A/D转换器相连,A/D转换器的RAIN,GAIN,BAIN分别与模拟接口的R,G,B相连。

3.2 A/D转换接口

由于A/D转换器的采样率较高,相应的输出数据速率也高。在系统最高要求下,像素点频率为108 MHz,相应的数据速率为324 Mbit/s(R,G,B 3个分量,每个分量8 bit)。同时,由于采集图像数据,要求较高的行同步时。如果某一行图像数据丢失一个或多个点数据,整个图像就会产生倾斜。因此需突发存储每行数据,保证数据不丢失。其突发长度为图像的水平分辨率。

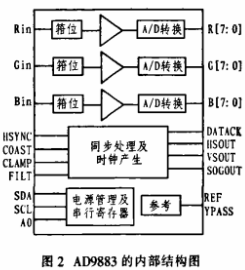

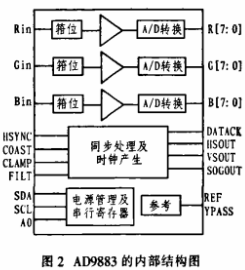

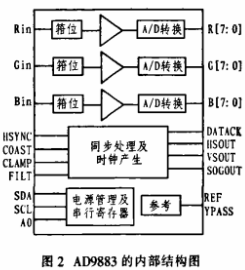

该采集模块的A/D转换器采用AD9883A。该器件是专门针对采集模拟R,G,B信号,并将其数字化显示或为其他应用而设计的。该器件具有采样精度为8 bit的3路通道,最高采样率为140 MS/s,300 MB的模拟带宽,并且优化了计算机及工作站的图像接口,可采样分辨率为1280×1024。刷新率为75 Hz的视频信号。基于AD9883A的电路可为高清电视(HDTV)提供良好的计算机接口和高性能视频设备的前端扫描转换器。AD9883A内部结构如图2所示。

输入VGA图像信号后,先箝位以调整其直流偏移分量,使输入电平满足A/D转换模块要求。AD9883A内部具有3个高带宽、8 bit分辨率、110MS/s转换速率的A/D转换器,对箝位后的模拟视频信号进行采样、量化、编码,得到数字视频信号,通过寄存器调整采样相位,获得最佳转换效果。

采样时钟通过配置锁相环(PLL)生成,可使用行同步信(HSYNC)作为参考时钟,然后经分频,得到A/D转换器所需的采样时钟。AD9883A内部集成一个超低抖动锁相环,在所有工作模式下时钟抖动不到点时钟的5%。AD9883A时钟的稳定性对于系统产生清晰稳定的图像十分重要。由于AD9883A具有一个宽范围,可调的锁相环,能够产生12~140 MHz的像素点频率,因此AD9883A支持丰富的输入图像格式。

AD9883A的同步信号产生模块能识别多种同步信号输入模式,同时也可根据需要灵活设定同步信号的输出模式。通过I2C总线时序,方便实现器件初始化。

A/D转换模块能采集多种VGA图像格式,但不能自动检测图像格式,必须通过它提供的I2C接口进行设置,FPGA自动检测图像格式,并设置A/D转换模块。另外,不同格式的VGA图像中场同步信号的有效脉冲电平不统一,A/D转换模块可自动检测输入的场同步信号极性并存储到内部寄存器,通过读取该寄存器判断输入VGA信号场同步的极性。A/D转换模块输出的场同步信号实现输入场同步信号的反相。FP-GA内部的同步逻辑只支持一种有效电平的场同步信号,因此在采集前需读取A/D转换器内部寄存器来判断当前输入同步信号的极性,以确定是否需要设置A/D转换器对场同步信号进行反相处理。

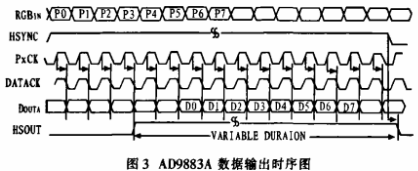

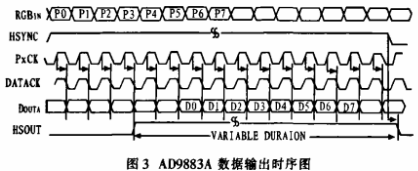

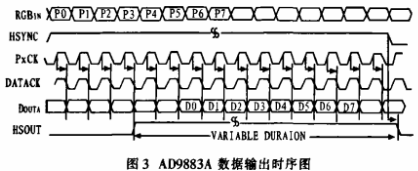

输入的模拟视频信号经箝位处理、增益与偏置控制后,AD9883内部3个高精度高速A/D转换器在锁相环产生的采样时钟作用下,转换为显示所需的数字视频信号。图3为其数据输出的时序,在输出数据时钟DATACK的下降沿,采样及量化其对应的信号,量化后的数据在时钟上升沿输出:接口电路以DATACK的上升沿准确锁存图像数据,实现数字化图像的采集。考虑到像素时钟和数据的相位延迟等问题,可用HSYNC消除边沿定时的不确定性。要注意的是,AD9883A有一个数据输出通道,在输出数据有效之前必须清空通道,从而导致在输出每行有效数据之前将输出4组无效数据,可通过对时钟计数避免输出这些无效数据。

3.3 FPGA控制器设计

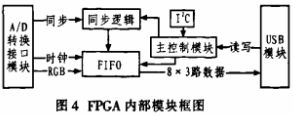

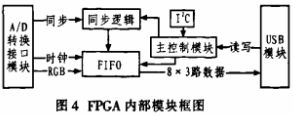

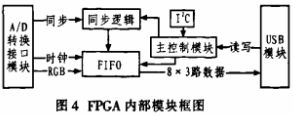

主控FPGA产生系统所需的控制信号,保证各个模块协涮工作。该系统设计采用EP1C12Q240C8型FPGA。其内部模块框图如图4所示。

FPGA内部由主控制、A/D转换接口、FIFO,以及USB等模块组成。主控制模块负责协调各模块之间的工作。A/D转换接口模块接收A/D转换模块输出的数据和同步信号并保证图像数据的行、场同步,FIFO模块采用pingpong的方式读取A/D转换传输的8×3路数字信号,然后USB输出接口模块输出高速数据。

3.4 输出显示设计

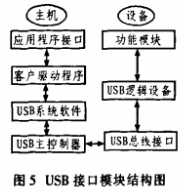

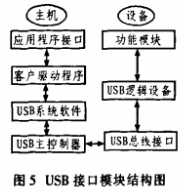

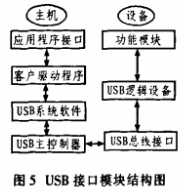

USB接口模块为应用程序和功能性设备提供可靠接口,USB体系可分为USB主机和USB设备两部分,其模块结构图如图5所示。

USB接口器件选用Cypress公司的EZ-USB FX2器件CY7C68013A。该器件内部集成USB 2.0收发器智能串行引擎SIE,增强型8051控制器,通用可编程接口(GPIF),8.5 KB的RAM和4 KB的FIFO存储器,FX2系列的独创性设计可满足USB2.0的总线带宽。

该系统以传输控制信息和视频数据为主,可将器件置于Slave FIFO模式,USB串行接口引擎(SIE)直接与Slave FIFO传输数据,Slave FIFO再与外部设备(FPGA)通信,从而实现PC机与FPGA的通信,并显示视频数据。

3.5 USB设备驱动开发

USB设备驱动程序嘲是连接USB外设、操作系统以及用户应用程序的桥梁,是USB设备连接到计算机系统的软件接口。EZ-USB FX2器件CY7C68013A的设备驱动程序有两种:一种用来在设备接入时从主机下载的固件存储RAM中,称为同件下载驱动程序(wdgtldr.sys);另一种是在设备重新列举后加载的通用设备驱动程序(ezu***.sys),应用软件通过该设备驱动程序与FX2通信。编写上位机程序的一个类USB Video Class,它对应于硬件CY7C68013A的一个同件,Video Class协议的目的是给USB接口的视频设备提供统一的数据交换规范,这样CY7C68013A接入PC后就无需ezu***.sys,而是使用PC自带的Video驱动将其识别为Video设备。

固件的程序代码既可通过外部E2PROM下载,也可通过主机下载,这里选用从主机下载。其中,USB Video Class协议是主机端通过向设备端获取描述符(Descriptor)来得到视频设备端的结构及其所支持的功能。而控制这些功能模块,配置数据源和数据流,则需通过Request(包括所有USB设备都需要支持的Standard Device Requests和Class与相关的Class Specific Requests)完成。

操作系统通过驱动程序实现对Video Class的支持。Video Class驱动的整体框架分为两部分:一部分是负责处理模块的初始化,处理USB总线上的Descriptor和Requests的交互,包括USB总线上的控制和查询包的接收、解释、分配和应答:另一部分是在初始化中启动的一个独立的内核线程。负责执行具体的控制指令,获取和传输图像数据。

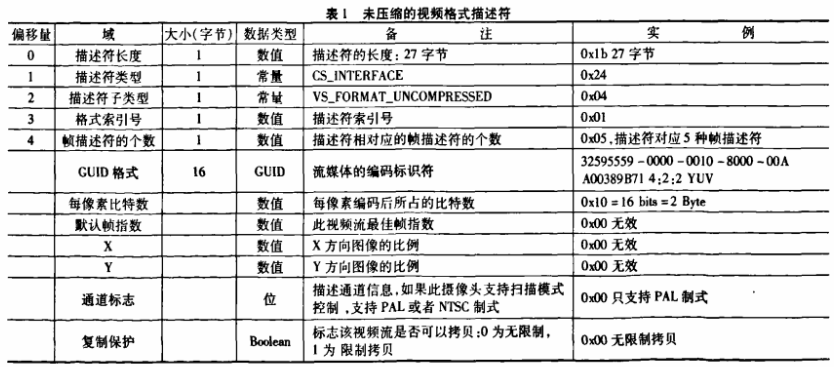

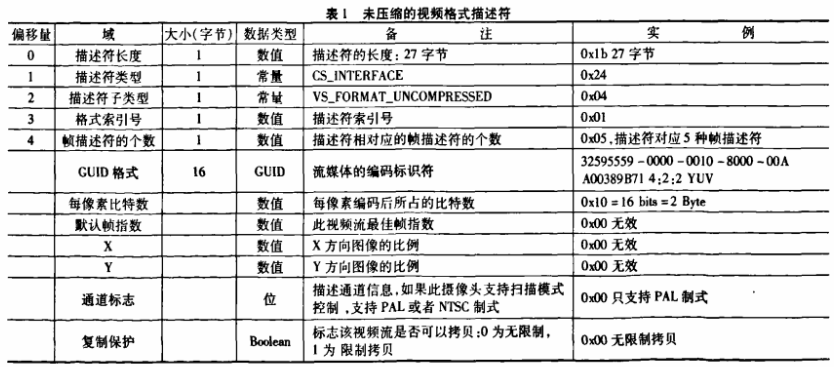

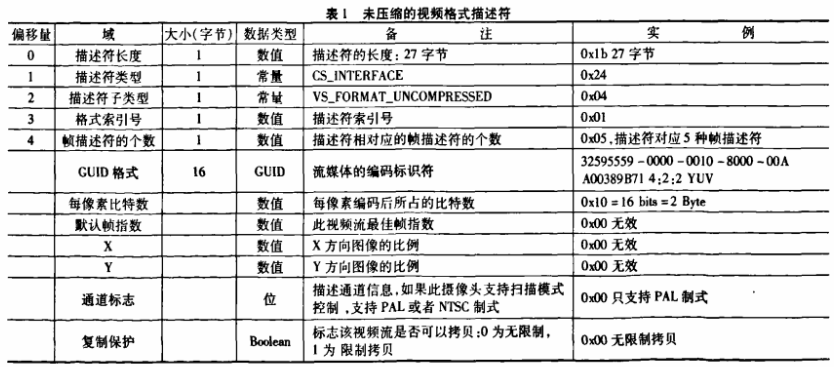

表1给出了USB Video Class程序中Uncompressed Video Format Descriptor(未压缩的视频格式描述符)的相关定义和实例。这个描述符定义了一种特殊的视频流的特性,用于定义未缩视频的信息,包括所有的YUV类型。一个视频终端包含属于相关通道的USB端点IN或OUT,可支持一个或多个格式定义。为了选择一种特定的格式,因此主机需发送控制请求给相关的通道。

系统硬件设计

3.1 VGA接口

VGA是一种D型接口,可传输VGA,SVGA,XGA,SXGA等图像格式。VGA接口共有15针,分成3排,每排5个。VGA接口是显卡应用最为广泛的接口类型。

系统VGA模拟信号输入与A/D转换器相连,A/D转换器的RAIN,GAIN,BAIN分别与模拟接口的R,G,B相连。

3.2 A/D转换接口

由于A/D转换器的采样率较高,相应的输出数据速率也高。在系统最高要求下,像素点频率为108 MHz,相应的数据速率为324 Mbit/s(R,G,B 3个分量,每个分量8 bit)。同时,由于采集图像数据,要求较高的行同步时。如果某一行图像数据丢失一个或多个点数据,整个图像就会产生倾斜。因此需突发存储每行数据,保证数据不丢失。其突发长度为图像的水平分辨率。

该采集模块的A/D转换器采用AD9883A。该器件是专门针对采集模拟R,G,B信号,并将其数字化显示或为其他应用而设计的。该器件具有采样精度为8 bit的3路通道,最高采样率为140 MS/s,300 MB的模拟带宽,并且优化了计算机及工作站的图像接口,可采样分辨率为1280×1024。刷新率为75 Hz的视频信号。基于AD9883A的电路可为高清电视(HDTV)提供良好的计算机接口和高性能视频设备的前端扫描转换器。AD9883A内部结构如图2所示。

输入VGA图像信号后,先箝位以调整其直流偏移分量,使输入电平满足A/D转换模块要求。AD9883A内部具有3个高带宽、8 bit分辨率、110MS/s转换速率的A/D转换器,对箝位后的模拟视频信号进行采样、量化、编码,得到数字视频信号,通过寄存器调整采样相位,获得最佳转换效果。

采样时钟通过配置锁相环(PLL)生成,可使用行同步信(HSYNC)作为参考时钟,然后经分频,得到A/D转换器所需的采样时钟。AD9883A内部集成一个超低抖动锁相环,在所有工作模式下时钟抖动不到点时钟的5%。AD9883A时钟的稳定性对于系统产生清晰稳定的图像十分重要。由于AD9883A具有一个宽范围,可调的锁相环,能够产生12~140 MHz的像素点频率,因此AD9883A支持丰富的输入图像格式。

AD9883A的同步信号产生模块能识别多种同步信号输入模式,同时也可根据需要灵活设定同步信号的输出模式。通过I2C总线时序,方便实现器件初始化。

A/D转换模块能采集多种VGA图像格式,但不能自动检测图像格式,必须通过它提供的I2C接口进行设置,FPGA自动检测图像格式,并设置A/D转换模块。另外,不同格式的VGA图像中场同步信号的有效脉冲电平不统一,A/D转换模块可自动检测输入的场同步信号极性并存储到内部寄存器,通过读取该寄存器判断输入VGA信号场同步的极性。A/D转换模块输出的场同步信号实现输入场同步信号的反相。FP-GA内部的同步逻辑只支持一种有效电平的场同步信号,因此在采集前需读取A/D转换器内部寄存器来判断当前输入同步信号的极性,以确定是否需要设置A/D转换器对场同步信号进行反相处理。

输入的模拟视频信号经箝位处理、增益与偏置控制后,AD9883内部3个高精度高速A/D转换器在锁相环产生的采样时钟作用下,转换为显示所需的数字视频信号。图3为其数据输出的时序,在输出数据时钟DATACK的下降沿,采样及量化其对应的信号,量化后的数据在时钟上升沿输出:接口电路以DATACK的上升沿准确锁存图像数据,实现数字化图像的采集。考虑到像素时钟和数据的相位延迟等问题,可用HSYNC消除边沿定时的不确定性。要注意的是,AD9883A有一个数据输出通道,在输出数据有效之前必须清空通道,从而导致在输出每行有效数据之前将输出4组无效数据,可通过对时钟计数避免输出这些无效数据。

3.3 FPGA控制器设计

主控FPGA产生系统所需的控制信号,保证各个模块协涮工作。该系统设计采用EP1C12Q240C8型FPGA。其内部模块框图如图4所示。

FPGA内部由主控制、A/D转换接口、FIFO,以及USB等模块组成。主控制模块负责协调各模块之间的工作。A/D转换接口模块接收A/D转换模块输出的数据和同步信号并保证图像数据的行、场同步,FIFO模块采用pingpong的方式读取A/D转换传输的8×3路数字信号,然后USB输出接口模块输出高速数据。

3.4 输出显示设计

USB接口模块为应用程序和功能性设备提供可靠接口,USB体系可分为USB主机和USB设备两部分,其模块结构图如图5所示。

USB接口器件选用Cypress公司的EZ-USB FX2器件CY7C68013A。该器件内部集成USB 2.0收发器智能串行引擎SIE,增强型8051控制器,通用可编程接口(GPIF),8.5 KB的RAM和4 KB的FIFO存储器,FX2系列的独创性设计可满足USB2.0的总线带宽。

该系统以传输控制信息和视频数据为主,可将器件置于Slave FIFO模式,USB串行接口引擎(SIE)直接与Slave FIFO传输数据,Slave FIFO再与外部设备(FPGA)通信,从而实现PC机与FPGA的通信,并显示视频数据。

3.5 USB设备驱动开发

USB设备驱动程序嘲是连接USB外设、操作系统以及用户应用程序的桥梁,是USB设备连接到计算机系统的软件接口。EZ-USB FX2器件CY7C68013A的设备驱动程序有两种:一种用来在设备接入时从主机下载的固件存储RAM中,称为同件下载驱动程序(wdgtldr.sys);另一种是在设备重新列举后加载的通用设备驱动程序(ezu***.sys),应用软件通过该设备驱动程序与FX2通信。编写上位机程序的一个类USB Video Class,它对应于硬件CY7C68013A的一个同件,Video Class协议的目的是给USB接口的视频设备提供统一的数据交换规范,这样CY7C68013A接入PC后就无需ezu***.sys,而是使用PC自带的Video驱动将其识别为Video设备。

固件的程序代码既可通过外部E2PROM下载,也可通过主机下载,这里选用从主机下载。其中,USB Video Class协议是主机端通过向设备端获取描述符(Descriptor)来得到视频设备端的结构及其所支持的功能。而控制这些功能模块,配置数据源和数据流,则需通过Request(包括所有USB设备都需要支持的Standard Device Requests和Class与相关的Class Specific Requests)完成。

操作系统通过驱动程序实现对Video Class的支持。Video Class驱动的整体框架分为两部分:一部分是负责处理模块的初始化,处理USB总线上的Descriptor和Requests的交互,包括USB总线上的控制和查询包的接收、解释、分配和应答:另一部分是在初始化中启动的一个独立的内核线程。负责执行具体的控制指令,获取和传输图像数据。

表1给出了USB Video Class程序中Uncompressed Video Format Descriptor(未压缩的视频格式描述符)的相关定义和实例。这个描述符定义了一种特殊的视频流的特性,用于定义未缩视频的信息,包括所有的YUV类型。一个视频终端包含属于相关通道的USB端点IN或OUT,可支持一个或多个格式定义。为了选择一种特定的格式,因此主机需发送控制请求给相关的通道。

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报