系统硬件设计

3.1 图像处理系统的设计与实现

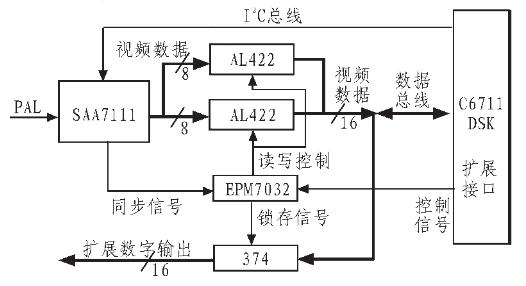

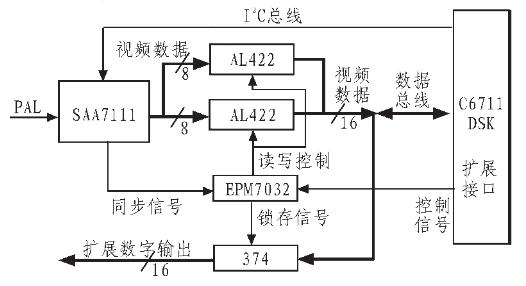

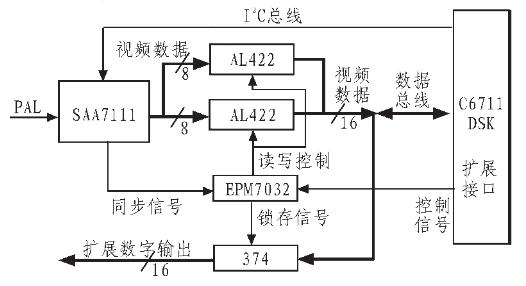

系统采用Philips公司提供的专用视频解码芯片SAA7111实现模拟视频信号的采集。SAA7111与C6711之间通过专用视频帧存储器AL422实现,外围接口逻辑由一片EPM7032实现,如图2所示。

图2:图像采集扩展结构。

3.2 I2C总线实现

SAA7111不支持即插即用功能,需要通过I2C总线对其进行初始化。由于C6711没有I2C接口模块,需要采用通用I/O接口和软件来模拟实现。C6711没有专门的通用I/O接口,需要通过配置多通道缓冲串行口(McBsp)使其成为通用I/O接口。C6711具有2个McBs接口,可将其中的一个配置成通用IO接口。C6711的时钟频率比I2C总线的频率要求高,在设计时需要注意I2C总线的时序要求,尤其是对数据保持时间的要求。

3.3 C6711与AL422接口实现

图像采集设计中需要考虑的主要问题之一是图像帧缓冲结构的设计。采用先进先出存储器(FIFO)只占用单页地址映射空间,可以节省大量地址空间。而且如果将帧存储体映射到地址空间的高段,会使其对DSP的影响降低到最小,因此系统采用了基于FIFO的图像帧缓冲结构。

AL422是专门用在视频领域的大容量视频帧存储器,设计中需要考虑的主要问题是接口逻辑的实现。虽然AL422的读写与WCK、RCK同步,但是与普通的同步FIFO不同的是其必须保证WCK、RCK至少1MHz的独立时钟,并且在进行不规律读写时只能由WEN或BEN进行控制。C6711采用100MHz的外部时钟,需要通过降频合成AL422的RCK。由于C6711输出的外部时钟频率为100MHz,而AL422B的最高RCK为50MHz,因此采用将C6711输出的外部时钟二分频作为AL422的RCK。AL422的REN、OEN可以采用DSK板上的DB_AREN、DB_OEN、DB_CE2信号通过组合逻辑实现。而RRSTN可采用DSK的一个通用I/O接口实现。DSK的外部时钟频率为IOOMHz,因此在设计时应该考虑逻辑器件本身的时延并采用同步设计方式。系统采用EPM7032实现上述FIFO接口逻辑,并将FIFO的输出数据与C6711DSK扩展接口的数据总线相连,将CE2存储空间分配给FIFO,从而最终实现了C6711与FIFO之间的接口。

3.4 F2812与C6711接口实现

由于TMS320C6711和TMS320F2812都支持McBsp接口并且相互兼容,所以系统采用McBsp接口实现两者之间的通讯。McBSP是多通道缓冲串行口的简称,能够同步发送和接收8/16/32位串行数据。接收和传送均采用独立的时钟和帧信号,其来源、频率、极性等均可由用户进行编程。McBSP包括数据流路径和控制路径,通过6根信号线连接到外部设备。数据信息通过传输引脚DX发送,接收引脚DR接收。时钟和帧同步控制信息由发送时钟、接收时钟、发送帧同步和接收帧同步引脚来产生。McBSP提供了双倍缓冲传送和三倍缓冲的接收。接收数据到达引脚DR后,移入接收移位寄存器RSR1,当整个字信息被接收之后,又被复制到接收缓冲寄存器RBR,最终复制到数据接收寄存器DRR,由CPU读取。而发送数据由CPU写入发送寄存器DXR,再复制到发送移位寄存器XSR。在帧同步信息发送后,发送器开始将XSR的内容移位到DX引脚。

F2812具有一个McBSP模块,而C6711自带了两个McBSP模块,二者之间完全兼容的。由于第一组McBSP的信号被配置成为通用I/O接口用于I2C总线的扩展,故只能使用C6711的第二组McBSP实现与F2812之间的通讯。在硬件上采用双机接收/发送端互连,即C6711的数据发送、时钟发送、帧发送同步信号管脚连接到F2812对应的接收管脚;反之亦然。

通过对相关寄存器的配置来实现数据的接收和发送操作,具体流程如下:

1)设置相关引脚为MeBSP引脚。

2)复位接收器、发送器及采样率发生器。

3)禁止数字回送、时钟停止、多通道模式。

4)接收和发送帧:单相,字长32位,每帧2个码字,使能帧同步忽略,无压缩扩展,1位数据延迟,右对齐高位填0,产生中断方式为检测到帧同步脉冲,帧同步脉冲高有效,时钟信号为上升沿触发。

5)发送时钟信号和帧同步信号来自内部采样率发生器,接收时钟信号和帧同步信号来自外部相应的接收引脚。时钟频率为37.5MHz,帧频率为1.25M,帧宽度为1个时钟脉冲宽度。采样率发生器时钟来源于内部CPU。

6)使能接收中断和发送中断,使能接收器、发送器及采样率发生器。

在相应的中断子程序中,通过读取和写入DXR1、DXR2、DRR1、DRR2寄存器实现F2812和C6711之间数据的读写。

系统硬件设计

3.1 图像处理系统的设计与实现

系统采用Philips公司提供的专用视频解码芯片SAA7111实现模拟视频信号的采集。SAA7111与C6711之间通过专用视频帧存储器AL422实现,外围接口逻辑由一片EPM7032实现,如图2所示。

图2:图像采集扩展结构。

3.2 I2C总线实现

SAA7111不支持即插即用功能,需要通过I2C总线对其进行初始化。由于C6711没有I2C接口模块,需要采用通用I/O接口和软件来模拟实现。C6711没有专门的通用I/O接口,需要通过配置多通道缓冲串行口(McBsp)使其成为通用I/O接口。C6711具有2个McBs接口,可将其中的一个配置成通用IO接口。C6711的时钟频率比I2C总线的频率要求高,在设计时需要注意I2C总线的时序要求,尤其是对数据保持时间的要求。

3.3 C6711与AL422接口实现

图像采集设计中需要考虑的主要问题之一是图像帧缓冲结构的设计。采用先进先出存储器(FIFO)只占用单页地址映射空间,可以节省大量地址空间。而且如果将帧存储体映射到地址空间的高段,会使其对DSP的影响降低到最小,因此系统采用了基于FIFO的图像帧缓冲结构。

AL422是专门用在视频领域的大容量视频帧存储器,设计中需要考虑的主要问题是接口逻辑的实现。虽然AL422的读写与WCK、RCK同步,但是与普通的同步FIFO不同的是其必须保证WCK、RCK至少1MHz的独立时钟,并且在进行不规律读写时只能由WEN或BEN进行控制。C6711采用100MHz的外部时钟,需要通过降频合成AL422的RCK。由于C6711输出的外部时钟频率为100MHz,而AL422B的最高RCK为50MHz,因此采用将C6711输出的外部时钟二分频作为AL422的RCK。AL422的REN、OEN可以采用DSK板上的DB_AREN、DB_OEN、DB_CE2信号通过组合逻辑实现。而RRSTN可采用DSK的一个通用I/O接口实现。DSK的外部时钟频率为IOOMHz,因此在设计时应该考虑逻辑器件本身的时延并采用同步设计方式。系统采用EPM7032实现上述FIFO接口逻辑,并将FIFO的输出数据与C6711DSK扩展接口的数据总线相连,将CE2存储空间分配给FIFO,从而最终实现了C6711与FIFO之间的接口。

3.4 F2812与C6711接口实现

由于TMS320C6711和TMS320F2812都支持McBsp接口并且相互兼容,所以系统采用McBsp接口实现两者之间的通讯。McBSP是多通道缓冲串行口的简称,能够同步发送和接收8/16/32位串行数据。接收和传送均采用独立的时钟和帧信号,其来源、频率、极性等均可由用户进行编程。McBSP包括数据流路径和控制路径,通过6根信号线连接到外部设备。数据信息通过传输引脚DX发送,接收引脚DR接收。时钟和帧同步控制信息由发送时钟、接收时钟、发送帧同步和接收帧同步引脚来产生。McBSP提供了双倍缓冲传送和三倍缓冲的接收。接收数据到达引脚DR后,移入接收移位寄存器RSR1,当整个字信息被接收之后,又被复制到接收缓冲寄存器RBR,最终复制到数据接收寄存器DRR,由CPU读取。而发送数据由CPU写入发送寄存器DXR,再复制到发送移位寄存器XSR。在帧同步信息发送后,发送器开始将XSR的内容移位到DX引脚。

F2812具有一个McBSP模块,而C6711自带了两个McBSP模块,二者之间完全兼容的。由于第一组McBSP的信号被配置成为通用I/O接口用于I2C总线的扩展,故只能使用C6711的第二组McBSP实现与F2812之间的通讯。在硬件上采用双机接收/发送端互连,即C6711的数据发送、时钟发送、帧发送同步信号管脚连接到F2812对应的接收管脚;反之亦然。

通过对相关寄存器的配置来实现数据的接收和发送操作,具体流程如下:

1)设置相关引脚为MeBSP引脚。

2)复位接收器、发送器及采样率发生器。

3)禁止数字回送、时钟停止、多通道模式。

4)接收和发送帧:单相,字长32位,每帧2个码字,使能帧同步忽略,无压缩扩展,1位数据延迟,右对齐高位填0,产生中断方式为检测到帧同步脉冲,帧同步脉冲高有效,时钟信号为上升沿触发。

5)发送时钟信号和帧同步信号来自内部采样率发生器,接收时钟信号和帧同步信号来自外部相应的接收引脚。时钟频率为37.5MHz,帧频率为1.25M,帧宽度为1个时钟脉冲宽度。采样率发生器时钟来源于内部CPU。

6)使能接收中断和发送中断,使能接收器、发送器及采样率发生器。

在相应的中断子程序中,通过读取和写入DXR1、DXR2、DRR1、DRR2寄存器实现F2812和C6711之间数据的读写。

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报