硬件设计

硬件设计主要包括TMS320C6678和两个88E1111的接口、88E1111和RJ45的接口、88E1111的硬件配置设计等几个部分。

TMS320C6678的网络模块结构如图3所示。片内集成了一个3口的以太交换机,负责将两个千兆网口的数据交换到主机,同时提供交换中断到主机,主机通过中断可以实时接收和发送数据。主机通过总线配置或者监控外部的物理层芯片,配置和监控数据通过MDIO接口连接到物理层芯片。

图3 TMS320C6678网络模块结构

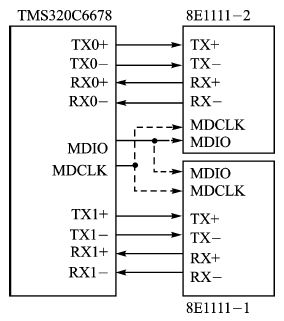

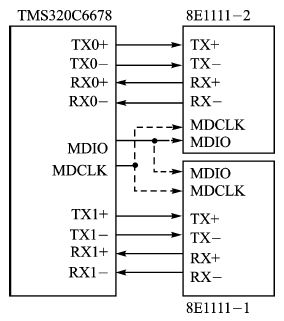

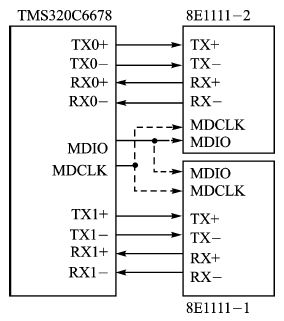

图4 TMS320C6678和88E1111的接口TMS320C6678和两片88E1111的接口电路如图4所示。TMS320C6678 采用SGMII(Serial Gigabit Media Independent Interface)接口,兼容10/100/1000M 工作方式。SGMII为串行数据收发方式,具有较少的引脚连接。从图4中可以看出,实际上只有两对收发的差分线,分别连接到对应的88E1111引脚上。读写时钟隐含在数据上传输,由硬件自动识别,无须软件参与。

图4 TMS320C6678和88E1111的接口

MDIO和MDCLK 为TMS320C6678内部MDIO 模块的数据和时钟,用于TMS320C6678和88E1111建立连接,TMS320C6678可以通过该接口配置88E1111,或者读取88E1111的信息。由于88E1111的MDIO模块接口电平为2.5V,而TMS320C6678的MDIO模块接口电平采用1.8V电压,所以两者之间需要增加电压转换芯片,本设计采用PCA9306实现电压转换,接口电路如图5所示。

图5 MDIO接口的电压转换电路

需要注意的是,由于存在两个88E111芯片,MDIO和MDCLK引脚直接连接到两个芯片上,MDIO可以最多控制32个物理层芯片,物理层芯片地址分别为1~32.88E1111的地址配置如图6所示。

图6 88E1111的硬件配置

表1为对应的配置信息,根据图6和表1,可以看出88E111的地址分别为4和8。

表1 配置引脚设置

硬件设计

硬件设计主要包括TMS320C6678和两个88E1111的接口、88E1111和RJ45的接口、88E1111的硬件配置设计等几个部分。

TMS320C6678的网络模块结构如图3所示。片内集成了一个3口的以太交换机,负责将两个千兆网口的数据交换到主机,同时提供交换中断到主机,主机通过中断可以实时接收和发送数据。主机通过总线配置或者监控外部的物理层芯片,配置和监控数据通过MDIO接口连接到物理层芯片。

图3 TMS320C6678网络模块结构

图4 TMS320C6678和88E1111的接口TMS320C6678和两片88E1111的接口电路如图4所示。TMS320C6678 采用SGMII(Serial Gigabit Media Independent Interface)接口,兼容10/100/1000M 工作方式。SGMII为串行数据收发方式,具有较少的引脚连接。从图4中可以看出,实际上只有两对收发的差分线,分别连接到对应的88E1111引脚上。读写时钟隐含在数据上传输,由硬件自动识别,无须软件参与。

图4 TMS320C6678和88E1111的接口

MDIO和MDCLK 为TMS320C6678内部MDIO 模块的数据和时钟,用于TMS320C6678和88E1111建立连接,TMS320C6678可以通过该接口配置88E1111,或者读取88E1111的信息。由于88E1111的MDIO模块接口电平为2.5V,而TMS320C6678的MDIO模块接口电平采用1.8V电压,所以两者之间需要增加电压转换芯片,本设计采用PCA9306实现电压转换,接口电路如图5所示。

图5 MDIO接口的电压转换电路

需要注意的是,由于存在两个88E111芯片,MDIO和MDCLK引脚直接连接到两个芯片上,MDIO可以最多控制32个物理层芯片,物理层芯片地址分别为1~32.88E1111的地址配置如图6所示。

图6 88E1111的硬件配置

表1为对应的配置信息,根据图6和表1,可以看出88E111的地址分别为4和8。

表1 配置引脚设置

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报