大家好,我是一哥,上章内容我们介绍什么是uvm?uvm的特点以及uvm为用户提供了哪些资源?

本章内容我们来看一看一个典型的uvm验证平台应该是什么样子的,来看一个典型的uvm测试平台的结构。

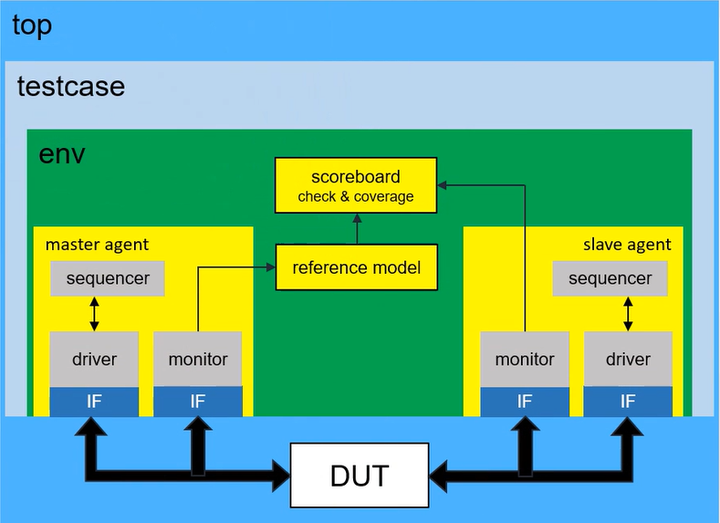

我们一个直观的印象,就是uvm验证平台,它是分层的结构。图中的每一个巨型框都代表着平台的一个构成元素。这些元素呢,我们称为平台组建,下面来简单的分析一下。

从最底层上来看,agent 中包含了driver,monitor和sequencer,其中driver ,monitor中也包含了与dut进行

通信的interface。

往上一层上来看,这层是env,其中包含了多个agent以及参考模型reference model和积分板scoreboard。

再往上一层是测试案例testcace,他包含了env。

最高层则是顶层top,它包含了测试的案例以及待测设计dut。

那么,在实际应用的过程中,将uvm的组件封装起来,可以将这些封装的组件呢作为一个整体进行重用,在进行芯片级或者是系统级验证的时候,往往会出现多个模块的验证。

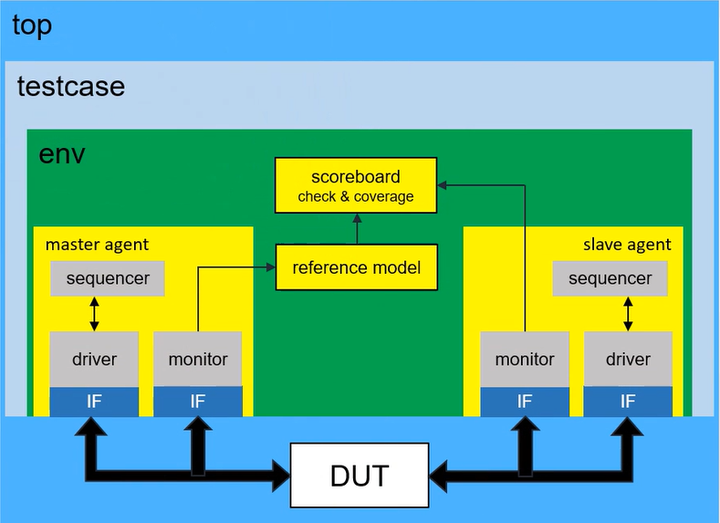

此时,测试平台的结构会发生变化,图中的测试平台实现了多个模块的测试,虽然说有点复杂,但是平台的结构与测试单个模块,在形式上是一样的,如果把dut看成是上一个图中的dut。那么平台的左半部分就于上图的测试平台完全一致。

只是slave agent变成了他的passitage模式,从图中可以看出,每增加一个测试模块,平台中就会增加一个与之相对应的agent,因为这些agent在测试单个模块的时候已经完成了,所以这里只需要将它们集成到一个env当中即可,这体现了uvm测试平台的可重用性。

本章内容就介绍到这里!!!

未完(待更).......

我们一个直观的印象,就是uvm验证平台,它是分层的结构。图中的每一个巨型框都代表着平台的一个构成元素。这些元素呢,我们称为平台组建,下面来简单的分析一下。

我们一个直观的印象,就是uvm验证平台,它是分层的结构。图中的每一个巨型框都代表着平台的一个构成元素。这些元素呢,我们称为平台组建,下面来简单的分析一下。 此时,测试平台的结构会发生变化,图中的测试平台实现了多个模块的测试,虽然说有点复杂,但是平台的结构与测试单个模块,在形式上是一样的,如果把dut看成是上一个图中的dut。那么平台的左半部分就于上图的测试平台完全一致。

此时,测试平台的结构会发生变化,图中的测试平台实现了多个模块的测试,虽然说有点复杂,但是平台的结构与测试单个模块,在形式上是一样的,如果把dut看成是上一个图中的dut。那么平台的左半部分就于上图的测试平台完全一致。