串行端接的优点在于:

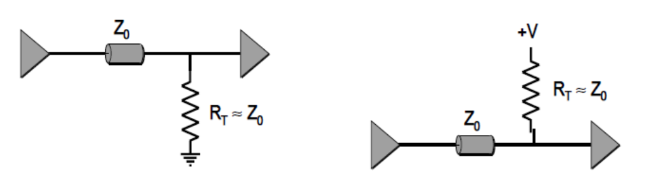

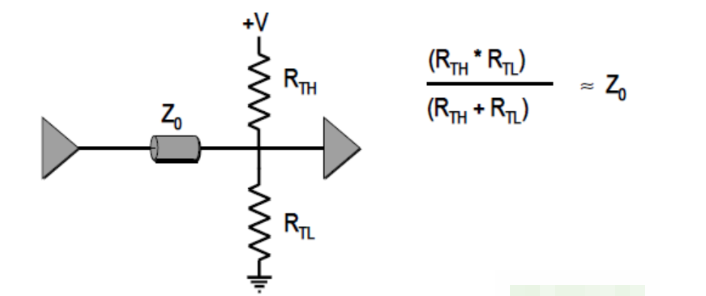

每条线只需要一个端接电阻,无需与电源相连接,消耗功率小。

串联电阻匹配终端的优势还在于可以减少板上器件的使用数量和连线密度。

串行端接的缺点在于:

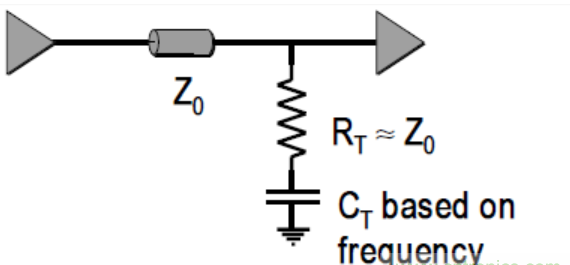

当信号逻辑转换时,源端会出现半波幅度的信号,这种半波幅度的信号沿传输线传播至负载端,又从负载端反射回源端,持续时间为2TD(TD为信号源端到终端的传输延迟),这意味着此时沿传输线不能加入其它的信号输入端。

串行端接的优点在于:

每条线只需要一个端接电阻,无需与电源相连接,消耗功率小。

串联电阻匹配终端的优势还在于可以减少板上器件的使用数量和连线密度。

串行端接的缺点在于:

当信号逻辑转换时,源端会出现半波幅度的信号,这种半波幅度的信号沿传输线传播至负载端,又从负载端反射回源端,持续时间为2TD(TD为信号源端到终端的传输延迟),这意味着此时沿传输线不能加入其它的信号输入端。

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报