时钟速率限制

为了计算最大SPI时钟速度,全双工“直接使用”式实施方案必须考虑数字隔离器的若干特性。最小脉冲宽度、最大数据速率和传播延迟都可能是限制因素。

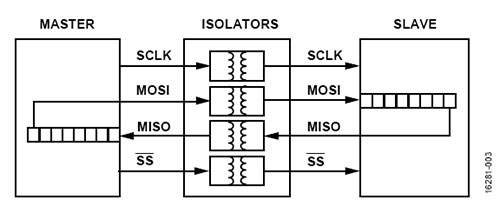

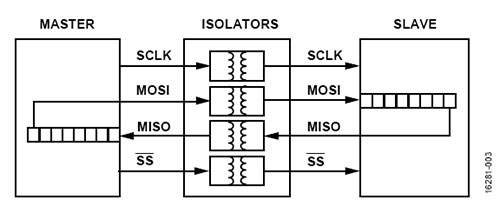

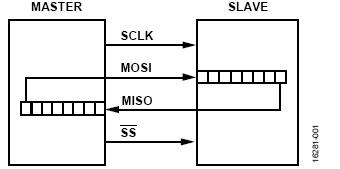

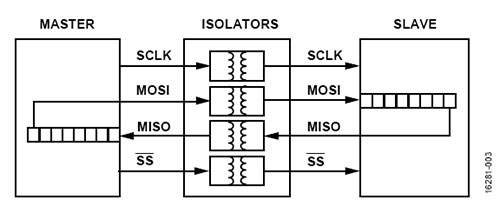

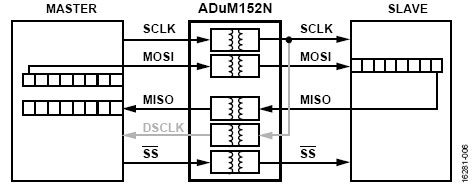

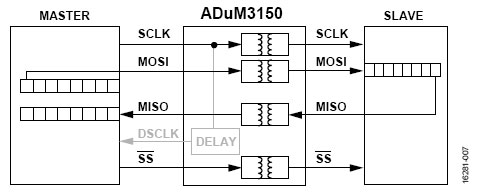

图3显示了利用通用3/1四通道标准数字隔离器作为“直接使用”式电气隔离解决方案的SPI总线隔离。SPI时钟信号每个周期改变状态两次,但通过数字隔离器的数字数据并非如此。标准数字隔离器必须具有支持时钟信号的最大数据速率特性。在此示例器件中,最大数据速率特性不是限制因素。

图3.标准数字隔离器SPI隔离

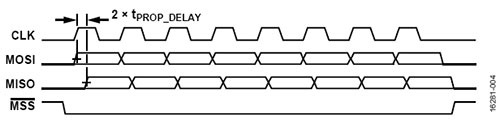

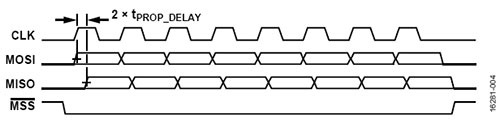

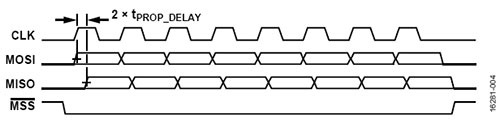

注意图4中传播延迟的影响。在这个例子中,数据在时钟上升沿发送,在下降沿接收。

图4.带隔离的标准SPI时序图

主器件同时开始时钟和主器件输出、从器件输入(MOSI)信号的传输。从器件的主器件输入、从器件输出(MISO)信号传输由时钟上升沿触发;由于时钟沿延迟,MISO信号也被延迟。MISO信号随后必须经过标准数据隔离器,再到达主器件。在这个例子中,从器件和主器件均在时钟下降沿读取数据。

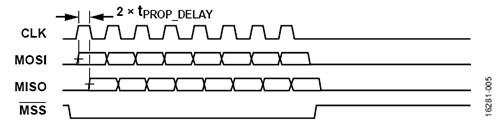

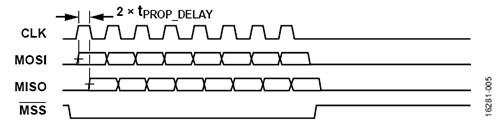

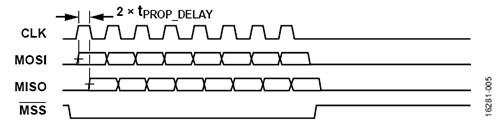

SPI通信取决于与MISO信号同步的时钟信号。图5显示了传播延迟的影响,数据速率一直增加到通信失败。由于传播延迟,时钟下降沿导致读取发生在MISO信号转换时,而非MISO信号建立时。此系统的数据速率过高,通信不可靠。

图5.主器件视角下的时序图

如图5所示,到从器件和返回到主器件的传播延迟必须发生在小于SPI时钟周期一半的时间内。在应用中,PCB走线延迟、建立时间和从器件响应时间可能会进一步降低最大时钟速率。为简单起见,本应用笔记忽略这些因素,因此“直接使用”式全双工实施方案具有如下关系:

SPI时钟半周期 ≥ 2 × tPROP_DELAY

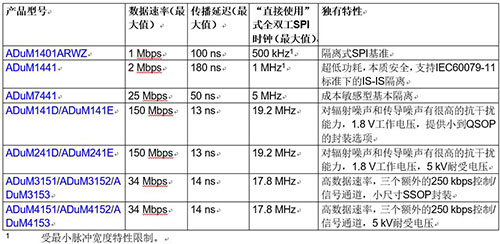

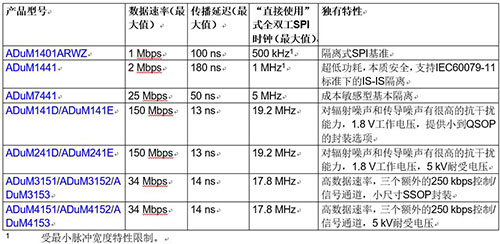

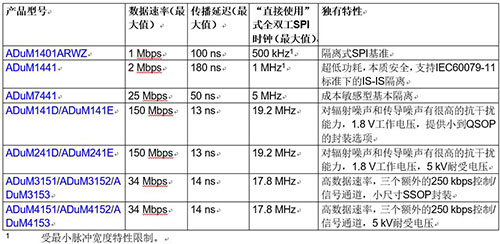

用数据手册中的最大传播延迟值计算最大数据速率。尽管系统在实验室中可以实现更高速度,但为了确保通信鲁棒,必须考虑温度、电源电压和器件的变化。表1提供了关于ADI公司各种数字隔离器的最大SPI数据速率的指南。

表1.“直接使用”式全双工数字隔离器最大SPI时钟速率

时钟速率限制

为了计算最大SPI时钟速度,全双工“直接使用”式实施方案必须考虑数字隔离器的若干特性。最小脉冲宽度、最大数据速率和传播延迟都可能是限制因素。

图3显示了利用通用3/1四通道标准数字隔离器作为“直接使用”式电气隔离解决方案的SPI总线隔离。SPI时钟信号每个周期改变状态两次,但通过数字隔离器的数字数据并非如此。标准数字隔离器必须具有支持时钟信号的最大数据速率特性。在此示例器件中,最大数据速率特性不是限制因素。

图3.标准数字隔离器SPI隔离

注意图4中传播延迟的影响。在这个例子中,数据在时钟上升沿发送,在下降沿接收。

图4.带隔离的标准SPI时序图

主器件同时开始时钟和主器件输出、从器件输入(MOSI)信号的传输。从器件的主器件输入、从器件输出(MISO)信号传输由时钟上升沿触发;由于时钟沿延迟,MISO信号也被延迟。MISO信号随后必须经过标准数据隔离器,再到达主器件。在这个例子中,从器件和主器件均在时钟下降沿读取数据。

SPI通信取决于与MISO信号同步的时钟信号。图5显示了传播延迟的影响,数据速率一直增加到通信失败。由于传播延迟,时钟下降沿导致读取发生在MISO信号转换时,而非MISO信号建立时。此系统的数据速率过高,通信不可靠。

图5.主器件视角下的时序图

如图5所示,到从器件和返回到主器件的传播延迟必须发生在小于SPI时钟周期一半的时间内。在应用中,PCB走线延迟、建立时间和从器件响应时间可能会进一步降低最大时钟速率。为简单起见,本应用笔记忽略这些因素,因此“直接使用”式全双工实施方案具有如下关系:

SPI时钟半周期 ≥ 2 × tPROP_DELAY

用数据手册中的最大传播延迟值计算最大数据速率。尽管系统在实验室中可以实现更高速度,但为了确保通信鲁棒,必须考虑温度、电源电压和器件的变化。表1提供了关于ADI公司各种数字隔离器的最大SPI数据速率的指南。

表1.“直接使用”式全双工数字隔离器最大SPI时钟速率

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报