理想

电容只存在于教科书中,现实世界的每个

电容器都会因其实体结构而产生额外的复杂性。由介电层(dielectriclayer)隔开的两个极板(plate)与导线或金属箔(metalfoil)串联,即可实现实际的连接;这两种金属导体会导入等效串联

电感(ESL)以及等效串联

电阻(ESR)。

总而言之,实体电容就是一种串联谐振

电路(series tank circuit),具有串联谐振频率以及受串联电阻影响的串联谐振因子「Q」。

电容器并不仅限于其字面意思,在低于其串联谐振的频率下,电容会对电激励(electrical excita

tion)表现出电容性阻抗;而在高于其串联谐振的频率下,它对电激励表现出电感性阻抗。

关于宽带轨(broadband rail)

电压旁路,一个传统的观点认为应该使用不同容量的电容并联组合。常见的并联组合阵容包括:一个大容量的铝或钽电解电容C1;一个大容量的陶瓷电容C2;一个小容量的陶瓷电容C3;

电路板的布线电容(artwork capacitance),称之为C4;以及天知道从哪里来的电容,如线束电容(harness capacitance)和/或

半导体组件电容,统称为C5。

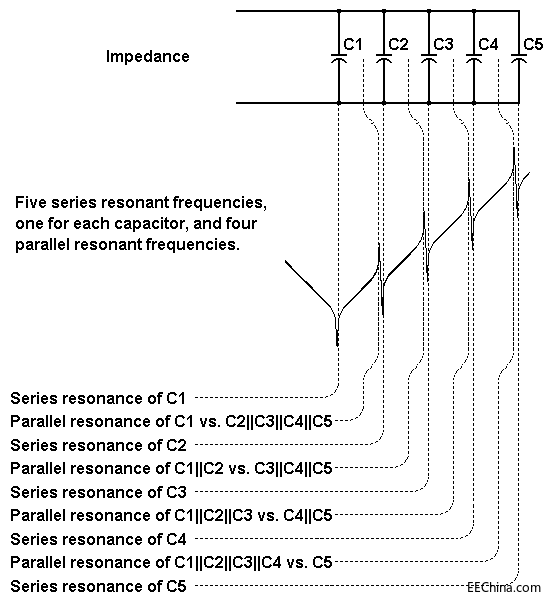

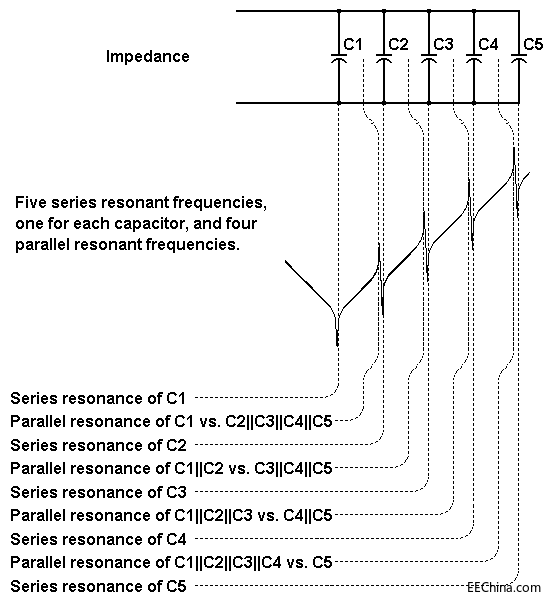

请记住,这五种电容每一个都不是单独的电容器,而是一个串联组合,包括电容器、电感器和电阻器。总之,它们由串联的RLC电路构成,将在串联谐振频率(SRF)处表现出串联谐振,其中SRF=1/(2 × π ×√ (L × C))。对于如上所述并联连接的五个电容的组合,将会有五个串联谐振频率,并且还会有四个并联谐振频率,如图1所示。

图1:5个并联电容的9个谐振频率。

四个较小的电容C2~C5在4个频率处进入并联谐振状态,这四个频率略低于它们各自的串联谐振频率。然而,C1并没有任何并联谐振,因为该电容没有任何感应可以产生并联谐振效应。

使用S

PICE软件和一些说明数字,我们可以深入研究这个问题,如图2所示。

2.jpg

2.jpg

图2:SPICE中5个电容的并联旁路。

对于这5个电容,将有5个串联自谐振频率,即SRF1、SRF2、SRF3、SRF4和SRF5,其中每一个电容都在其自身的SRF处阻抗最小。但是,不可避免地,在频率PRF2、PRF3、PRF4和PRF5处会产生4个总阻抗的并联谐振峰值。

PRF2源于C2~C5组合的容抗(capacitive impedance)与C1感抗(inductive impedance)之间的并联关系。类似地,PRF3来自C3~C5的组合容抗与C1~C2的组合感抗之间的并联关系,而PRF4来自C4~C5对C1~C3的并联关系,最后,PRF5来自C5对C1~C4的并联关系。

5个阻抗零点和4个阻抗峰值都受到电阻值的影响,图3提供了一个范例。请注意,并联谐振频率本身不能完全消除,将永远存在,你必须考虑到这一点。

图3:ESR的阻抗曲线变化。

备注:这个议题首先是在一个项目中引起我的注意,其中一个闸控数组的频率频率为16MHz,结果一些并联轨旁路电容的并联谐振频率也是16MHz。

2.jpg

2.jpg