[color=#333333 !important]

EMC范围很广,由于篇幅很大,这里主要先介绍下电容电感对EMC的影响。

[color=#333333 !important]

电容:

[color=#333333 !important]

电容的基本结构和高频等效电路如下图:

[color=#333333 !important]

[color=#333333 !important]

电容的质量(Q)取决于ESR

[color=#333333 !important]

ESL主要取决于电容的封装结构(插件》贴片)

[color=#333333 !important]

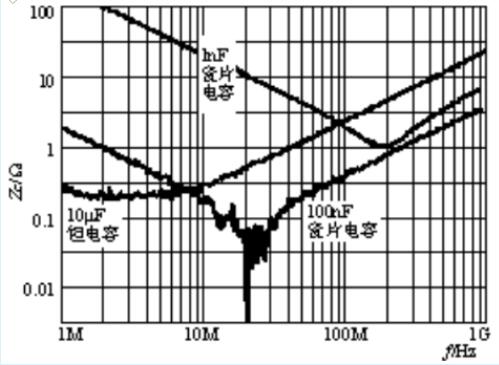

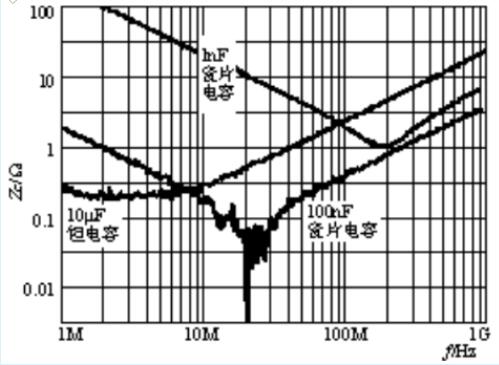

电容的阻抗(Zc)频谱特性(如图):

[color=#333333 !important]

[color=#333333 !important]

谐振频率f0=1/2π√LC

[color=#333333 !important]

当工作频率在f0时, Zc=ESR

[color=#333333 !important]

当工作频率小于f0时

[color=#333333 !important]

Zc随频率的上升而减小

[color=#333333 !important]

当工作频率大于f0时

[color=#333333 !important]

Zc随频率的上升而增大

[color=#333333 !important]

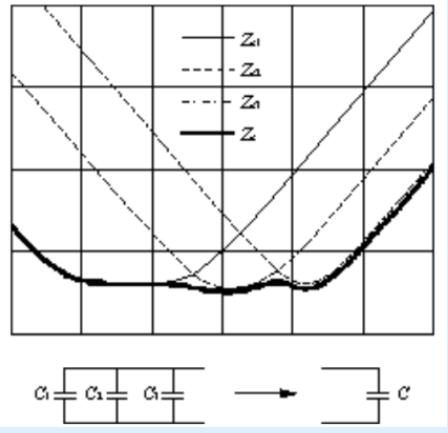

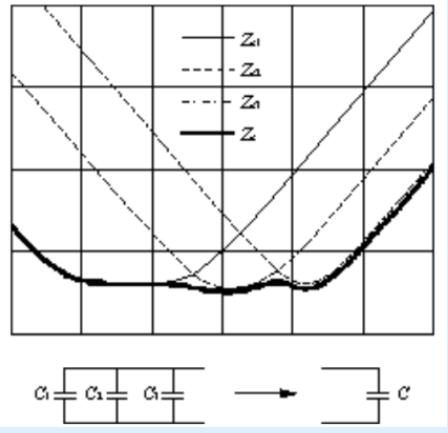

所以当多个电容并联起来的时候,可以改善电容的高频阻抗特性,如下图

[color=#333333 !important]

[color=#333333 !important]

所以电容是并的越多,高频特性越好。

[color=#333333 !important]

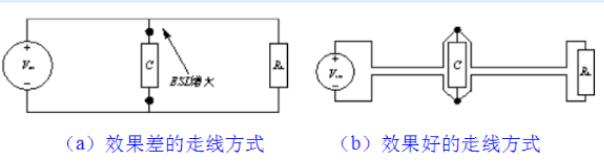

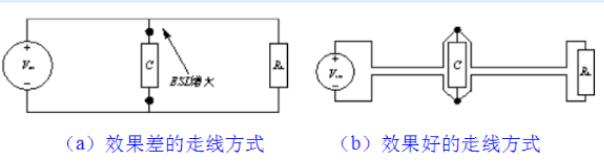

如图,PCB走线时应尽量减短引线长度,从而降低滤波电容的ESL,且电容两极之间的走线应尽量靠近。

[color=#333333 !important]

[color=#333333 !important]

电感:

[color=#333333 !important]

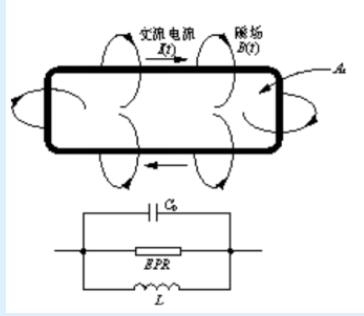

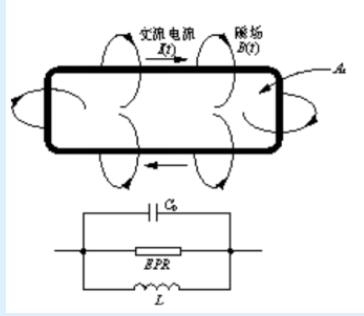

电感的基本结构和高频等效电路如下图

[color=#333333 !important]

EPR取决于磁性材料和匝数

[color=#333333 !important]

Cp一般大于1pF

[color=#333333 !important]

[color=#333333 !important]

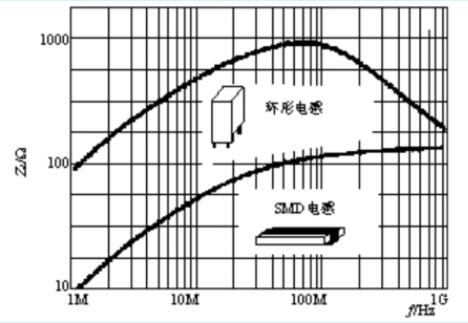

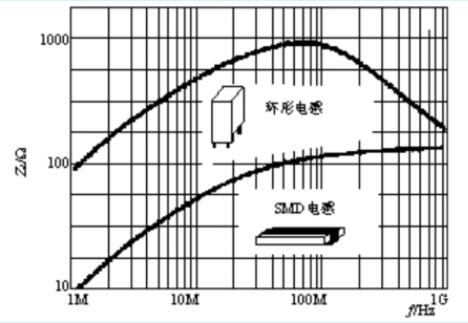

电感的阻抗(Zc)频谱特性(如图):

[color=#333333 !important]

[color=#333333 !important]

谐振频率f0=1/2π√LC

[color=#333333 !important]

当工作频率在f0时, Zc=EPR

[color=#333333 !important]

当工作频率小于f0时

[color=#333333 !important]

Zc随频率的上升而增大

[color=#333333 !important]

当工作频率大于f0时

[color=#333333 !important]

Zc随频率的上升而减小

[color=#333333 !important]

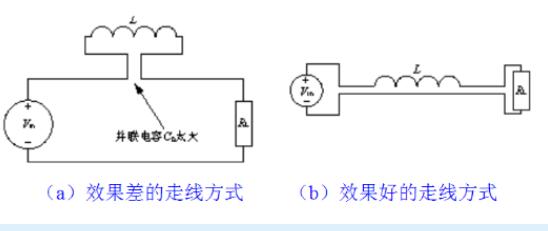

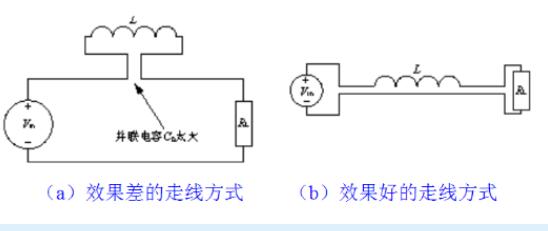

如图,PCB走线时电感的两个引脚应尽量远离,从而降低电感的Cp。

[color=#333333 !important]

[color=#333333 !important]

附:

[color=#333333 !important]

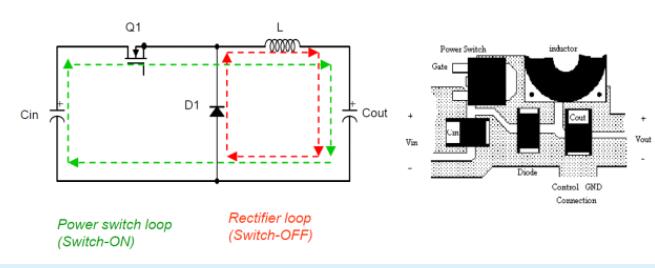

信号环路既是产生辐射的源头,也有可能是***扰的对象。因此尽量减小信号环路的大小是对一个layout工程师最基本的要求。

[color=#333333 !important]

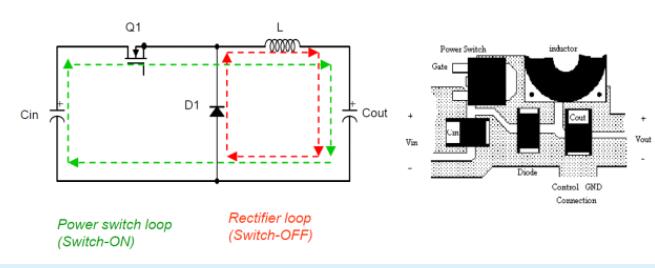

如下图是一个降压(BUCK)电路的工作电流环路分析以及layout的要求。

[color=#333333 !important]

[color=#333333 !important]

信号环路的控制:

[color=#333333 !important]

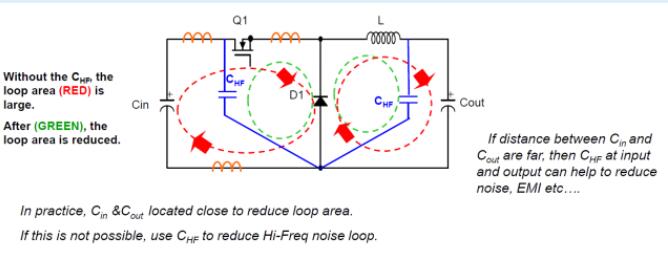

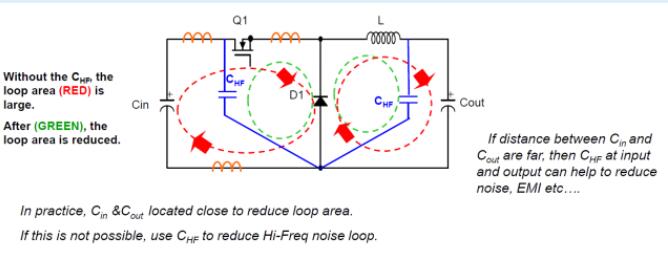

如果在实际PCB设计中Cin和Cout只能距离较远,可以通过增加高频滤波电容来减小BUCK电路的工作电流环路。

[color=#333333 !important]

[color=#333333 !important]

[color=#333333 !important]

[color=#333333 !important]

EMC范围很广,由于篇幅很大,这里主要先介绍下电容电感对EMC的影响。

[color=#333333 !important]

电容:

[color=#333333 !important]

电容的基本结构和高频等效电路如下图:

[color=#333333 !important]

[color=#333333 !important]

电容的质量(Q)取决于ESR

[color=#333333 !important]

ESL主要取决于电容的封装结构(插件》贴片)

[color=#333333 !important]

电容的阻抗(Zc)频谱特性(如图):

[color=#333333 !important]

[color=#333333 !important]

谐振频率f0=1/2π√LC

[color=#333333 !important]

当工作频率在f0时, Zc=ESR

[color=#333333 !important]

当工作频率小于f0时

[color=#333333 !important]

Zc随频率的上升而减小

[color=#333333 !important]

当工作频率大于f0时

[color=#333333 !important]

Zc随频率的上升而增大

[color=#333333 !important]

所以当多个电容并联起来的时候,可以改善电容的高频阻抗特性,如下图

[color=#333333 !important]

[color=#333333 !important]

所以电容是并的越多,高频特性越好。

[color=#333333 !important]

如图,PCB走线时应尽量减短引线长度,从而降低滤波电容的ESL,且电容两极之间的走线应尽量靠近。

[color=#333333 !important]

[color=#333333 !important]

电感:

[color=#333333 !important]

电感的基本结构和高频等效电路如下图

[color=#333333 !important]

EPR取决于磁性材料和匝数

[color=#333333 !important]

Cp一般大于1pF

[color=#333333 !important]

[color=#333333 !important]

电感的阻抗(Zc)频谱特性(如图):

[color=#333333 !important]

[color=#333333 !important]

谐振频率f0=1/2π√LC

[color=#333333 !important]

当工作频率在f0时, Zc=EPR

[color=#333333 !important]

当工作频率小于f0时

[color=#333333 !important]

Zc随频率的上升而增大

[color=#333333 !important]

当工作频率大于f0时

[color=#333333 !important]

Zc随频率的上升而减小

[color=#333333 !important]

如图,PCB走线时电感的两个引脚应尽量远离,从而降低电感的Cp。

[color=#333333 !important]

[color=#333333 !important]

附:

[color=#333333 !important]

信号环路既是产生辐射的源头,也有可能是***扰的对象。因此尽量减小信号环路的大小是对一个layout工程师最基本的要求。

[color=#333333 !important]

如下图是一个降压(BUCK)电路的工作电流环路分析以及layout的要求。

[color=#333333 !important]

[color=#333333 !important]

信号环路的控制:

[color=#333333 !important]

如果在实际PCB设计中Cin和Cout只能距离较远,可以通过增加高频滤波电容来减小BUCK电路的工作电流环路。

[color=#333333 !important]

[color=#333333 !important]

[color=#333333 !important]

举报

举报

举报

举报