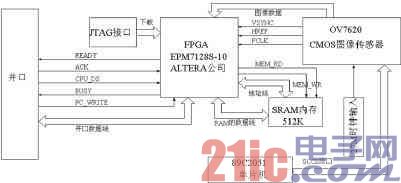

USB、串口、并口是PC机和外设进行通讯的常用接口,但对于数据量大的图像来说,若利用串行RS-232协议进行数据采集,速度不能达到图像数据采集所需的要求;而用USB进行数据采集,虽能满足所需速度,但要求外设必须支持USB协议,而USB协议与常用工程软件的接口还不普及,给使用带来困难。有些用户为了利用标准并行口(SPP)进行数据采集,但SPP协议的150kb/s传输率对于图像数据采集,同样显得太低。因此,为了采集数据量大的图像数据,本文采用了具有较高传输速率的增强型并行口协议(EPP)和

FPGA,实现对OV7620CMOS图像传感器进行高速数据采集,它最高速率可以达到2Mb/s。

举报

举报