3 结束语

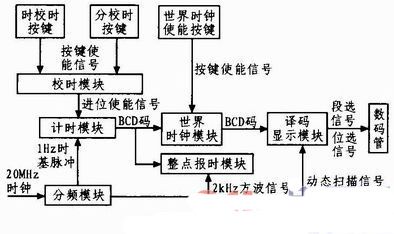

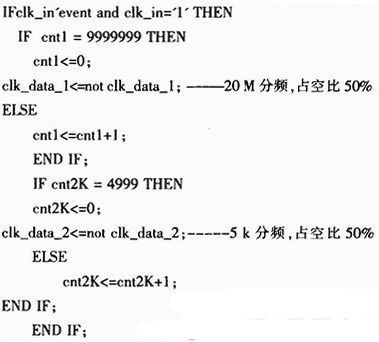

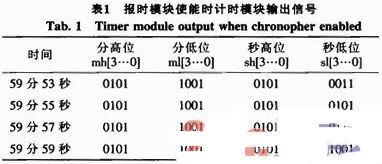

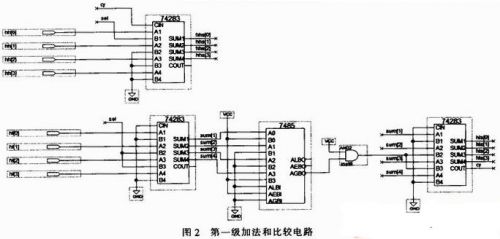

在QuartusⅡ开发环境中完成上述各模块的原理图设计和程序编写,并对设计好的电路进行编译、仿真,得到的仿真波形符合设计要求。根据所采用的硬件平台,在顶层电路中进行管脚分配、再编译。然后将编译好的目标文件下载到FPGA开发板中进行验证和调试。测试结果,数码管能够正确显示计时时间,能够通过按键调整时间,整点报时和世界时钟均能够正常工作,实验结果符合设计要求。

3 结束语

在QuartusⅡ开发环境中完成上述各模块的原理图设计和程序编写,并对设计好的电路进行编译、仿真,得到的仿真波形符合设计要求。根据所采用的硬件平台,在顶层电路中进行管脚分配、再编译。然后将编译好的目标文件下载到FPGA开发板中进行验证和调试。测试结果,数码管能够正确显示计时时间,能够通过按键调整时间,整点报时和世界时钟均能够正常工作,实验结果符合设计要求。

举报

举报

举报

举报

举报

举报

举报

举报