五、系统测试和结束语

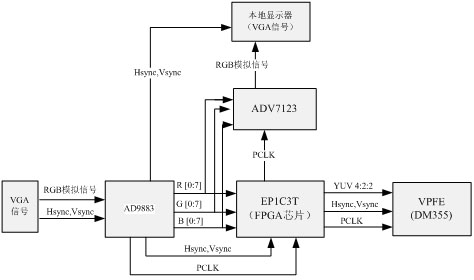

本系统对VGA信号采集成功后,利用MPEG4算法进行编码,并利用开源的JRTP库实现网络传输功能,客户端可实时观看和存储接收到的码流。在进行VGA信号采集编码的同时,可利用ADV7123芯片将VGA信号还原,在本地的显示器进行输出。经过实验测试,本系统具有较好的实时性,解码后的图像主观质量也很好。

本文提出的基于TMS320DM355处理器,采用AD9883和ADV7123转换芯片,结合FPGA技术的VGA信号采集方案,能够对XGA信号进行实时采集。该系统可广泛应用于雷达、天气预报、航空航天、通信等领域的图像数据实时记录。

【参考文献】

[1] Analog Devices.AD9883A/AD9883A Data sheet[EB/OL].2007. http://www.analog.com/static /imported- files/data_sheets/ AD9883A.pdf.

[2] 胡建民,郭太良,林志贤。 AD9883 在平板显示视频接口中的应用[J]。现代电子技术, 2007(2):25-27.

[3] Texas Instruments Incorporated. TMS320DM35x digital media system-on-chip video processing front end (VPFE) RG spruf71a[EB/OL]。[2009-08-10]。 http://focus.ti.com/lit/ug /spruf71a/spruf71a.pdf 。

[4] 朱文伟,许忠仁,基于FPGA 的V GA 图像控制器的设计与实现[J ] 。 贵州大学学报:自然科学版,2009 ,30 (2) :109- 111.

[5] SCHIMEK Michael H,DIRKS Bill,VERKUIL Hans,et al. Video for Linux Two API specification [EB/OL]。 [2009-10-20].http://www.soezblog.com/plate/web/bookmarkmsg.jsp?UI =cherng64&CI =368&p =1&BI=199102.

五、系统测试和结束语

本系统对VGA信号采集成功后,利用MPEG4算法进行编码,并利用开源的JRTP库实现网络传输功能,客户端可实时观看和存储接收到的码流。在进行VGA信号采集编码的同时,可利用ADV7123芯片将VGA信号还原,在本地的显示器进行输出。经过实验测试,本系统具有较好的实时性,解码后的图像主观质量也很好。

本文提出的基于TMS320DM355处理器,采用AD9883和ADV7123转换芯片,结合FPGA技术的VGA信号采集方案,能够对XGA信号进行实时采集。该系统可广泛应用于雷达、天气预报、航空航天、通信等领域的图像数据实时记录。

【参考文献】

[1] Analog Devices.AD9883A/AD9883A Data sheet[EB/OL].2007. http://www.analog.com/static /imported- files/data_sheets/ AD9883A.pdf.

[2] 胡建民,郭太良,林志贤。 AD9883 在平板显示视频接口中的应用[J]。现代电子技术, 2007(2):25-27.

[3] Texas Instruments Incorporated. TMS320DM35x digital media system-on-chip video processing front end (VPFE) RG spruf71a[EB/OL]。[2009-08-10]。 http://focus.ti.com/lit/ug /spruf71a/spruf71a.pdf 。

[4] 朱文伟,许忠仁,基于FPGA 的V GA 图像控制器的设计与实现[J ] 。 贵州大学学报:自然科学版,2009 ,30 (2) :109- 111.

[5] SCHIMEK Michael H,DIRKS Bill,VERKUIL Hans,et al. Video for Linux Two API specification [EB/OL]。 [2009-10-20].http://www.soezblog.com/plate/web/bookmarkmsg.jsp?UI =cherng64&CI =368&p =1&BI=199102.

举报

举报

举报

举报

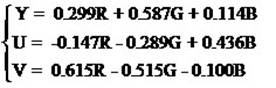

(式 1)

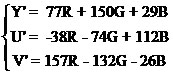

(式 1) (式2)

(式2)

举报

举报

举报

举报