无线蜂窝电话系统正从窄带的2G全球移动通信系统(GSM)和IS-95系统向基于宽带码分多址(W-CDMA)的3G和3.5G系统转移。随着这些标准的进步,无线基站OEM必须转换到更新、更好、更为强大及更有成本效益的各种技术,以满足这些系统对越来越高数据率的需求。

在不远的将来,第三代合作伙伴关系项目长期演进(3GPP LTE)规范将需要复杂的信号处理技术,如多点多输出(MIMO)及正交频分复用(OFDMA)和多载波码分多址(MC-CDMA)这样的新型无线电技术。随着这些技术应用的日益临近,移动和无线服务提供商及运营商希望无线基站OEM确保他们在现场安装的基站能够支持LTE规范。

运营商坚持避免出现“剥离更换”(rip and replace)的情况。这意味着OEM要用多协议设计在“将来试验”它们的基站。

多协议基站被定义为能够支持W-CDMA到LTE标准的基站。这种规格的基站家族实际上将需要从3GPP版本向更新的标准转移的能力,这种转移利用的是同一家族的基站,绝大多数系统不需要成本高昂的重新设计。

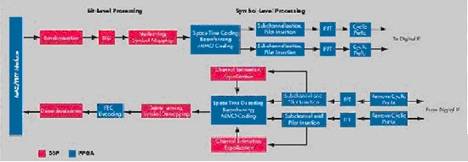

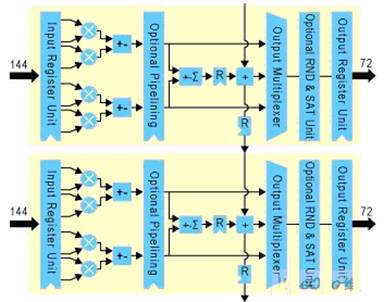

基于混合FPGA/数字信号处理的平台提供一种顺应这些不断变化的无线标准的有效设计方法。在FPGA和数字信号处理器之间的智能分区要求必须基于系统的吞吐量要求和产品成功所需要的长期成本考虑。随着标准的稳定,最初针对基站设计灵活性的要求应该逐渐居于次要地位,与此同时,成本成为一个主要的成功因素。

选择FPGA,就具备了一条向低成本的结构化ASIC技术转移的无风险的路径,从而大幅度降低成本。例如,Altera公司的HardCopy II技术提供一种无缝无风险的从Stratix III FPGA向成本大幅度降低的HardCopy II结构化ASIC转移的路径,与此同时,也提高了系统的性能并降低了功耗。

不断进化的设计

全球的无线运营商目前正使用高速下行链路分组接入(HSDPA),从而使通用移动通信系统(UMTS)系统的成功部署成为可能。UMTS向HSDPA的升级类似于增强数据率GSM演进(EDGE),它被证明是向GSM网络的一个有效升级。

HSDPA锁定的是移动多媒体应用,并能够实现缩短的延迟,在从基站到移动终端的下行链路上,峰值数据率高达14Mbps。通过增加一个新的高速下行链路,并与依赖于传输参数快速自适应的三个基本技术共享,就有可能做到这一点。那三个基本技术分别是:自适应调制和编码(AMC)、快速混合自动重复请求(ARQ)和快速调度技术。

高速上行分组接入(HSUPA)不久将追随HSDPA而步入实用,这两种技术的组合被称为高速分组接入(HSPA)。HSPA有望在21世纪头十年剩余的时间内成为占优势的移动数据传输技术。为了利用运营商在HSPA中的投资,标准组织正调查一系列增强标准,以创造被称为HSPA+的“HSPA演变”标准。

HSPA演变标准是W-CDMA标准的合乎逻辑的发展,为向全新的3GPP LTE无线电平台的发展提供了一种有效的转换。LTE在下行链路上采用OFDM,目标是在2009年左右开始部署。

LTE利用最佳种类的无线电技术,以实现超越实际CDMA方法的性能水平。LTE系统将与2G和3G系统共存,类似于3G与2G系统在一体化网络中的共存。同时,OFDM通信系统的设计持续取得更大的进展。OFDM是一种多载波调制方案,它把数据编码到一个无线电频率(RF)信号上。

与传统的单载波调制方案不同,像幅度或频率调制(AM/FM)利用一个无线电频率一次仅仅发送一个信号。OFDM取而代之的是在专门计算的正交载波频率上并发发送多个高速信号,结果,在噪声和其它干扰期间,带宽的使用效率更高,通信更为鲁棒。

在下行链路上用于LTE的OFDMA非常适合于在高频谱带宽内实现高峰值数据率。W-CDMA无线电技术的效率与在5MHz的带宽内传输具有大约10Mbps的峰值数据率的OFDM系统的效率大致相同。

然而,以较宽的无线电信道实现100Mbps范围的峰值数据率会导致终端高度复杂并且以现有的技术是不切实际的。正是在这里OFDM提供了一种实际的实现优势。

在上行链路,纯OFDMA方法导致高信号峰值对平均比(PAR),从而折衷电源效率和最终的电池寿命。因此,LTE利用一种称为单载波频分多址(SC-FDMA)的方法,它与OFDMA有一定的相似性,但是,比其它技术如IEEE 802.16e所使用的OFDMA方法有2到6dB PAR的优势。

无线蜂窝电话系统正从窄带的2G全球移动通信系统(GSM)和IS-95系统向基于宽带码分多址(W-CDMA)的3G和3.5G系统转移。随着这些标准的进步,无线基站OEM必须转换到更新、更好、更为强大及更有成本效益的各种技术,以满足这些系统对越来越高数据率的需求。

在不远的将来,第三代合作伙伴关系项目长期演进(3GPP LTE)规范将需要复杂的信号处理技术,如多点多输出(MIMO)及正交频分复用(OFDMA)和多载波码分多址(MC-CDMA)这样的新型无线电技术。随着这些技术应用的日益临近,移动和无线服务提供商及运营商希望无线基站OEM确保他们在现场安装的基站能够支持LTE规范。

运营商坚持避免出现“剥离更换”(rip and replace)的情况。这意味着OEM要用多协议设计在“将来试验”它们的基站。

多协议基站被定义为能够支持W-CDMA到LTE标准的基站。这种规格的基站家族实际上将需要从3GPP版本向更新的标准转移的能力,这种转移利用的是同一家族的基站,绝大多数系统不需要成本高昂的重新设计。

基于混合FPGA/数字信号处理的平台提供一种顺应这些不断变化的无线标准的有效设计方法。在FPGA和数字信号处理器之间的智能分区要求必须基于系统的吞吐量要求和产品成功所需要的长期成本考虑。随着标准的稳定,最初针对基站设计灵活性的要求应该逐渐居于次要地位,与此同时,成本成为一个主要的成功因素。

选择FPGA,就具备了一条向低成本的结构化ASIC技术转移的无风险的路径,从而大幅度降低成本。例如,Altera公司的HardCopy II技术提供一种无缝无风险的从Stratix III FPGA向成本大幅度降低的HardCopy II结构化ASIC转移的路径,与此同时,也提高了系统的性能并降低了功耗。

不断进化的设计

全球的无线运营商目前正使用高速下行链路分组接入(HSDPA),从而使通用移动通信系统(UMTS)系统的成功部署成为可能。UMTS向HSDPA的升级类似于增强数据率GSM演进(EDGE),它被证明是向GSM网络的一个有效升级。

HSDPA锁定的是移动多媒体应用,并能够实现缩短的延迟,在从基站到移动终端的下行链路上,峰值数据率高达14Mbps。通过增加一个新的高速下行链路,并与依赖于传输参数快速自适应的三个基本技术共享,就有可能做到这一点。那三个基本技术分别是:自适应调制和编码(AMC)、快速混合自动重复请求(ARQ)和快速调度技术。

高速上行分组接入(HSUPA)不久将追随HSDPA而步入实用,这两种技术的组合被称为高速分组接入(HSPA)。HSPA有望在21世纪头十年剩余的时间内成为占优势的移动数据传输技术。为了利用运营商在HSPA中的投资,标准组织正调查一系列增强标准,以创造被称为HSPA+的“HSPA演变”标准。

HSPA演变标准是W-CDMA标准的合乎逻辑的发展,为向全新的3GPP LTE无线电平台的发展提供了一种有效的转换。LTE在下行链路上采用OFDM,目标是在2009年左右开始部署。

LTE利用最佳种类的无线电技术,以实现超越实际CDMA方法的性能水平。LTE系统将与2G和3G系统共存,类似于3G与2G系统在一体化网络中的共存。同时,OFDM通信系统的设计持续取得更大的进展。OFDM是一种多载波调制方案,它把数据编码到一个无线电频率(RF)信号上。

与传统的单载波调制方案不同,像幅度或频率调制(AM/FM)利用一个无线电频率一次仅仅发送一个信号。OFDM取而代之的是在专门计算的正交载波频率上并发发送多个高速信号,结果,在噪声和其它干扰期间,带宽的使用效率更高,通信更为鲁棒。

在下行链路上用于LTE的OFDMA非常适合于在高频谱带宽内实现高峰值数据率。W-CDMA无线电技术的效率与在5MHz的带宽内传输具有大约10Mbps的峰值数据率的OFDM系统的效率大致相同。

然而,以较宽的无线电信道实现100Mbps范围的峰值数据率会导致终端高度复杂并且以现有的技术是不切实际的。正是在这里OFDM提供了一种实际的实现优势。

在上行链路,纯OFDMA方法导致高信号峰值对平均比(PAR),从而折衷电源效率和最终的电池寿命。因此,LTE利用一种称为单载波频分多址(SC-FDMA)的方法,它与OFDMA有一定的相似性,但是,比其它技术如IEEE 802.16e所使用的OFDMA方法有2到6dB PAR的优势。

举报

举报

举报

举报

举报

举报

举报

举报