4 系统验证与设计总结

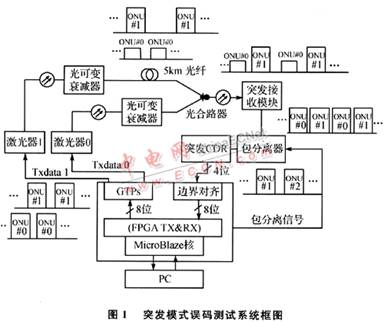

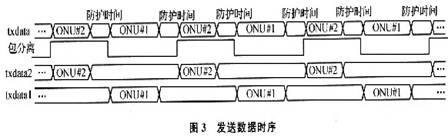

为了验证系统的性能,分别用该仪器做了自环测试和对1.25 GHz GPON系统突发式光接收模块的误码测试。在自环测试中,发送的数据不通过光路直接送到BMCDR的接收端。测试结果表明,在电信号信道中误码测试系统自身不会误码。在对1.25 GHz GPON系统突发式光接收模块测试过程中,采用两个步骤的测试。步骤1中,按图1连接误码测试系统,两路数据包信号0UN#1和0UN#2都不经过可变光衰减器的衰减,经光合路器合路后的光信号中所有包信号幅值一致,用以验证误码测试系统光路中是否产生误码,实验结果同样验证了误码测试系统自身不会产生误码。步骤2中,对一路数据包信号进行不同幅度的衰减,使光合路器输出的光信号存在幅值的跳变,并在两路数据包信号存在不同幅值跳变的情况下,分别测试突发式光接收模块的误码性能。试验中使用的被测突发式光接收模块强包弱包幅度相差20 dB,保护时间为32位,速率为1.248 8 Gbps的情况下误码率低于10-12。,说明此误码测试系统具有较好的性能。

4 系统验证与设计总结

为了验证系统的性能,分别用该仪器做了自环测试和对1.25 GHz GPON系统突发式光接收模块的误码测试。在自环测试中,发送的数据不通过光路直接送到BMCDR的接收端。测试结果表明,在电信号信道中误码测试系统自身不会误码。在对1.25 GHz GPON系统突发式光接收模块测试过程中,采用两个步骤的测试。步骤1中,按图1连接误码测试系统,两路数据包信号0UN#1和0UN#2都不经过可变光衰减器的衰减,经光合路器合路后的光信号中所有包信号幅值一致,用以验证误码测试系统光路中是否产生误码,实验结果同样验证了误码测试系统自身不会产生误码。步骤2中,对一路数据包信号进行不同幅度的衰减,使光合路器输出的光信号存在幅值的跳变,并在两路数据包信号存在不同幅值跳变的情况下,分别测试突发式光接收模块的误码性能。试验中使用的被测突发式光接收模块强包弱包幅度相差20 dB,保护时间为32位,速率为1.248 8 Gbps的情况下误码率低于10-12。,说明此误码测试系统具有较好的性能。

举报

举报

举报

举报

举报

举报

举报

举报