3 FPGA中实现IP保护

在EDA软件生成了用于配置FPGA的bit-stream后,将bit-stream加载到FPGA中,就可以完成对FPGA的编程,FPGA实现设计者期望的功能。FPGA分为非易失性(Don—volatile)和易失性(volatile)两种,前者包括基于反熔丝技术和Flash技术,后者主要是基于SRAM技术。对于基于SRAM的FPGA,因为其配置信息在掉电之后就会丢失,因此一般需要用PROM存储FPGA的配置信息,以使FPGA在重新加电后能够再次根据这些信息进行配置。FPGA的配置信息就是设计在FPGA上的最终实现,因此需要相应的技术手段来保护这些配置信息。

因此FPGA的bit-stream是二进制信息,它是依赖于设计本身和具体的FPGA结构。一般来说,bit-stream的生成工具都是由FPGA的生产商提供。FPGA的生产商虽然会给出一些bit-stream生成工具的使用信息,但一般都不会公开FPGA的bit-stream编码格式。由于不知道FPGA的bit-stream文件格式,目前尚未发现对FPGA的编程bit-stream文件成功实现逆向工程,所以绝大多数的FPGA使用者都不考虑FPGA中的设计会被破解。

虽然bit-stream文件难以被逆向工程方法破解,但如果这些bit-stream被复制,利用这些bit-stream,再使用同样的FPGA,竞争对手就可以生产同样产品。也这是说,设计还是有可能被盗窃。因此,需要相应的安全机制来防止bit-stream被复制。针对基于SRAM的FPGA,下面讨论两种防范机制。

3.1 一次加载

保证FPGA的编程bit-stream文件安全的一种简单办法就是在安全环境下对FPGA编程后,不再向FPGA配置任何器件,而是对FPGA持续供电。因为所有的可编程逻辑设备都具有保密设置,可阻止从FPGA中读取编程bit-stream文件,而且编程bit-stream文件也不会暴露在器件之外,这种方法既能够使FPGA的设计不被偷窃,也不被篡改。这种保护机制的安全级别与基于反熔丝技术或者其他的非易失性的FPGA相似,但是这种方法的缺点是需要对系统持续供电。

3.2 bit-stream加密

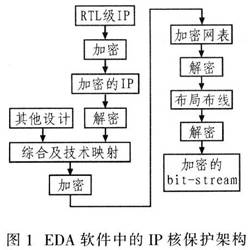

Bit-stream加密技术是对FPGA的编程bit-stream文件加密处理,加密过程是EDA软件的最后一个处理步骤,如图1所示。加密后的bit-stream存储在FPGA的配置器件中,在配置FPGA器件前,要先把加密的bit-stream写入FPGA中,然后进行解密,再用解密后的bit-stream对FPGA进行配置。这一方法既增加对bit-stream文件逆向工程的难度,又阻止编程文件被非法复制。加密采用对称密钥加密算法,密钥由设计者指定。设计者需要将密钥存储到FPGA,FPGA中的解密功能模块可以用这一密钥来对bit-stream解密。

如果最终生成的bit-stream文件是加密的,FPGA就需有一个专用的片上解密器和专用的密码存储器。为了使FPGA既能支持加密的bit-stream,又能支持未加密的bit-stream,bit-stream文件包含有未加密的指令,这些指令可用于启动和解密配置数据。如果bit-stream是加密的,FPGA在真正编程配置前,需要先用存储的密钥对其解密。这样,在FPGA使用过程中,虽然攻击者很容易从配置器件和FPGA的连接线路上获取bit-stream,但是因为这些bit-stream是加密的,即使把这些bit-stream配置到同样的FPGA上,但由于不知道解密的密钥,FPGA也无法对其解密,从而无法配置FPGA。使用这种保护方法,攻击者不知道密钥就无法复制FPGA中的设计。

攻击者可能转而试图从FPGA中盗取密钥。在FPGA中,密钥可存储在RAM中,通过芯片上的一个电池为其供电。如果切断电源,则存储信息即密钥丢失。为了窃取密钥,攻击者需要打开FPGA的封装,打磨掉多个金属层,然后用扫描电子显微镜(SEM)扫描表示密钥的数据位。在进行这些操作的同时,还必须保持对存储密钥的存储器供电。显然这种攻击是难以实现的。

此外,还可以在FPGA内部设计一些逻辑来限制对配置和密钥的访问。例如:当载入一个加密的bit—stream文件时,只能进行单独的、整个芯片的配置;在加载了加密的配置流后,就不允许再读取其中信息;试图读取或写入密钥就会清除所有的密钥和所有的配置数据;解密后的bit-stream在用于配置操作前,必须要通过数据的完整性检验。通过这些限制,使得攻击者无法读取解密后的bit-stream,也无法获得FPGA存储的密钥,从而阻止攻击者复制FPGA中的设计。

4 结语

随着电路设计规模的不断扩大,越来越多的设计者开始应用IP核来提高设计速度和系统可靠性。提出在EDA工具中加入保护机制,防止IP核被窃取,以及在FPGA中加入保护机制防止最终在FPGA上实现的设计被非法复制。这种机制的实现前提条件是要求FPGA的生产商和EDA工具的开发商都是可信的。如何在两者不可信的情况下实现IP核保护,还需进一步研究。

http://article.ednchina.com/PLDFPGA/EDA_software_FPGA_IP_nuclear_protection1.htm

3 FPGA中实现IP保护

在EDA软件生成了用于配置FPGA的bit-stream后,将bit-stream加载到FPGA中,就可以完成对FPGA的编程,FPGA实现设计者期望的功能。FPGA分为非易失性(Don—volatile)和易失性(volatile)两种,前者包括基于反熔丝技术和Flash技术,后者主要是基于SRAM技术。对于基于SRAM的FPGA,因为其配置信息在掉电之后就会丢失,因此一般需要用PROM存储FPGA的配置信息,以使FPGA在重新加电后能够再次根据这些信息进行配置。FPGA的配置信息就是设计在FPGA上的最终实现,因此需要相应的技术手段来保护这些配置信息。

因此FPGA的bit-stream是二进制信息,它是依赖于设计本身和具体的FPGA结构。一般来说,bit-stream的生成工具都是由FPGA的生产商提供。FPGA的生产商虽然会给出一些bit-stream生成工具的使用信息,但一般都不会公开FPGA的bit-stream编码格式。由于不知道FPGA的bit-stream文件格式,目前尚未发现对FPGA的编程bit-stream文件成功实现逆向工程,所以绝大多数的FPGA使用者都不考虑FPGA中的设计会被破解。

虽然bit-stream文件难以被逆向工程方法破解,但如果这些bit-stream被复制,利用这些bit-stream,再使用同样的FPGA,竞争对手就可以生产同样产品。也这是说,设计还是有可能被盗窃。因此,需要相应的安全机制来防止bit-stream被复制。针对基于SRAM的FPGA,下面讨论两种防范机制。

3.1 一次加载

保证FPGA的编程bit-stream文件安全的一种简单办法就是在安全环境下对FPGA编程后,不再向FPGA配置任何器件,而是对FPGA持续供电。因为所有的可编程逻辑设备都具有保密设置,可阻止从FPGA中读取编程bit-stream文件,而且编程bit-stream文件也不会暴露在器件之外,这种方法既能够使FPGA的设计不被偷窃,也不被篡改。这种保护机制的安全级别与基于反熔丝技术或者其他的非易失性的FPGA相似,但是这种方法的缺点是需要对系统持续供电。

3.2 bit-stream加密

Bit-stream加密技术是对FPGA的编程bit-stream文件加密处理,加密过程是EDA软件的最后一个处理步骤,如图1所示。加密后的bit-stream存储在FPGA的配置器件中,在配置FPGA器件前,要先把加密的bit-stream写入FPGA中,然后进行解密,再用解密后的bit-stream对FPGA进行配置。这一方法既增加对bit-stream文件逆向工程的难度,又阻止编程文件被非法复制。加密采用对称密钥加密算法,密钥由设计者指定。设计者需要将密钥存储到FPGA,FPGA中的解密功能模块可以用这一密钥来对bit-stream解密。

如果最终生成的bit-stream文件是加密的,FPGA就需有一个专用的片上解密器和专用的密码存储器。为了使FPGA既能支持加密的bit-stream,又能支持未加密的bit-stream,bit-stream文件包含有未加密的指令,这些指令可用于启动和解密配置数据。如果bit-stream是加密的,FPGA在真正编程配置前,需要先用存储的密钥对其解密。这样,在FPGA使用过程中,虽然攻击者很容易从配置器件和FPGA的连接线路上获取bit-stream,但是因为这些bit-stream是加密的,即使把这些bit-stream配置到同样的FPGA上,但由于不知道解密的密钥,FPGA也无法对其解密,从而无法配置FPGA。使用这种保护方法,攻击者不知道密钥就无法复制FPGA中的设计。

攻击者可能转而试图从FPGA中盗取密钥。在FPGA中,密钥可存储在RAM中,通过芯片上的一个电池为其供电。如果切断电源,则存储信息即密钥丢失。为了窃取密钥,攻击者需要打开FPGA的封装,打磨掉多个金属层,然后用扫描电子显微镜(SEM)扫描表示密钥的数据位。在进行这些操作的同时,还必须保持对存储密钥的存储器供电。显然这种攻击是难以实现的。

此外,还可以在FPGA内部设计一些逻辑来限制对配置和密钥的访问。例如:当载入一个加密的bit—stream文件时,只能进行单独的、整个芯片的配置;在加载了加密的配置流后,就不允许再读取其中信息;试图读取或写入密钥就会清除所有的密钥和所有的配置数据;解密后的bit-stream在用于配置操作前,必须要通过数据的完整性检验。通过这些限制,使得攻击者无法读取解密后的bit-stream,也无法获得FPGA存储的密钥,从而阻止攻击者复制FPGA中的设计。

4 结语

随着电路设计规模的不断扩大,越来越多的设计者开始应用IP核来提高设计速度和系统可靠性。提出在EDA工具中加入保护机制,防止IP核被窃取,以及在FPGA中加入保护机制防止最终在FPGA上实现的设计被非法复制。这种机制的实现前提条件是要求FPGA的生产商和EDA工具的开发商都是可信的。如何在两者不可信的情况下实现IP核保护,还需进一步研究。

http://article.ednchina.com/PLDFPGA/EDA_software_FPGA_IP_nuclear_protection1.htm

举报

举报

举报

举报

举报

举报