2 系统集成

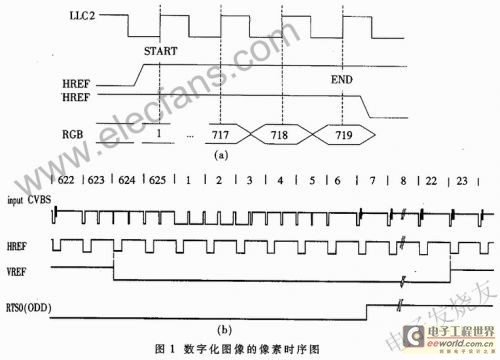

综上所述,完整的电子稳像系统结构如图8所示。摄像头输入的信号采用PAL制式,经过视频处理接口后形成RGB565格式的数字视频信号和控制信息;帧存控制器作为整个平台的核心,在将数据写入帧存储器的同时,对数字化的图像信息进行去隔行处理,再将数据读出送往VGA控制器时进行放大变换。VGA控制器则负责将数据按照VGA标准时序送往显示器上。

在该平台上实现了文献中K0等人提出的一种最简单的基本位平面的电子稳像算法,对于8位的灰度图像,可以表示为:利用第4层进行运算,其依据是在多帧图像进行BPM运算后发现,该层的误差结果较平滑。然而,K0的BMP-b4算法在不同的图像序列和信噪比的情况下,并不能总得到一个最优解;在某些情况下,b4、b5或b6会得到更好的结果。

目前资料显示电子稳像技术作为近年新兴技术还处于试验研究阶段,因其适用范围广阔而展现了乐观的研发前景。

2 系统集成

综上所述,完整的电子稳像系统结构如图8所示。摄像头输入的信号采用PAL制式,经过视频处理接口后形成RGB565格式的数字视频信号和控制信息;帧存控制器作为整个平台的核心,在将数据写入帧存储器的同时,对数字化的图像信息进行去隔行处理,再将数据读出送往VGA控制器时进行放大变换。VGA控制器则负责将数据按照VGA标准时序送往显示器上。

在该平台上实现了文献中K0等人提出的一种最简单的基本位平面的电子稳像算法,对于8位的灰度图像,可以表示为:利用第4层进行运算,其依据是在多帧图像进行BPM运算后发现,该层的误差结果较平滑。然而,K0的BMP-b4算法在不同的图像序列和信噪比的情况下,并不能总得到一个最优解;在某些情况下,b4、b5或b6会得到更好的结果。

目前资料显示电子稳像技术作为近年新兴技术还处于试验研究阶段,因其适用范围广阔而展现了乐观的研发前景。

举报

举报

举报

举报

举报

举报

举报

举报